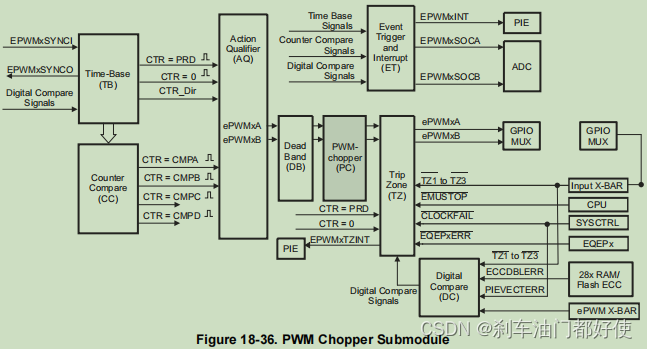

下图是PC子模块和其他子模块的联系图。可以看出,PC接收DB的输出,然后处理后给到TZ。

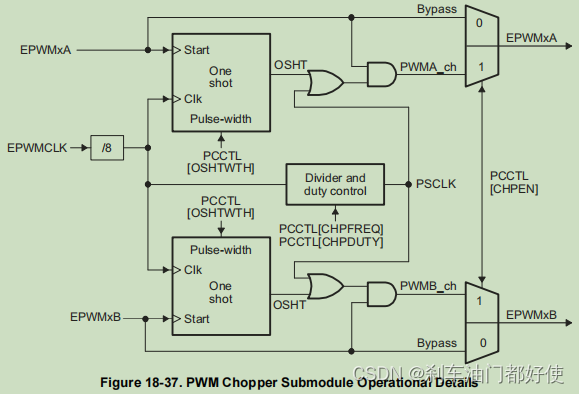

下图是PC子模块的内部框图。可以看到:

1)PC子模块功能可以被bypass;

2)one shot和divider的时钟是epwm时钟的8分频;

3)PC子模块功能输出是EPWMxA & (PSCLK | OSHT)。

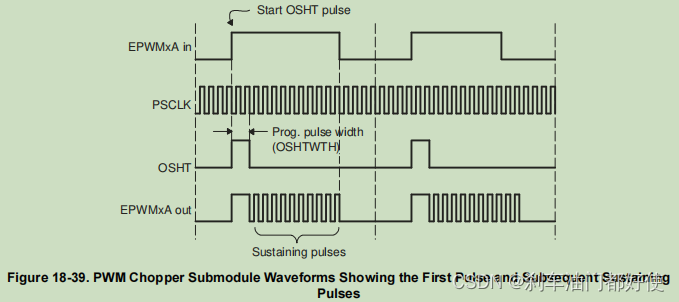

下图是波形情况。

其中OSHTWTH和PSCLK的频率和占空比是可调的,具体可查看寄存器描述。

疑问:

PC子模块的应用场景是什么呢?

参考文档:

TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (Rev. G)

![[论文笔记] Pai-megatron Qwen1.5-14B-CT 后预训练 踩坑记录](https://img-blog.csdnimg.cn/direct/13ad315ebbbd4986a3331d2fd36fc4fd.png)