4.3 批处理验证实现

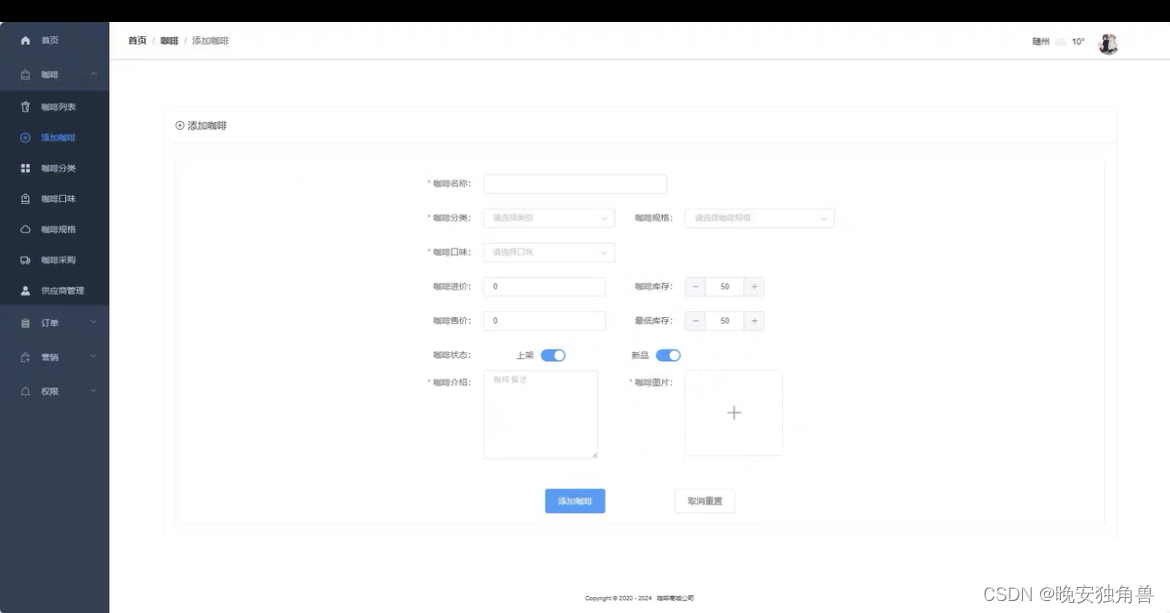

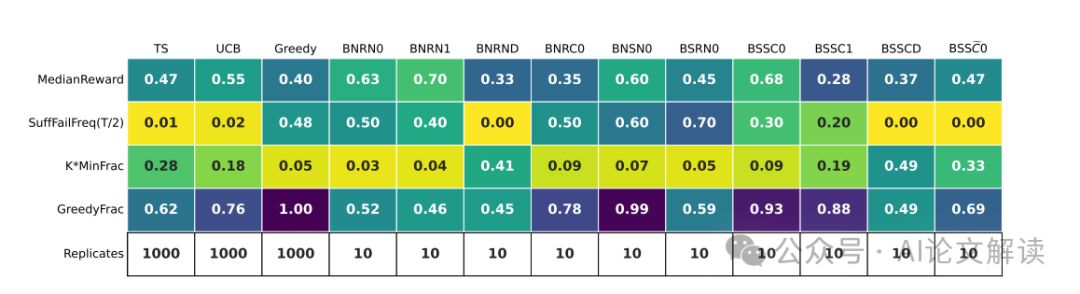

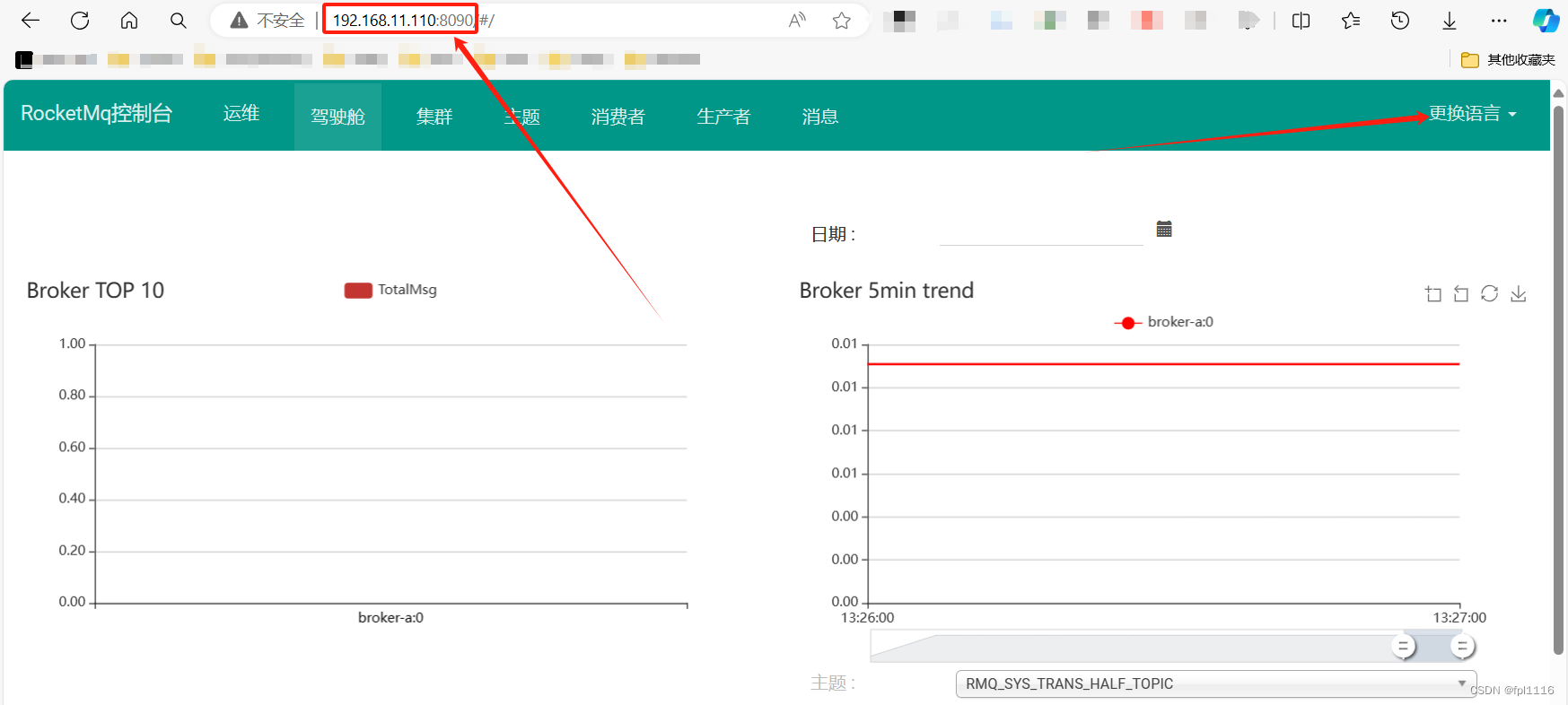

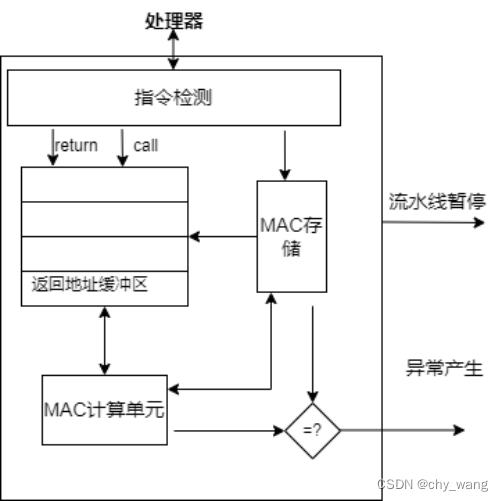

批处理验证是为了进一步降低硬件资源消耗和降低系统功耗提出的二级片内硬件堆栈的另一种实现方法,批处理验证的硬件结构图如图4.7所示,也由指令检测单元、返回地址缓冲区、MAC计算单元、MAC存储单元组成。

图4.7 批处理验证硬件框图

批处理验证与延迟验证相同都在处理器相同的位置截取指令,采用相同的方式对保存或调用返回地址的指令进行检测,在流水线中截取相同的信号获得返回地址和保存返回地址到内存堆栈中,其端口信号与延迟验证相同,如表4.2所示。在批处理验证中当检测到返回地址调用或保存指令后,对RAB中的返回地址进行相应的操作,如3.4节所述,在条件满足的情况下会将RAB中的返回地址送入MAC计算单元进行计算,之后再将MAC保存到MAC存储单元中,由于RAB中的返回地址只生成一个MAC,所以MAC存储单元可以做的更小以节省硬件资源。

在批处理验证中,RAB只需要保存最近的返回地址以及一个硬件指针front。批处理验证中MAC计算单元同样采用AES对称加密算法,同时采用了门控时钟和最新MAC存储等方法进行了优化,进一步提高系统性能。

4.3.1 消息验证码计算单元

在批处理验证中同时输入AES多个返回地址进行计算,同样在输入的返回地址位宽小于AES输入数据位宽时使用比特位进行填充。

在进行MAC验证时,通常验证的返回地址是上一次保存到内存堆栈中的返回地址,即MAC验证通常紧跟在MAC计算更新之后,这种情况通常出现在叶函数中[4]。因此在MAC计算单元中保存最新输入AES进行计算的返回地址,在下一次计算返回地址的MAC时,如果计算的返回地址与上一次相同,则不需要再次进行计算,可以直接使用之前已经计算出的MAC。在MAC单元中记录最新AES输入数据的程序为(RAB大小为4):

assign aes_data = {rab_ra[3], rab_ra[2], rab_ra[1], ra_lw};

// 当需要计算MAC时,保存此时的返回地址

if((sw_ra_i == 2’b01) & (front== 0))

aes_data_reg <= aes_data;

在需要验证时,先判断需要计算MAC的返回地址与之前更新的返回地址是否相同:

assign aes_same = (aes_data_reg == aes_data);

在保存或调用返回地址后,如果此时front为0并且aes_same为0,RAB中的返回地址为一个新的块,将开始计算该块的MAC。

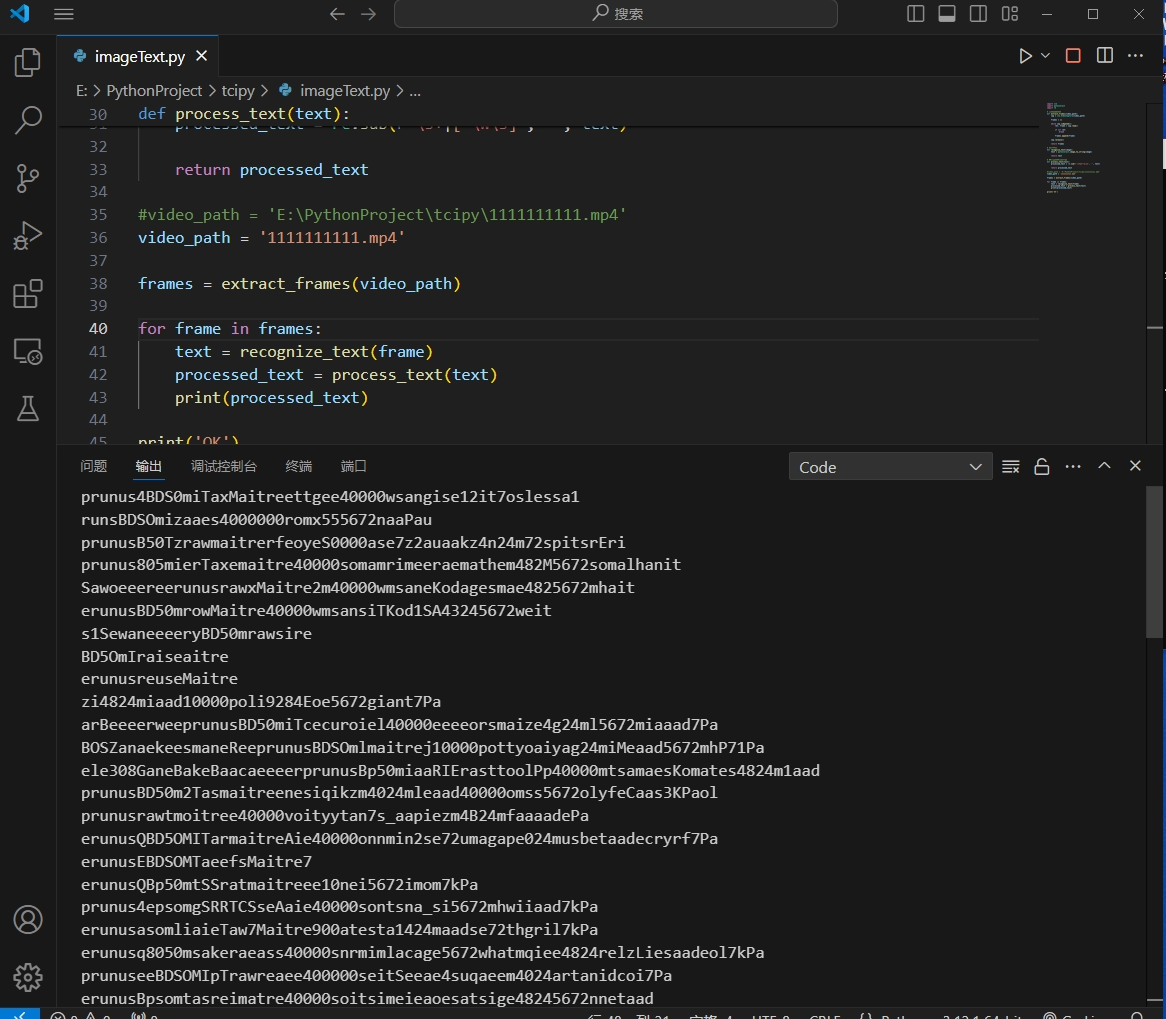

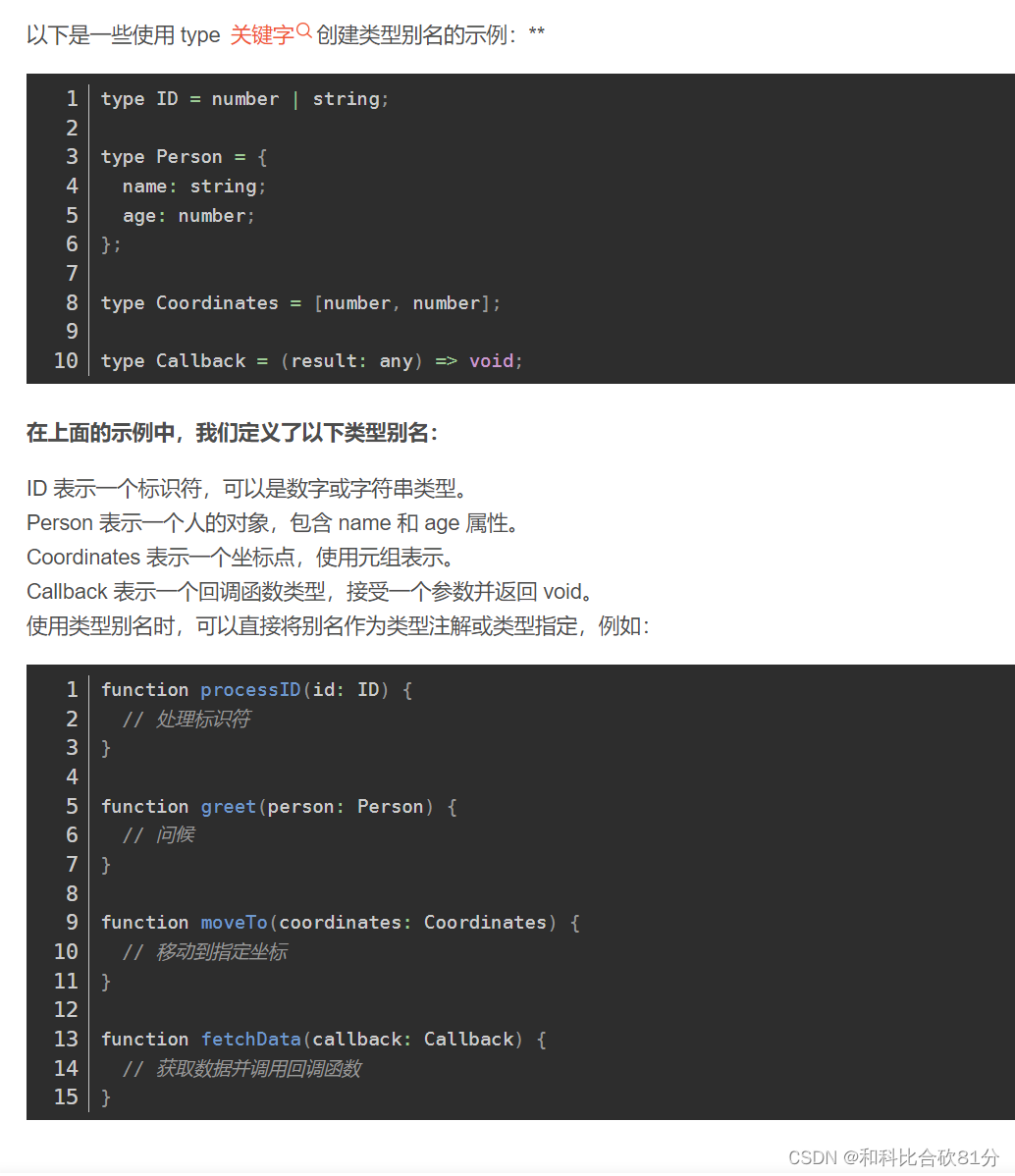

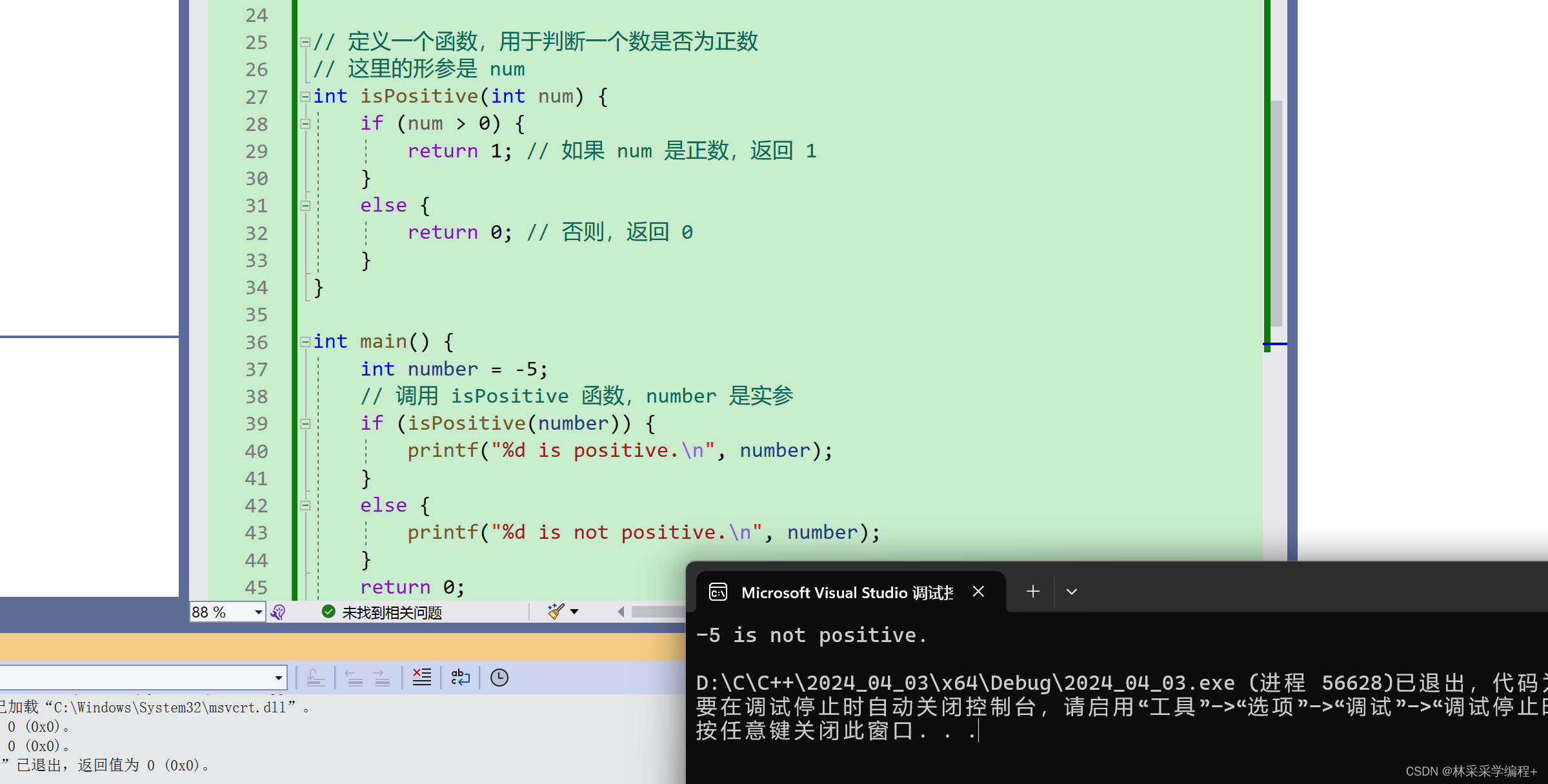

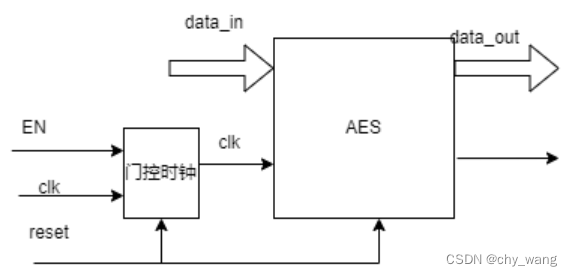

批处理验证只有RAB中的返回地址为一个新的块并且aes_same为0的情况下AES才会进行运算,为此我们在AES中添加门控时钟,只有需要AES进行运算的情况下时钟才使能,在时钟无效的情况下AES没有功耗产生,降低了系统的功耗,原理图如图4.8所示。

图4.8 AES门控时钟

###4.3.2 消息验证码存储单元

在批处理验证中由于多个返回地址生成一个MAC,所以MAC存储单元可以设计的很小以节省硬件资源。与延迟验证相同,使用一个硬件指针mac_pointer作为MAC存储单元中存储下一个MAC的地址,mac_poiner初始时为0指向第一个存储单元。

在MAC存储单元中设置了两个标志位sw_mac和lw_mac,当需要将RAB中返回地址的MAC保存到MAC存储单元时sw_mac被置1,当需要从MAC存储单元中读取相应的MAC时lw_mac被置1。

在系统中需要将返回地址的MAC保存到MAC存储单元时,如果aes_same为1即需要保存的返回地址的MAC与前一次的返回地址相同,则可以直接将已有的MAC保存并将mac_pointer加1。如果aes_same为0并且sw_same为1则当AES模块计算完毕后再将生成的MAC保存到MAC存储单元。在系统需要读取MAC进行验证时,如果此时aes_same为1则直接将MAC存储单元中的“栈顶”的MAC取出与AES中的MAC进行比较判断返回地址是否被篡改;如果aes_same为0且lw_mac为1,则等待AES计算完当前MAC计算完后在读取MAC存储单元中的MAC。

4.3.3 流水线暂停与异常产生

在调用返回地址并且需要进行验证时,如果aes_same为1则不需要重新计算MAC,所以不需要暂停流水线,如果aes_same为0则需要MAC计算单元重新计算MAC。此时需要暂停流水线,定义stall信号为流水线暂停信号:

always @ (posedge clk,negedge rst_n) begin

if(~rst_n)

stall <= 1’b0;

else begin

if((lw_ra_2_i == 2’b10)&(aes_same == 1’b0)&(front == 2’b00))

stall <= 1’b1;

if(aes_done_r == 2’b10)

stall<= 1’b0;

end

end

与延迟验证相同,将该信号作为译码模块中流水线控制信号的一个输入,实现处理器流水线的暂停。

在调用返回地址时,如果此时RAB中的返回地址为一个新的块则需要进行验证,如果aes_same为1则直接将AES模块中的MAC与MAC存储单元中的MAC进行比较,如果aes_same为0则AES模块计算出新的MAC时将计算出的MAC与MAC存储模块中的MAC进行比较,如果不相等则产生异常信号,异常输入到处理器的NMI不可屏蔽中断中,从而阻止恶意程序的执行。

4.4 本章小结

本章主要在玄铁E906 RSIC-V处理器中实现了二级硬件堆栈的两种验证方法。首先介绍了平头哥的开源32位RISC-V处理器玄铁E906,基于这款开源RISC-V处理器,将系统硬件模块划分为指令检测单元、返回地址缓冲区、消息验证码计算单元和消息验证码存储单元,此外还包括异常产生以及流水线暂停处理,分别在硬件中实现两种验证方法并集成到处理器中。