存储系统

- 层次划存储

- 概念图

- 局促性原理

- 分类

- 存储器位置

- 存取方式

- 按内容存储

- 按地址存储

- 工作方式

- 拓展

- 往年真题

- 高速缓存(cache)

- 概念

- 案例解析:求取平均时间

- Cache与主存的地址映射

- 映像

- 往年真题

- 主存编制计算

- 编址

- 大小的求取

- 编址与计算

- 存储单元

- 编址内容

- 总容量求取

- 例题解析:编址与计算

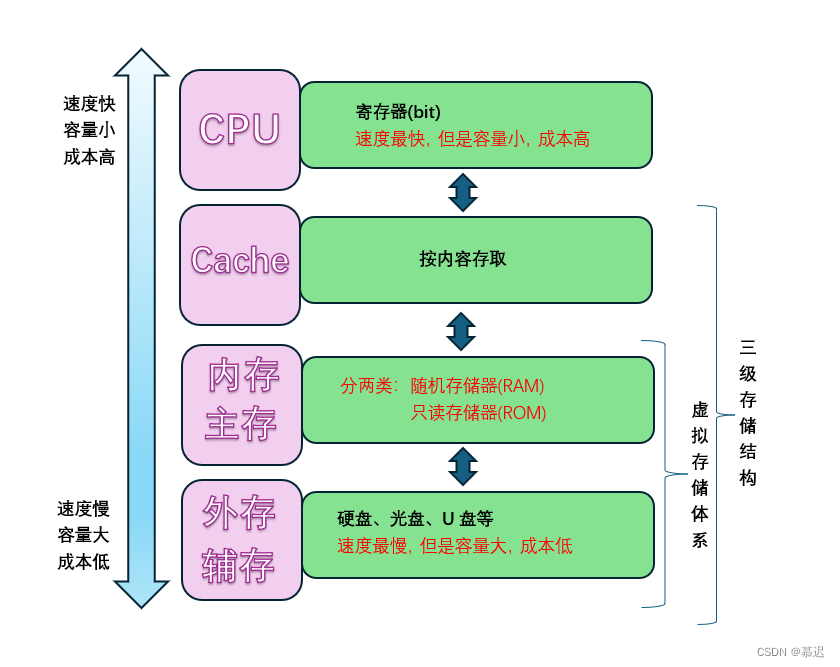

层次划存储

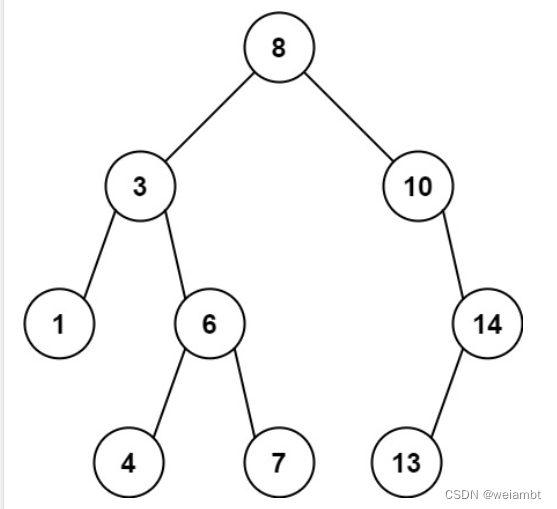

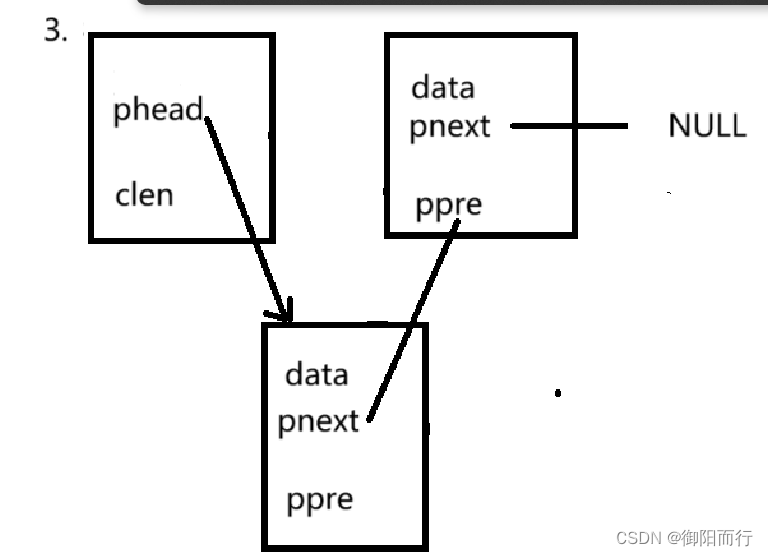

概念图

局促性原理

是层次化存储结构的支撑

- 时间局部性:刚被访问的内容,立即又被访问,一般是循环的体现。

- 空间局部性:刚被访问的内容,临近的空间很快被访问,一般是顺序的体现。

分类

存储器位置

内存&外存

- 计算器内部叫内存也叫主存

- 计算机外部的叫外存也叫辅存

存取方式

按内容存储

- 相联存储器(如:Cache)

按地址存储

- 随机存取存储器(如:内存)

- 顺序存取存储器(如:磁带)

- 直接存取存储器(如:磁盘)

磁盘:包含连个过程:①移绿调度的过程②旋转延迟的过程(顺序)

工作方式

- 随机存取存储器RAM(如内存:DRAM)

RAM:掉电丢失,会丢失数据

DRAM:动态的,会定时刷新,成本稍微低一些,SRAM静态的,不会取刷新,成本稍微高一些

- 只读存储器ROM(如BIOS)

掉电保留,不会丢失数据

拓展

- DRAM:动态随机存取存储器

- SRAM:静态随机存取存储器

- Cache:高速缓存

- EEPROM:电可擦可编程只读存储器

往年真题

CPU访问存储器时,被访问数据一般聚集在一个较小的连续存储区域中。若一个存储单元已被访问,则其邻近的存储单元有可能还要被访问,该特性被称为( C )。

A、数据局部性

B、指令局部性

C、空间局部性

D、时间局部性

备注:只分为:空间和时间,所以A、B是错误的

时间局促性:一定时间内再次被访问,循环的原理

空间局促性:顺序的考察

虚拟存储体系由( A )两级存储器构成。

A、主存-辅存

B、寄存器-Cache

C、寄存器-主存

D、Cache-主存

在微机系统中,BIOS(基本输入输出系统保存在( A )

A、主板上的ROM

B、CPU的寄存器

C、主板上的RAM

D、虚拟存储器

高速缓存(cache)

概念

在计算机的存储系统体系中,Cache是访问速度最快的层次(若有寄存器,则寄存器最快)。

使用Cache改善系统性能的依据是程序的局部性原理。

上节回顾:

- 时间局部性:刚被访问的内容,立即又被访问,一般是循环的体现。

- 空间局部性:刚被访问的内容,临近的空间很快被访问,一般是顺序的体现。

案例解析:求取平均时间

如果以h代表对Cachel的访问命中率,t1表示Cachel的周期时间,t2表示主存储器周期时间,以读操作为例,使用Cache+主存储器的系统的平均周期为t3,则:

t

3

=

h

×

t

1

+

(

1

−

h

)

×

t

2

t3=h×t1+(1-h)×t2

t3=h×t1+(1−h)×t2

其中,(1-h)又称为失效率(未命中率)

- cache一般命中率为90%左右,所以效率是非常高的。

- 失效率为:1-90% = 10%

- 假设

t1(Cache)周期是1ms,t2(主存储器)周期是100毫秒 - 假设只有catch+主存结构,假如读取了100次数据,那么平均时间的求取是:

-

(100*90%)×1ms+10×100ms

-

90×1ms+100×100ms

-

那么平均时间就是:

90 × 1 m s + 10 × 100 m s 100 90×1ms+10×100ms \over 100 10090×1ms+10×100ms -

也就是 概率 数值 概率 \over 数值 数值概率

-

- 平均时间结果为

10.9ms

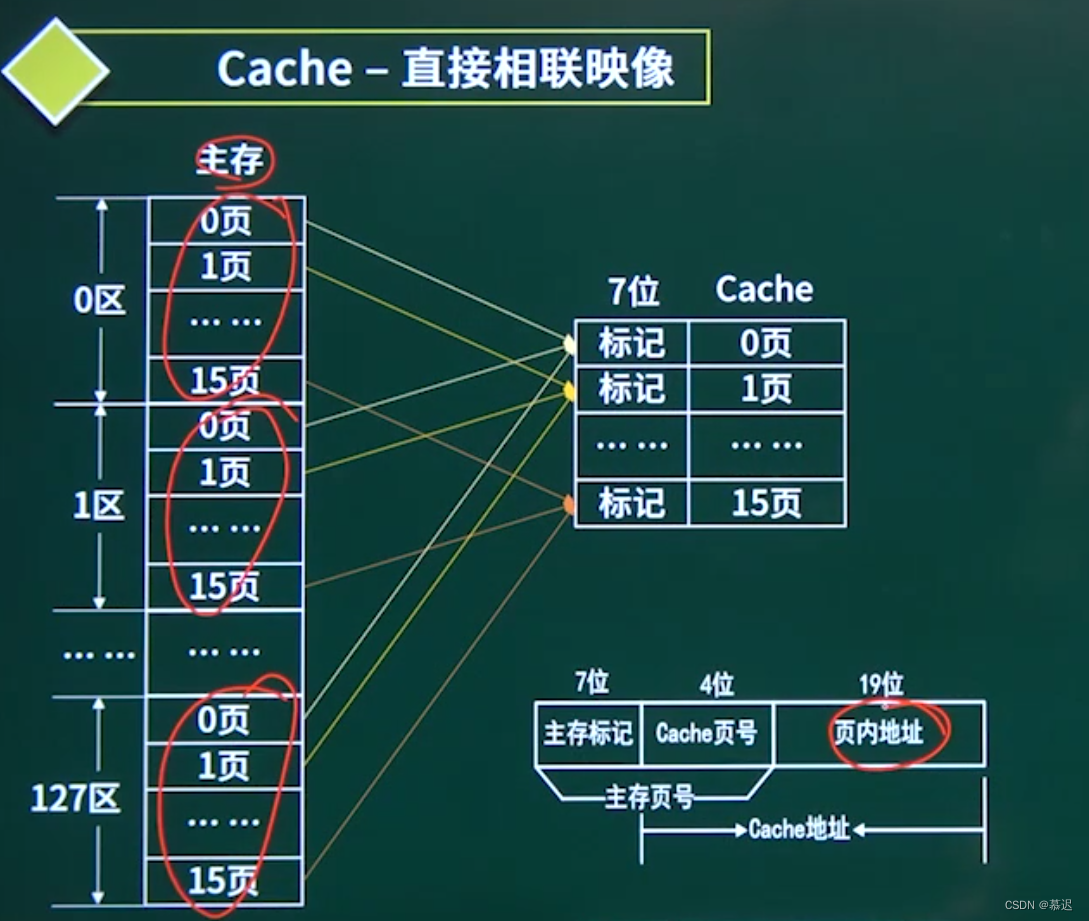

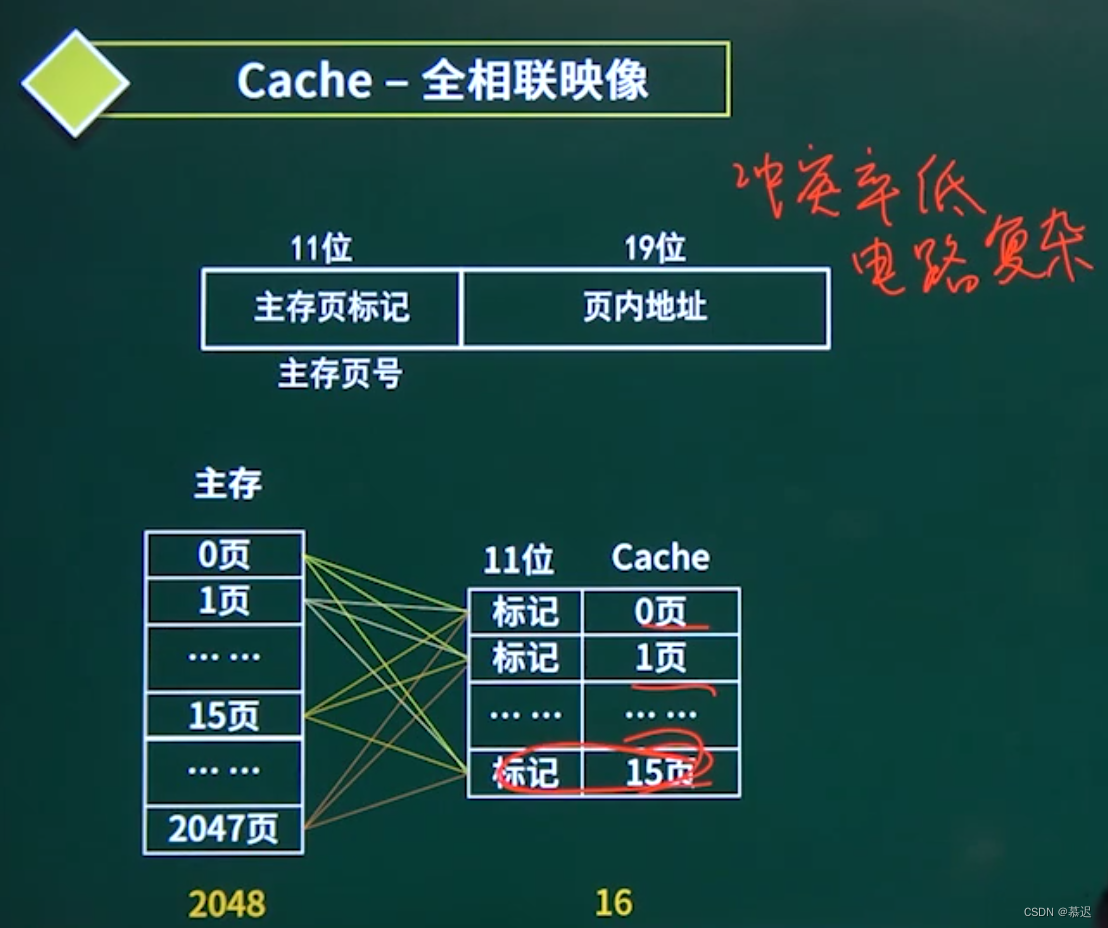

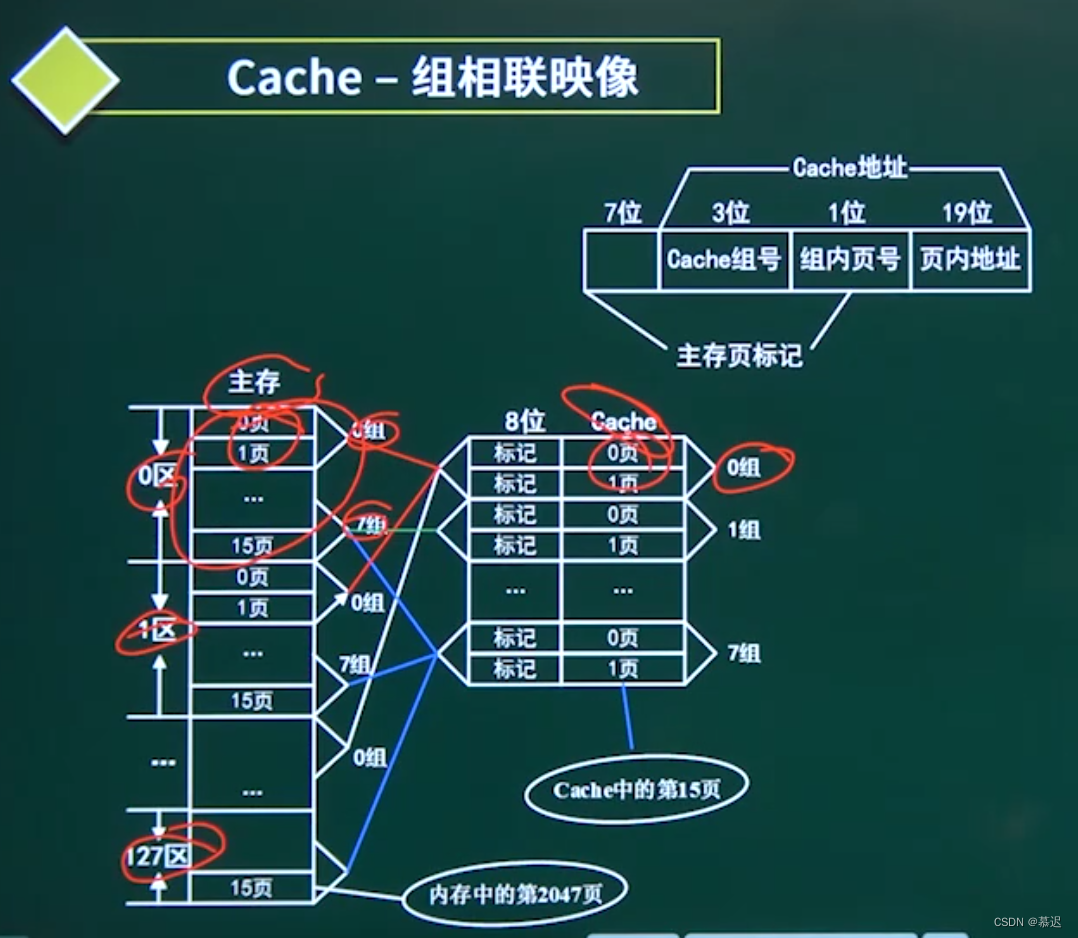

Cache与主存的地址映射

- 直接相联映像:

硬件电路较简单,但冲突率很高。 - 全相联映像:电路难于设计和实现,只适用于小容量的cache,

冲突率较低。 - 组相联映像:直接相联与全相联的

折中。

注: 主存与Cache之间的地址映射由硬件直接完成。

映像

地址映像是将主存与Cache的存储空间划分为若干大小相同的页(或称为块)。

例如,某机的主存容量为1GB,划分为2048页,每页512KB;Cache容量为8MB,划分为16页,每页512KB。

- 直接相联映像

电路简单,冲突率高

- 全相联映像

冲突率低,电路复杂

- 组相联映像

冲突率中,电路复杂度中

- 相联映像对比表格

| 冲突率 | 复杂度 | |

|---|---|---|

| 直接相联映像 | 高 | 简单 |

| 全相联映像 | 低 | 复杂 |

| 组相联映像 | 中 | 折中 |

往年真题

以下关于Cache(高速缓冲存储器)的叙述中,不正确的是( A )。

A、Cache的设置扩大了主存的容量

B、Cache的内容是主存部分内容的拷贝

C、Cache的命中率并不随其容量增大线性地提高

D、Cache位于主存与CPU之间

在程序执行过程中,高速缓存(Cache)与主存间的地址映射由( D )

A、操作系统进行管理

B、存储管理软件进行管理

C、程序员自行安排

D、硬件自动完成

主存与Cache的地址映射方式中,( A )方式可以实现主存任意一块装入Cache中任意位置,只有装满才需要替换。

A、全相联

B、直接映射

C、组相联

D、串并联

主存编制计算

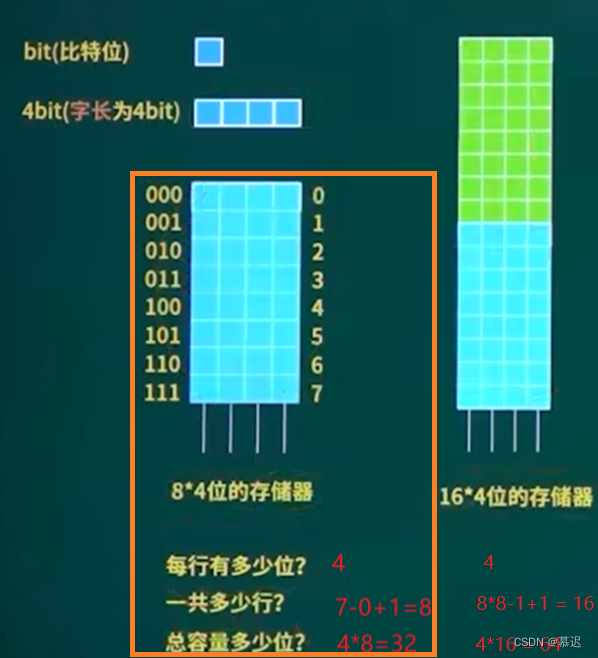

编址

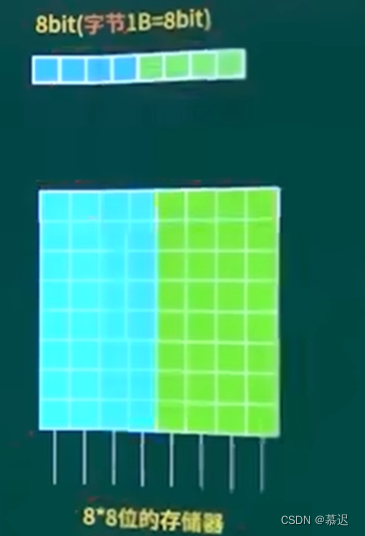

一般字长题目中会给出,这里指定了4个bit,最常见的是16位字长,这样的一组被称为存储单元。

大小的求取

- 不仅可以纵向拼接还可以横行拼接

八位字长我们一般成为字节

编址与计算

存储单元

存储单元大小 = 最大地址-最小地址+1

编址内容

按字编址:存储体的存储单元是字存储单元,即最小寻址单位是一个字

按字节编址:存储体的存储单元是字节存储单元,即最小寻址单位是一个字节。

总容量求取

总容量 = 存储单元个数 * 编址内容

一般总容量都是比较大的,所以我们都是小芯片进行的拼装,所以要根据总容量求出总片数。

根据存储器所要求的容量和选定的存储芯片的容量,就可以计算出所需芯片的总数,即:

总片数

=

总容量

每片的容量

总片数 = {总容量 \over 每片的容量}

总片数=每片的容量总容量

- 考试形式:

给出地址范围,给出编制内容,求出总容量

或者再给芯片容量,求出总片数

再或者给片数,求出芯片容量

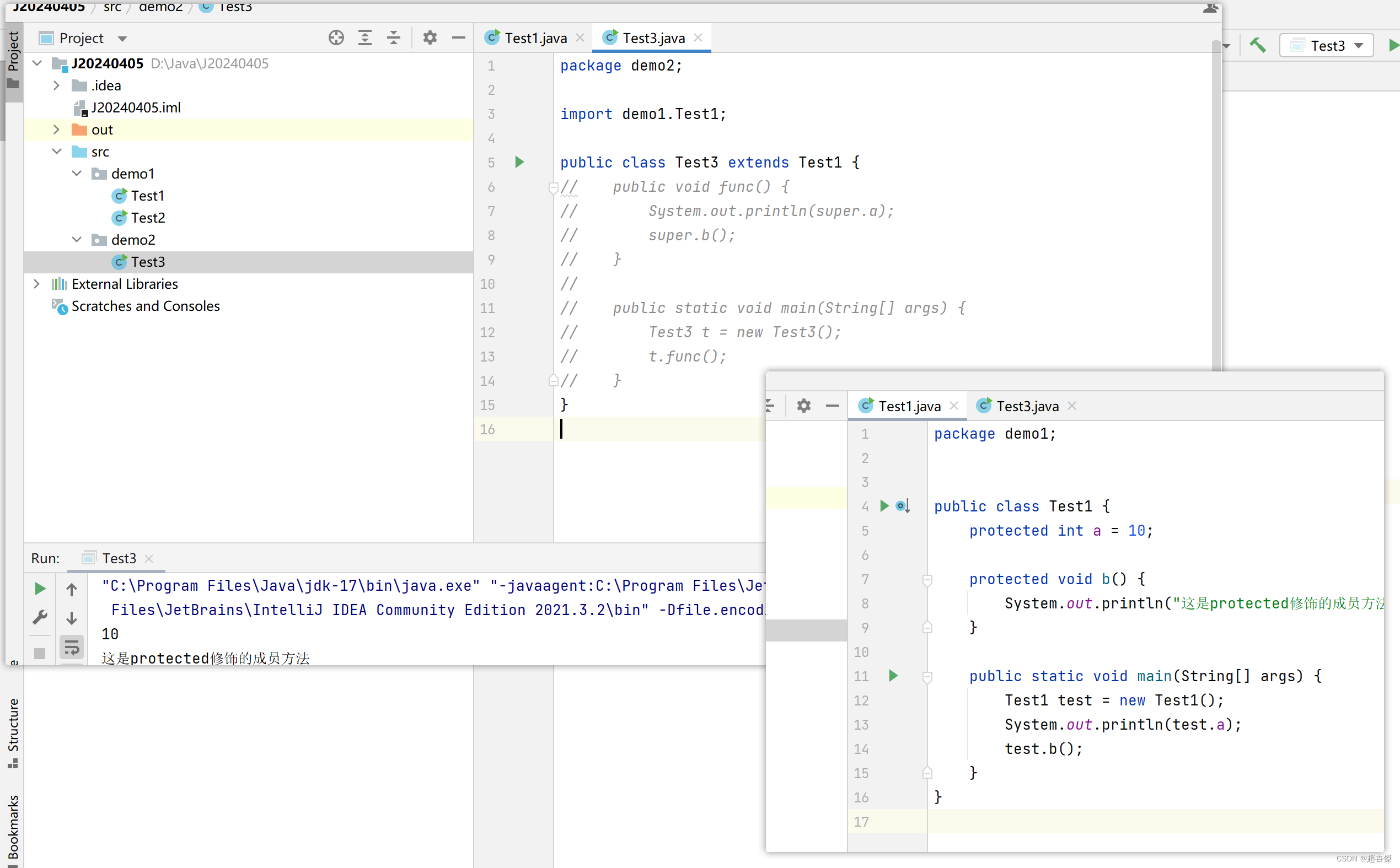

例题解析:编址与计算

内存按字节编址,地址从A0000H到CFFFFH的内存,共有( D )字节,若用存储容量为64K×8tit的存储器芯片构成该内存空间,至少需要( B )片。

A、80KB B、96KB

C、160KB D、192KB

A、2 B、3

c、5 D、8

注意:字节编制:字节一般用大写字母B来表示,占用8bit

注意:H是16进制

![[C#]OpenCvSharp使用帧差法或者三帧差法检测移动物体](https://img-blog.csdnimg.cn/direct/fcdbca9fb19848e4afe4d34a102b6544.png)