目录

一、前言

二、分析报告

2.1 时钟分析

2.1.1 时钟报告

2.1.2 时钟网络报告

2.1.3 时钟利用率报告

2.1.4 跨时钟域报告

2.2 时序分析

2.3 约束分析

2.4 资源分析

2.5 逻辑级数分析

2.6 扇出分析

2.7 进位链分析

2.8 控制集分析

2.9 复杂度分析

2.10 pipeline分析

2.11 时序分析配置报告

2.12 参数配置报告

三、参考资料

一、前言

在大型工程设计中,为了设计时序收敛,往往需要对初步运行的结果进行调试,调试的很重要的依据就是各种报告的分析,下面将介绍一些常用的分析报告,演示的器件为xcku3p-ffvb676-2-i

二、分析报告

2.1 时钟分析

时钟分析主要包含四部分:时钟,时钟网络,时钟利用率,跨时钟域

2.1.1 时钟报告

Tcl console使用命令report_clocks可以报告设计中使用的时钟信息(名称,周期,波形,属性,来源),包括主时钟和生成时钟

report_clocks "clk_name"命令可以对指定名称的时钟进行报告,此时示例时钟名称为clk1

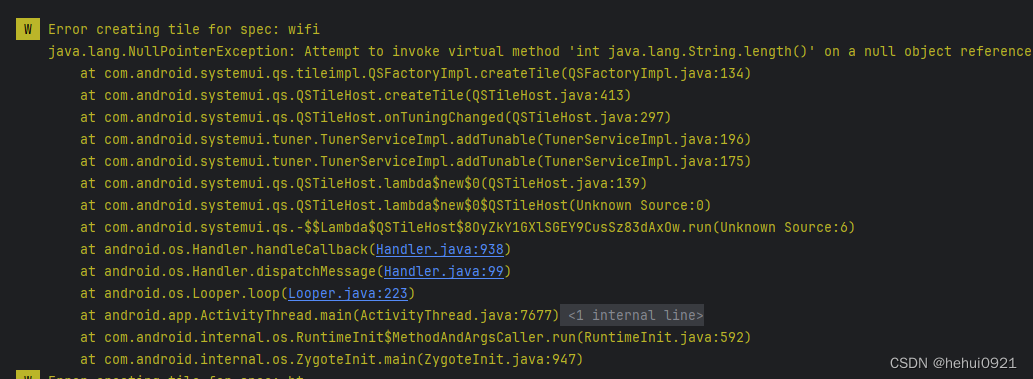

2.1.2 时钟网络报告

时钟网络报告使用界面的report_clock_networks生成,也可以tcl console窗口执行report_clock_networks命令生成,报告与时钟周期约束无关,为物理存在的,通过时钟网络报告可以查看时钟是否遗漏约束以及时钟驱动的load的信息。

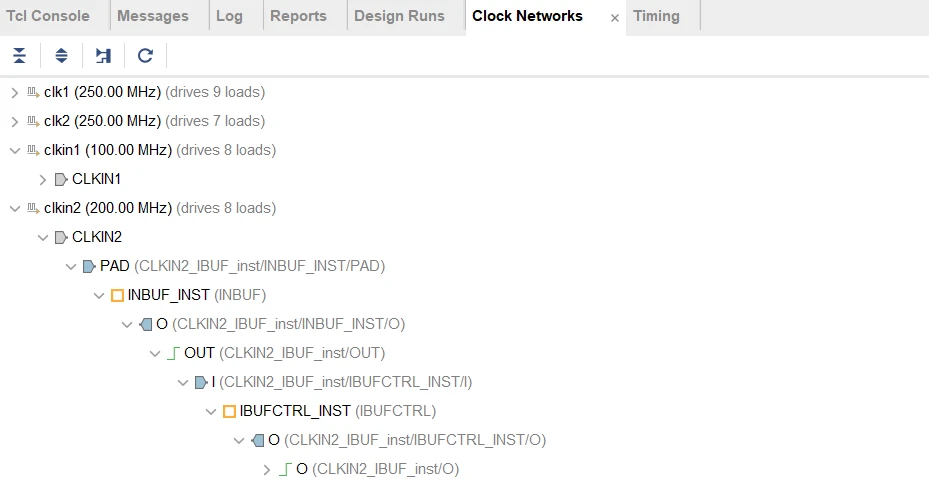

2.1.3 时钟利用率报告

使用命令report_clock_utilization -name utilizer即会打开一个名称为utilizer的窗口,显示设计的时钟资源利用率,内容为时钟原语利用率,全局时钟资源利用率,全局时钟资源使用细节,本地时钟细节,时钟区域(时钟资源按区域分布的情况),全局时钟

2.1.4 跨时钟域报告

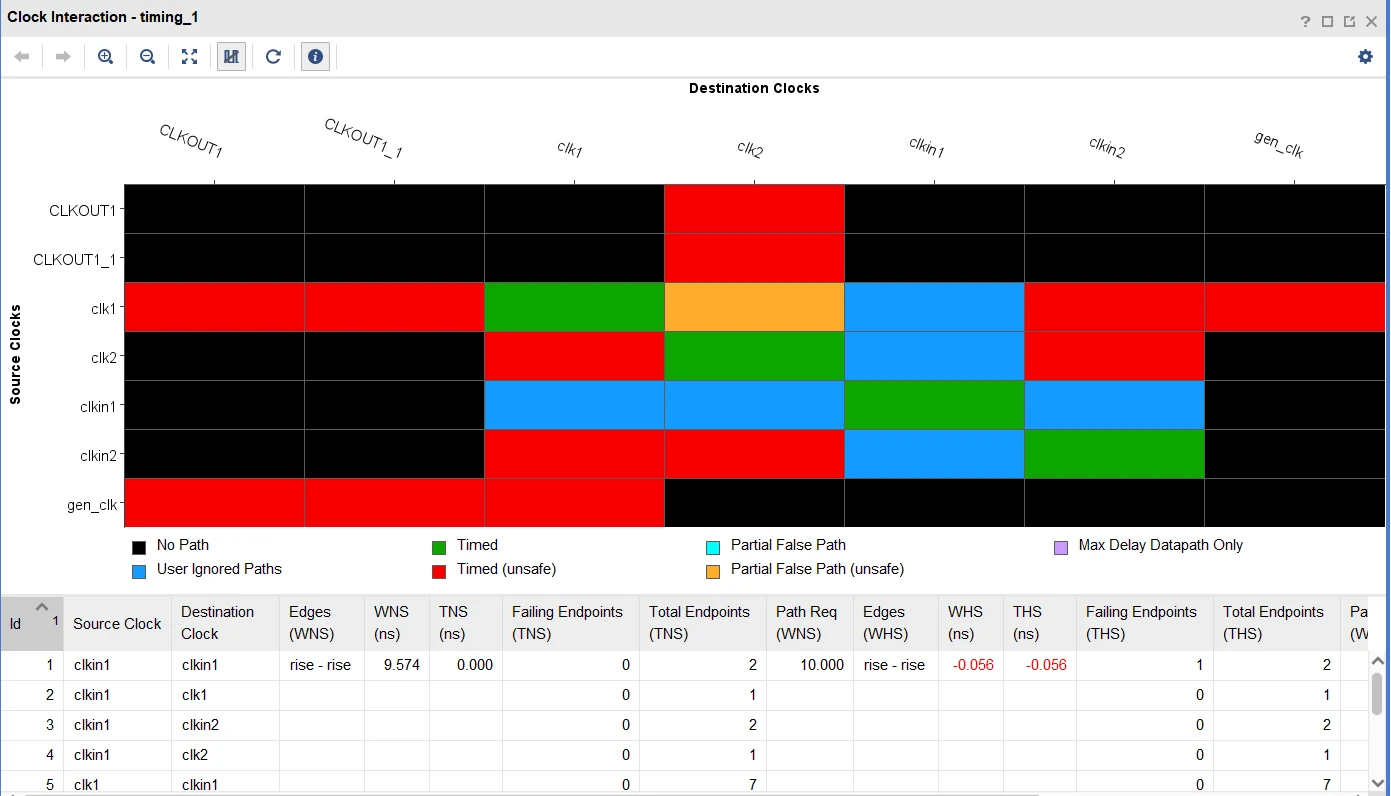

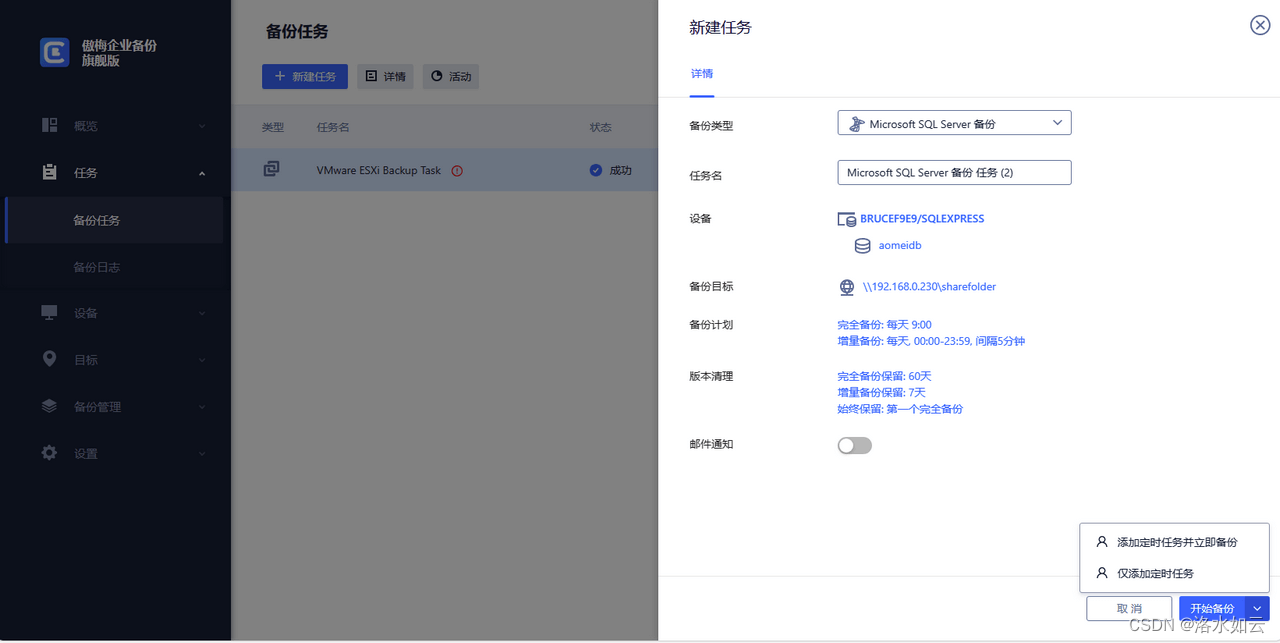

通过左侧综合与实现栏中的report_clock_interaction或tcl console输入report_clock_interaction都可进行源时钟和目标时钟关系分析,分析结果如下图

各颜色块名称含义如下

No path(黑色):指定的两个时钟间无时序路径

Timed(绿色):源时钟和目的时钟有同步关系,该路径的时序是安全的

User Ignored path(蓝色):在该源时钟与目的时钟的路径上,用户设置了false path或时钟组约束,

Partial False Path (淡蓝色):用户对源时钟和目的时钟间的部分路径设置false path约束,并且目的时钟与源时钟是同步时钟

Timed (Unsafe) (红色):源时钟和目的时钟是异步关系,它们没有共同的主时钟

Partial False Path (Unsafe) (橘黄色):源时钟和目的时钟至少有一条路径设置了false path约束

Max Delay Datapath Only (灰色):源时钟和目的时钟间的路径都设置了set_max_delay -datapath_only约束。

2.2 时序分析

时序分析主要是通过report_timing或report_timing_summary产生,后者是生成时序总结报告,report_timing更多的是用于指定路径进行时序分析。同时report_timing还可将时序报告以指定格式输出,可指定为.rpx和.rpt,其中.rpx是和网表文件dcp同时打开。

关于report_timing_summary可参见文章https://blog.csdn.net/zyp626/article/details/136436191?spm=1001.2014.3001.5501

2.3 约束分析

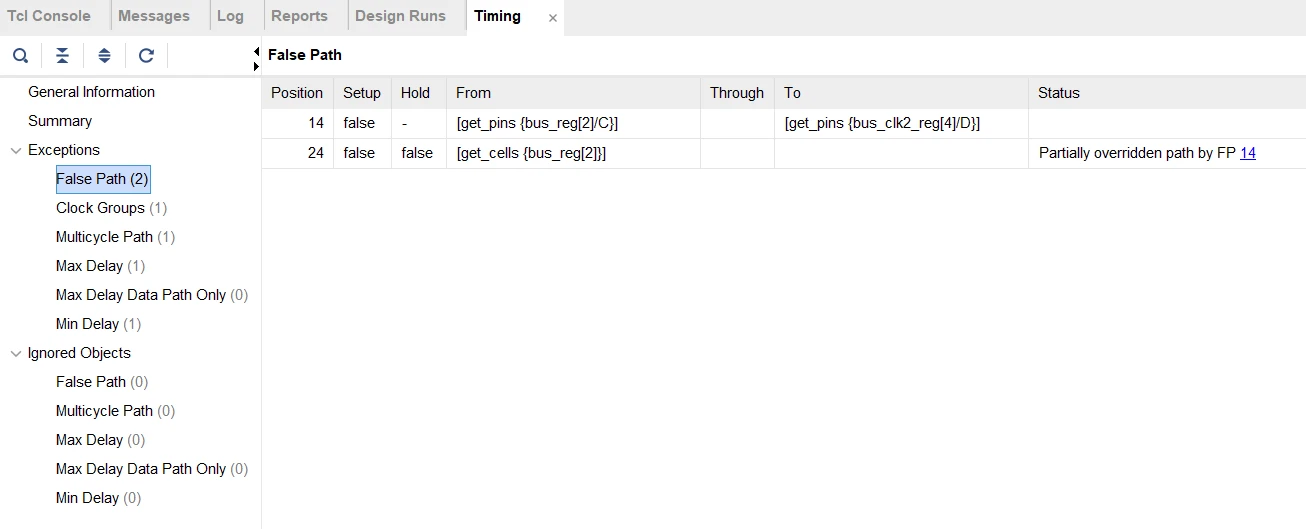

在时序例外约束中,如set_clock_groups,set_false_path,set_max_path,set_min_path,set_multicycle_path中,存在着优先级关系,一步小心就被覆盖,vivado使用report_exceptions来检查是否存在覆盖或合并的情况,可通过菜单栏路径“Reports->Timing->Report Exceptions”运行,也可tcl console窗口执行report_exceptions -name exception运行。

如下图,exceptions中显示了用户设置的约束,右侧为约束的实际情况,在position为24的status可以看到,该条约束已被第14条约束所覆盖。

在status列看到有缩写FP表示set_false_path,同时可能出现其他缩写,CG(set_clock_groups),MXD(set_max_path),MND(set_min_path),MCP(set_multicycle_path),DPO(set_max_path -datapath_only)。

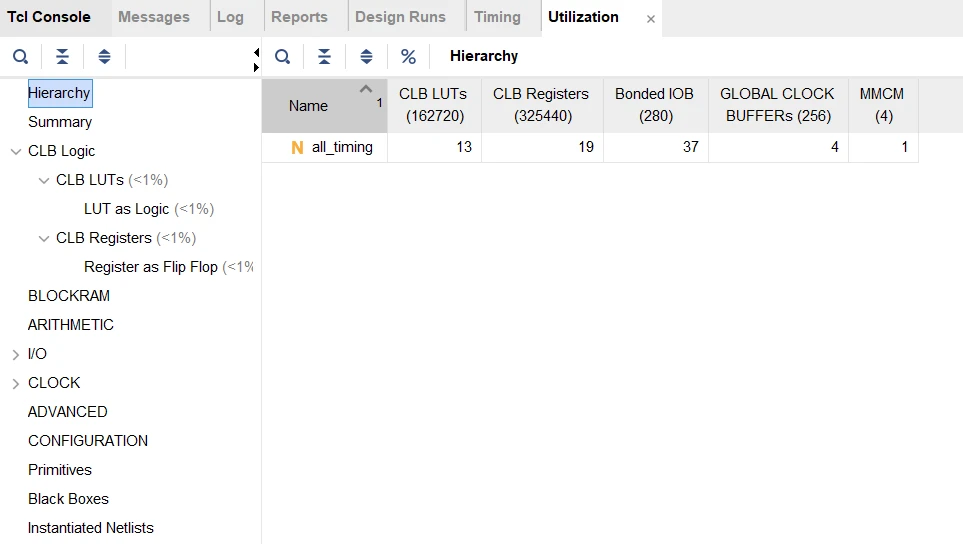

2.4 资源分析

资源分析可以通过综合和实现中的Report Utiliation运行,也可以在tcl console窗口执行命令report_utilization -name utiliza运行,其中utiliza为自定义的窗口标签名称,结果如下图,包含CLB资源,I/O,时钟,BlockRAM等

在summary中已直方图形式展示了LUT,FF,IO,BUFG,MMCM的使用率,primitive则展示了使用资源对应的原语。

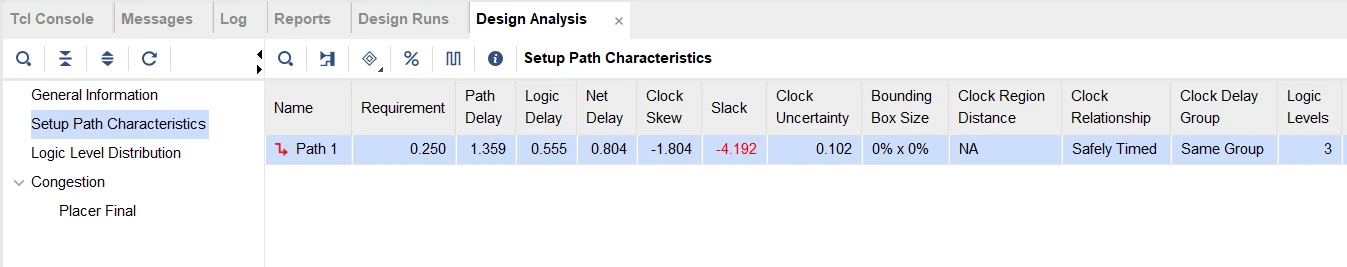

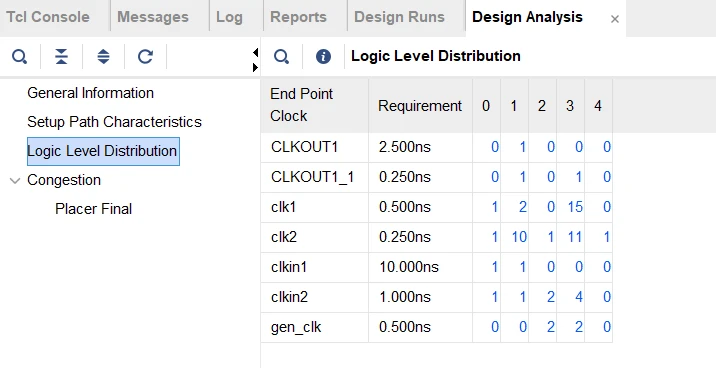

2.5 逻辑级数分析

逻辑级数是指时序路径中起点与终点中间的组合逻辑门个数,包括LUT,进位链,和Slice中的F7MUX/F8MUX/F9MUX,通常,逻辑级数越大,传输的延迟就越大。假设LUT和连接的网线的延迟为tns,时钟周期为Tns,则最大的LUT级数不能超过T/t,即在一个时钟周期内数据必须到达终点。

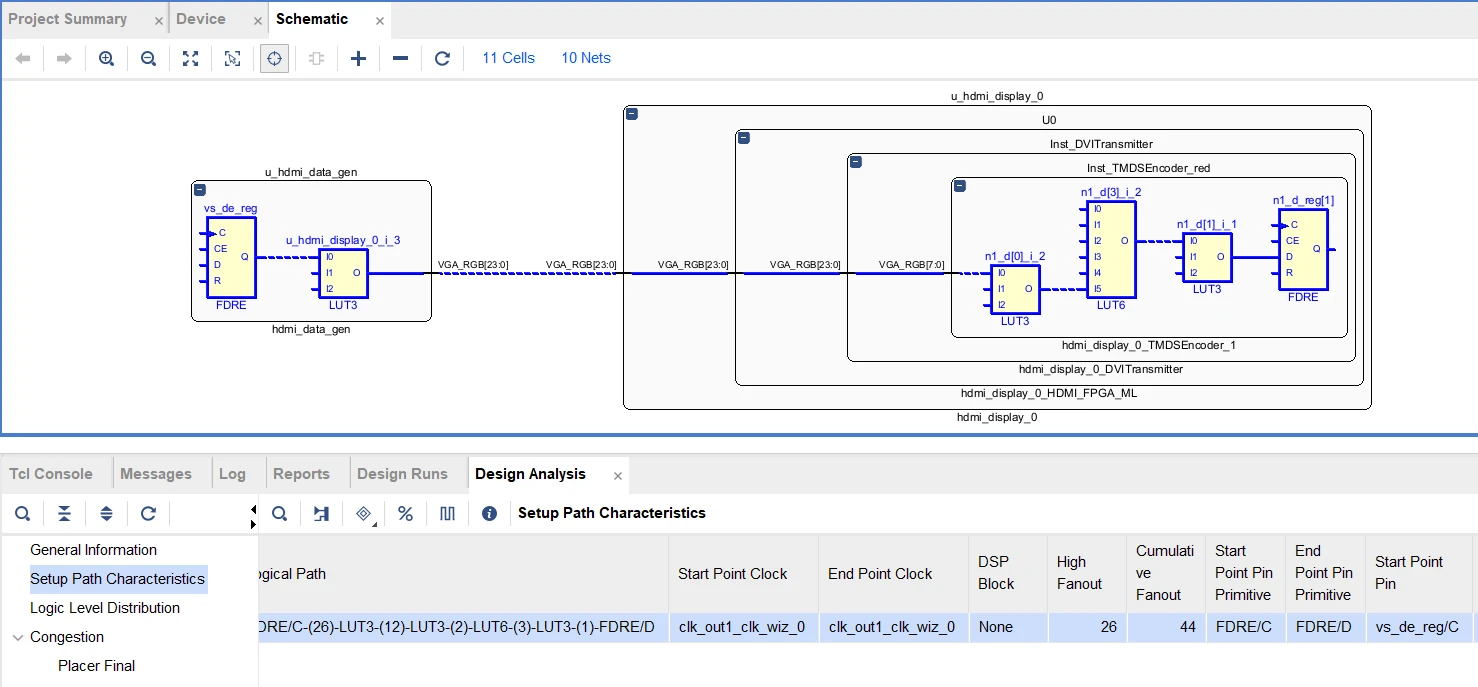

逻辑级数的分析使用命令report_design_analysis -name design_name来分析,以下图为例

Setup_Path_Characteristics显示时序路径中setup最差的信息,在schematic中,显示了起点到终点的连接关系

在logic level distribution中,右侧0-5分别为逻辑级数,下面的数字表示对应逻辑级数下时序路径的数量。

2.6 扇出分析

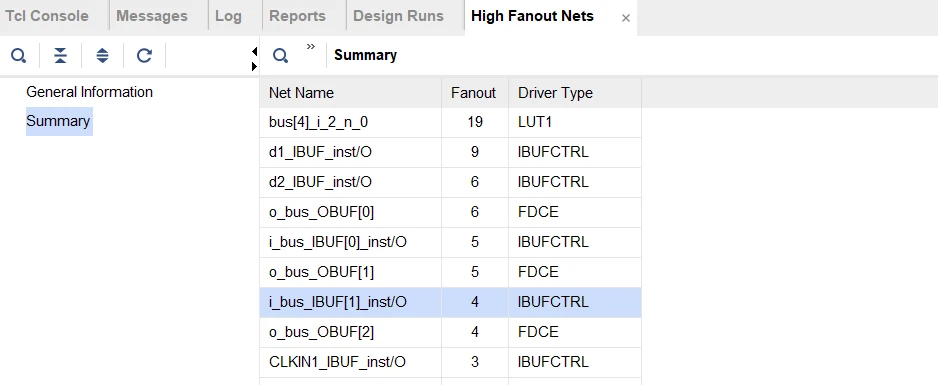

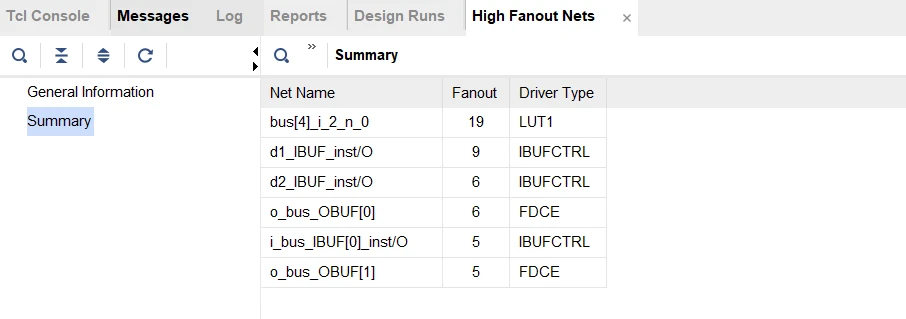

Vivado中针对扇出也有专门的分析报告,通过执行report_high_fanout_nets生成报告,下图报告中,summary中显示了具体信息,包含了设计中所有net的fanout数量以及对应的Driver类型

也可以通过参数-fanout_greater_than和-fanout_lesser_than来设置显示指定fanout数量范围的net,以显示fanout大于4的位列,执行report_high_fanout_nets -name fanout -fanout_greater_than 4

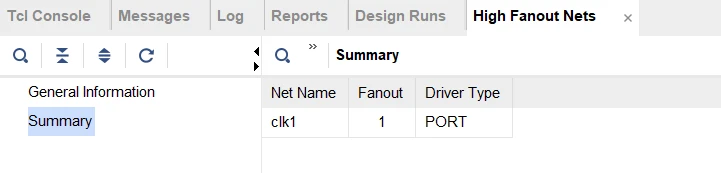

也可以显示指定时钟的fanout,report_high_fanout_nets -name fanout -clocks clk1

更多的设置参数可以在tcl console使用help report_high_fanout_nets查看使用

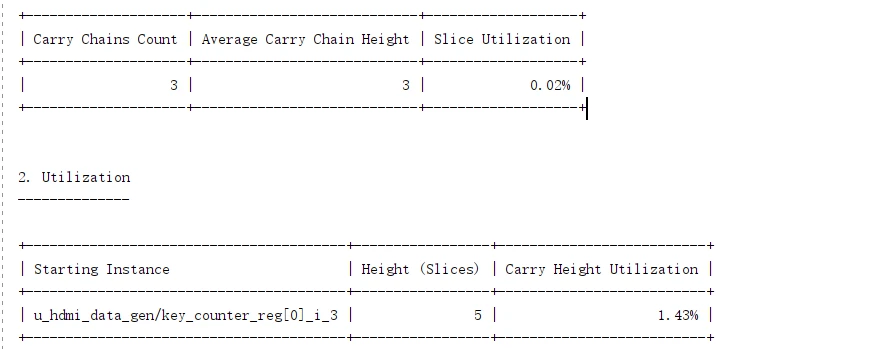

2.7 进位链分析

进位链分析使用命令report_carry_chains进行报告,不同于扇出和逻辑级数可以窗口显示,进位链分析结果只能tcl窗口显示,报告中统计了进位链的数量,长度

2.8 控制集分析

通常,由同一组控制信号,如时钟信号,使能信号,置位/复位信号相同的触发器为一个控制集,这些触发器可以放置在一个slice中,时序效果将更好,但需要更多的LUT资源。使用命令report_control_sets来报告,下图为添加了参数-hierarchical按层级展示控制集,下图为使用参数-hierarchical按层级来显示控制集的结果。报告中由四类信息

1. Summary

2. Histogram

3. Control Sets by Hierarchy

4. Flip-Flop Distribution

主要看Flip-Flop Distribution,Total registers类即显示对应控制集下的寄存器数量,Total slices为占用的slice数目

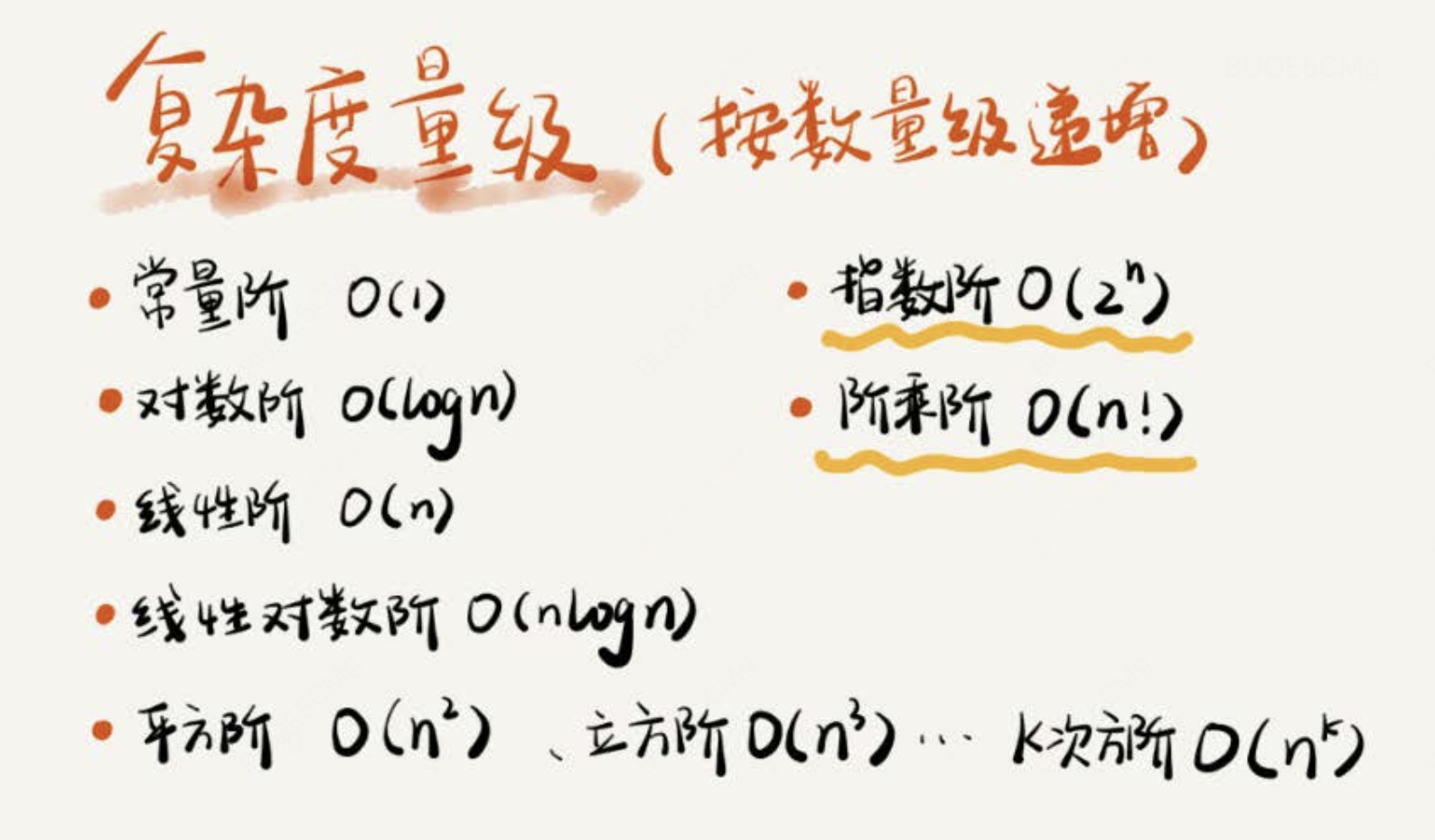

2.9 复杂度分析

复杂度分析主要用于评估设计的收敛难度,使用report_design_analysis命令可以生成对应报告。

setup path characteristics显示setup值最差的路径

logic level distribution中按时钟展示对应的logic level

在命令后再加入参数-complexity,会计算设计的rent value,该值表示模块之间的关联性强弱,越大则关联性越大,此处因为工程太小,所以未计算rent value

rent value值在0-0.65表示正常范围,在0.65-0.85时则要关注了,收敛存在一定难度,如果大于0.85并且模块的total instances也超过15000,表示布局布线将失败

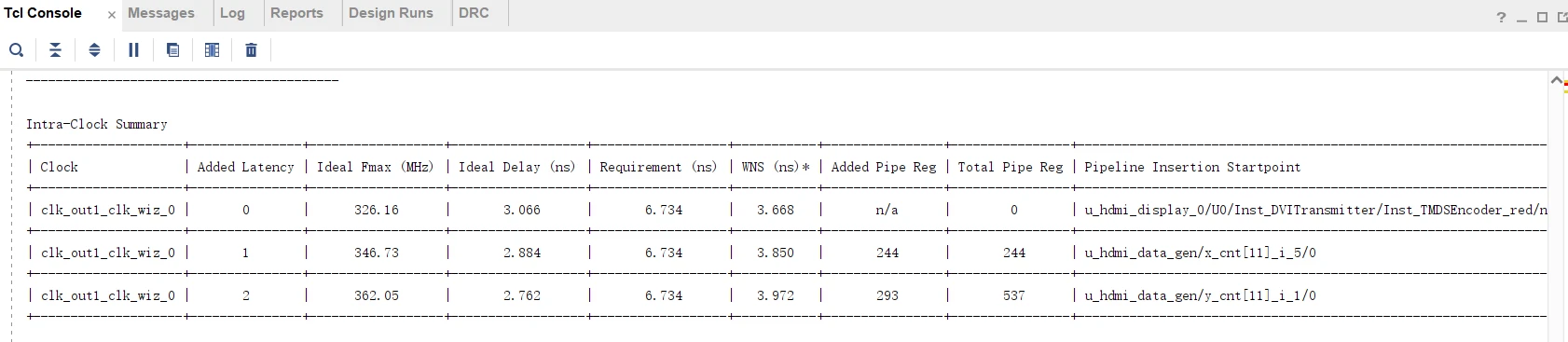

2.10 pipeline分析

对于较长的组合逻辑,可以通过插入寄存器改善时序,对于插入的位置,可以参考pipeline报告的Pipeline insertion startpoint,Clock 为分析路径的时钟,Added Latency 为增加的pipeline阶段的数目,Ideal Fmax 为当前的最大频率,Ideal Delay 为当前最小的时钟周期,

Added Pipe Reg 在给定的added latency下,需要添加pipeline寄存器的最大数目,Requirement为在当前时序约束下需要的最大时延,WNS 为要求的最小时延,Pipeline Insertion Startpoint 为最长时延路径的起点单元,Pipeline Insertion Endpoint 为最长时延路径的终点。

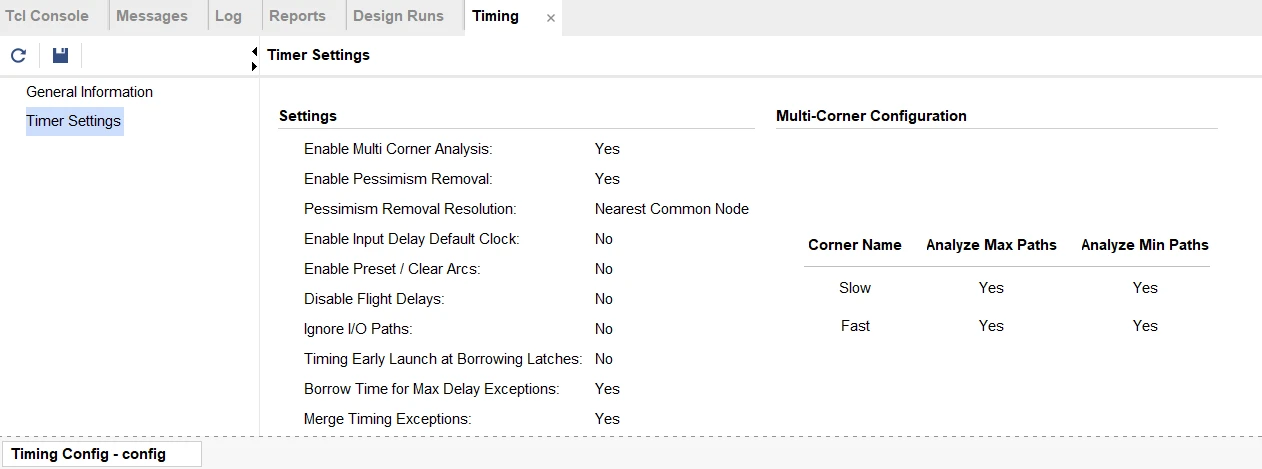

2.11 时序分析配置报告

使用report_config_timing 查看时序分析的配置项

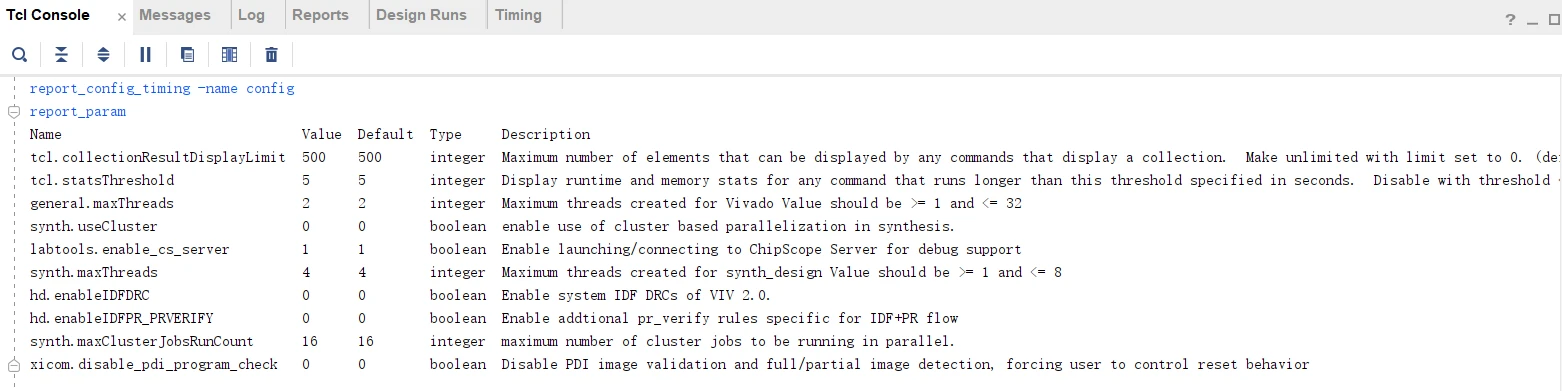

2.12 参数配置报告

使用命令report_param查看设计中参数相关的配置,description由参数功能的描述

三、参考资料

《Vivado/tcl 零基础入门与案例实战》

![[激光原理与应用-77]:基于激光器加工板卡的二次开发软件的系统软硬件架构](https://img-blog.csdnimg.cn/direct/cb9383ef13cc4000a65a8a0204c1d38e.png)