修改逻辑

在中实现后,可以修改非只读逻辑对象的属性Vivado IDE以及Tcl。

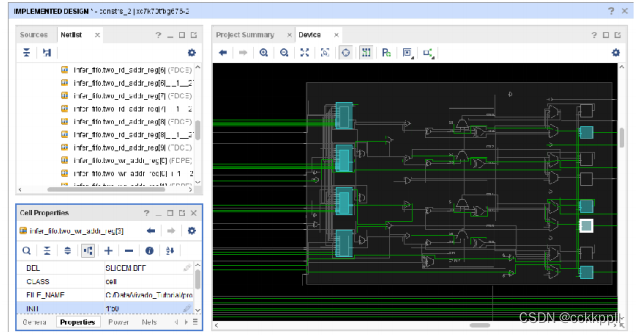

注意:有关Tcl命令的更多信息,请参阅Vivado Design Suite Tcl命令参考指南(UG835),或键入<command>-help。要在“设备”窗口中修改对象的属性,请执行以下操作:

1.选择对象。

2.在“属性”窗口的“属性”视图中修改对象的属性值。

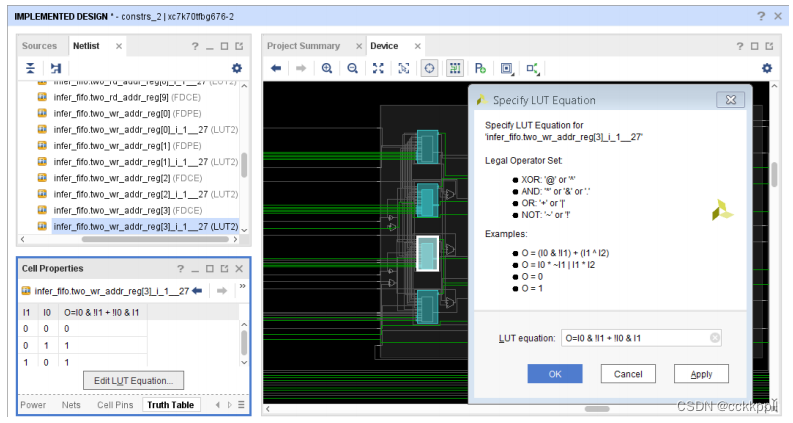

这些属性可以包括从块RAM INIT到时钟修改的所有内容MMCM上的属性。还有一个特殊的对话框,用于设置或修改LUT上的INIT物体。此对话框允许您指定LUT方程并让工具确定适当的INIT。

保存修改

•要捕获内存中对设计所做的更改,请编写设计的检查点。由于工作分配没有反向注释到设计中,因此必须添加工作分配以便它们影响下一次运行。

•要在项目模式中将约束保存到约束文件中,请选择“文件” → 约束 → 拯救

修改网表

网表有时需要更改以修复功能逻辑错误、满足时间限制或插入调试逻辑。您可以使用Tcl命令在合成后、放置后等修改现有网表,以及路线后。

Netlist修改命令

以下命令允许您修改现有网表:

•创建端口

•remove_port

•创建单元格

•remove_cell

•create_pin

•remove_pin

•创建net

•remove_net

•connect_net

•disconnect_net

注意:有关这些Tcl命令的更多信息,请参阅Vivado Design Suite Tcl命令参考指南(UG835),或键入<command>-help。

网表修改命令适用于后合成、后放置或后路由网表。

在修改网表之前,必须将其加载到内存中。网表修改命令允许您在网表位于内存中时对其进行逻辑更改。您可以使用write_checkpoint命令保存更改。

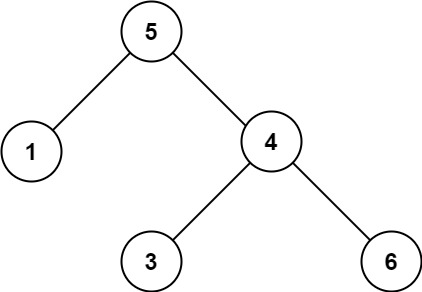

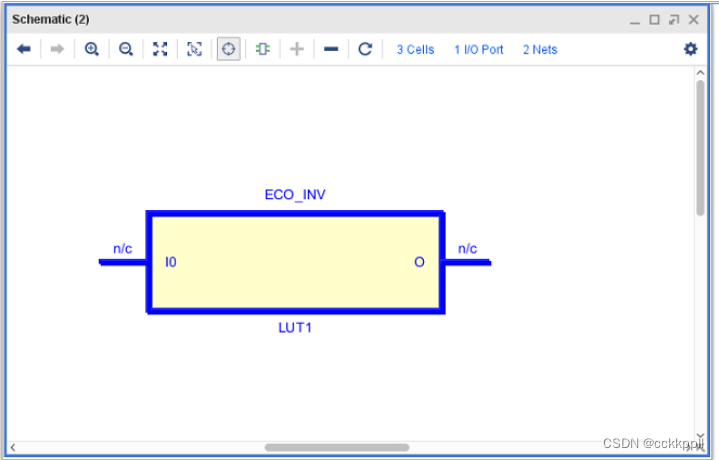

提示:Vivado工具允许您使用网表修改无条件地更改网表命令。但是,逻辑更改可能导致无效的物理实现。建议在执行网表更改后运行DRC。此外,DRC作为添加过程的一部分运行对物理实现的逻辑更改。这些DRC标记任何无效的网表更改或新的在实际实施开始之前需要解决的物理限制。只要网表修改命令,逻辑更改就会反映在原理图中执行。下图显示了使用LUT1作为参考单元格。

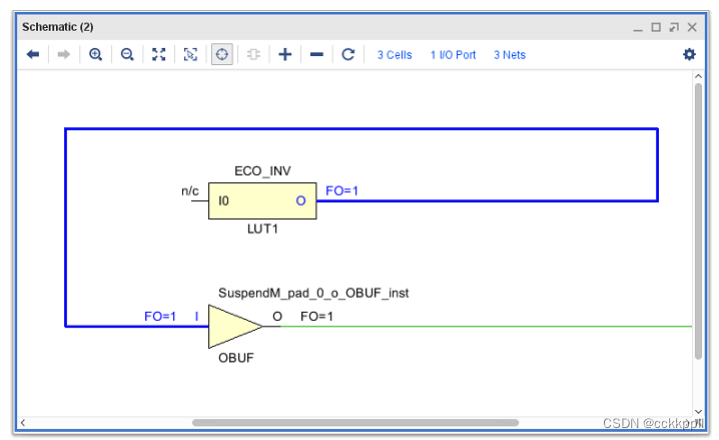

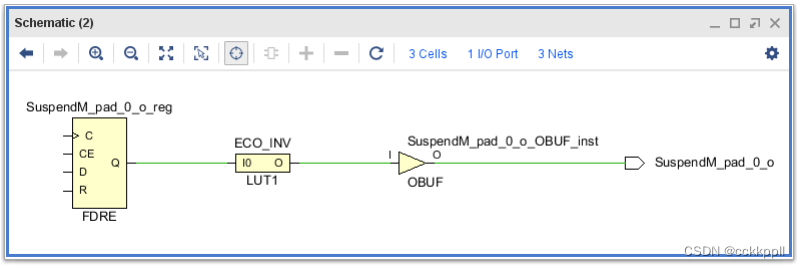

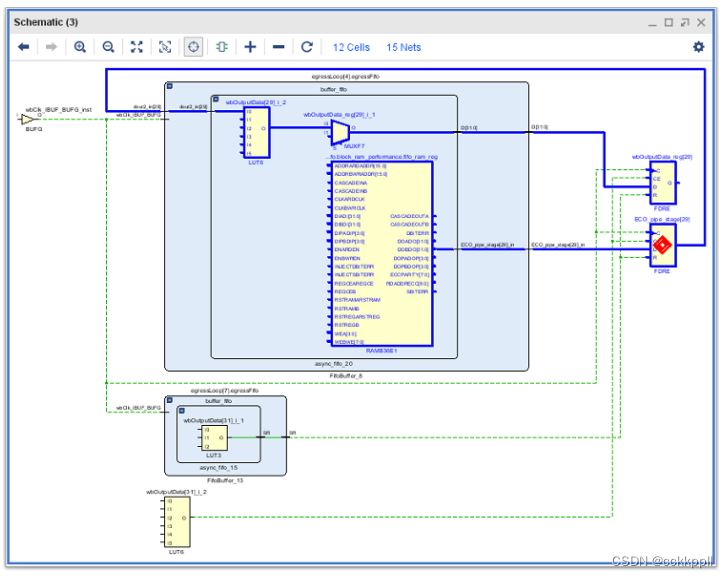

当LUT1的输出连接到OBUF时,示意图反映了这种变化显示ECO_INV/O引脚不再带有“无连接”。下图显示得到的示意图。

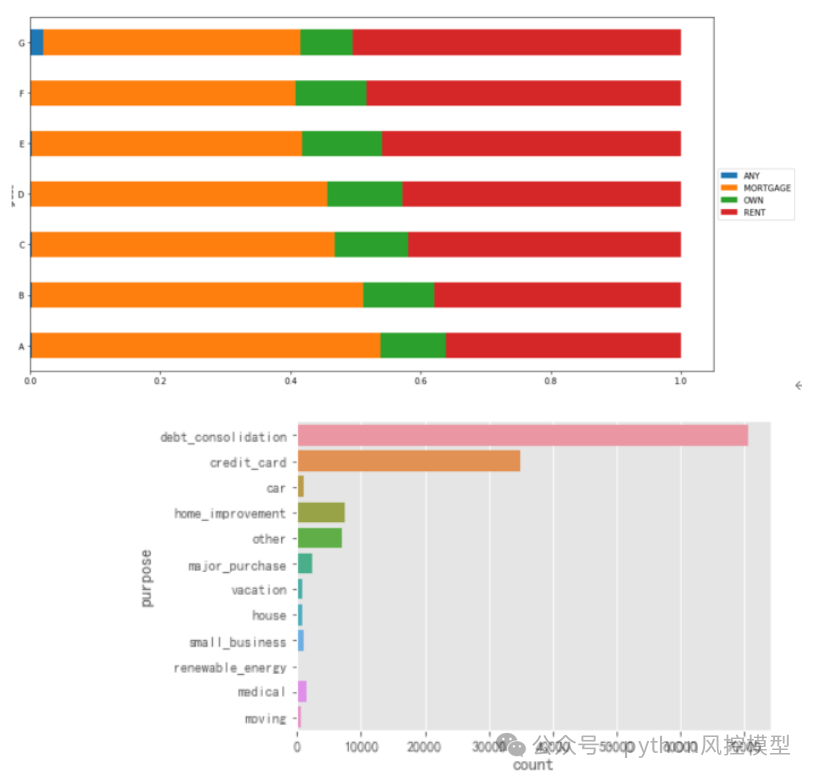

使用案例

以下示例显示了网表修改的一些最常见的用例。这个示例显示了原始逻辑网表的示意图,列出了修改Tcl的网表命令,并显示最终修改的网表的示意图。

用例1:反转网络的逻辑值

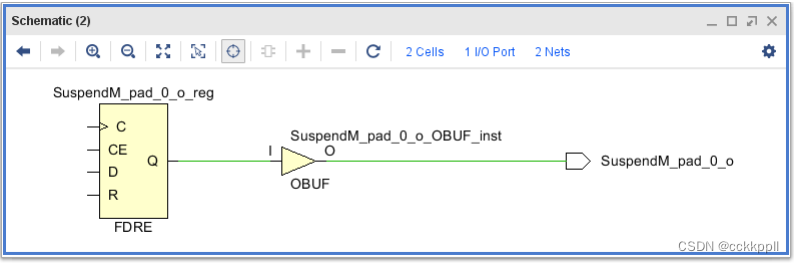

反转网络的逻辑值可以像修改现有的LUT方程一样简单LUTx基元,或者它可能需要插入一个LUT1,该LUT1被配置为将其输出反相输入下图中的示意图显示了驱动输出的FDRE原语通过OBUF端口wbOutputData[0]。

以下Tcl命令显示了如何在FDRE的输出和OBUF:

在这个示例脚本中,LUT1单元ECO_INV被创建,INIT值被设置为2'h1实现反转。FDRE和OBUF之间的网络与Q断开FDRE的输出引脚,并且反相LUT1单元ECO_INV的输出连接到IOBUF的输入引脚。最后,在的Q输出引脚之间创建并连接一个网络FDRE和反相LUT1单元的I0输入引脚。下图显示了由此产生的逻辑网表更改的示意图。

成功修改网表后,必须实现逻辑更改。这个必须放置LUT1信元,并对信元之间的网络进行路由。这必须在没有修改未修改的设计部分的放置或布线。Vivado在上运行place_design时,实现命令会自动使用增量模式修改后的网表,日志文件通过显示“增量放置”反映了这一点总结

要保留现有路由并仅路由修改后的网络,请使用route_design命令这只会增量路由更改,如您在增量路由中所见重用日志文件中的摘要:

而不是使用增量自动放置和路由修改后的网表place_design和route_design命令,可以使用提交逻辑更改手动放置和布线约束。有关详细信息,请参见修改放置以及本章前面的“修改路由”部分。

用例2:添加调试端口

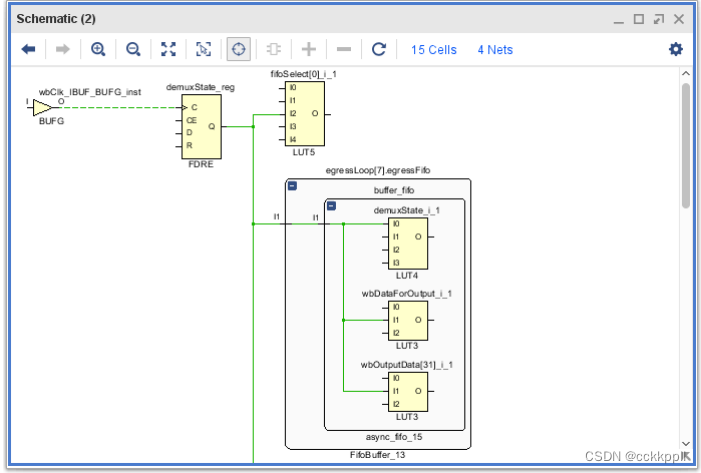

您可以通过网表更改轻松地将内部信号路由到调试端口。下面的示意图显示了引脚demuxState_reg/Q,您可以在设备的外部端口上观察到它。

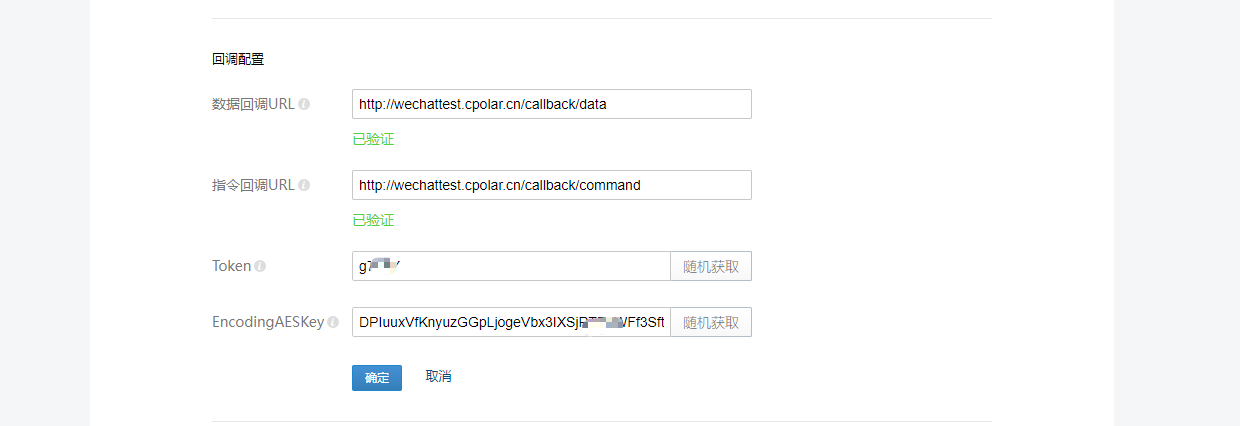

下面的Tcl脚本显示了如何向现有设计中添加端口并路由内部向新创建的端口发送信号。

示例脚本实现以下内容:

•创建调试端口。

○ 将其分配给封装引脚AB20。

○ 为其指定LVCMOS18的I/O标准。

•创建一个OBUF,通过网络ECO_OBUF1_out驱动调试端口。

•创建一个网络,将demuxState_reg寄存器的输出连接到OBUF的输入。

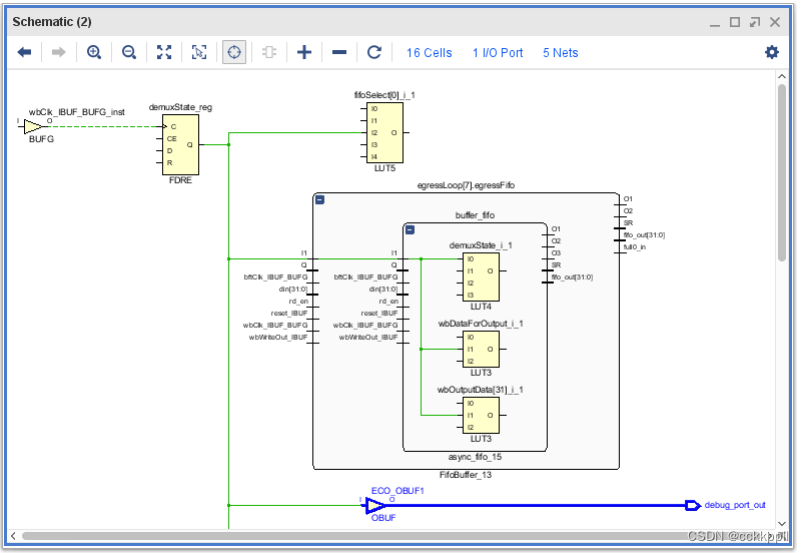

下图显示了由此产生的逻辑网表更改的示意图。

成功修改网表后,必须实现逻辑更改。由于端口已分配给封装引脚,驱动端口的OBUF自动放置在正确的位置。因此,放置者没有任何东西可放置,并且因此,当运行place_design后跟route_design。路由将内部信号连接到OBUF的新添加的网络输入,使用route_design-nets命令或手动路由网络以避免出现完整的route_design通过,这可能会更改其他网络的路由。或者,您可以运行route_design-preserve,它保留了现有的路由。请参见使用其他路线_设计选项。

用例3:添加管道阶段以改进计时

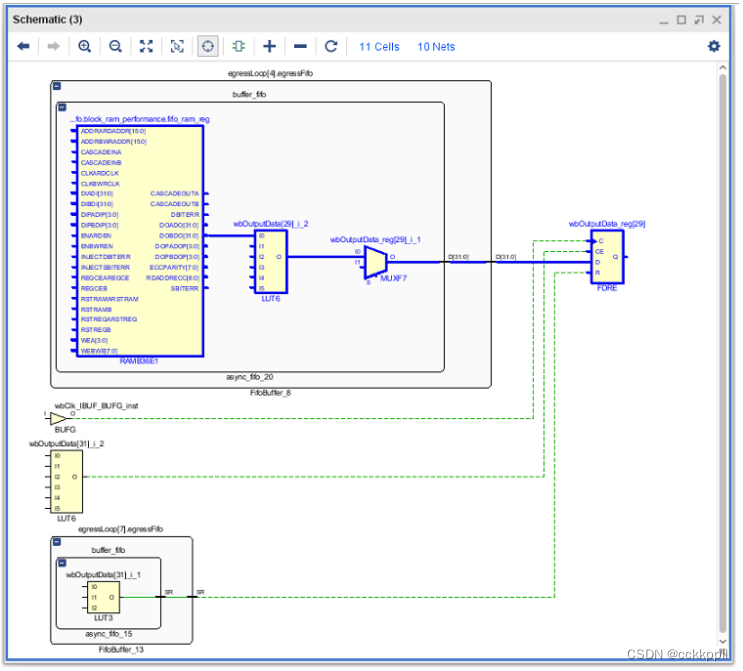

沿着一条路径添加寄存器以将组合逻辑拆分为多个循环称为流水线。流水线通过在中引入额外的延迟来提高寄存器到寄存器的性能流水线路径。流水线是否有效取决于您的设计的延迟容忍度。这个下图中的示意图显示了从RAMB36E1开始并经过通过两个LUT6单元,然后终止于FF。添加流水线级可以改善时序用于关键路径,并且可以通过修改网表来实现。

下面的Tcl脚本显示了如何在两个LUT6单元之间插入流水线寄存器。这个寄存器使用与加载寄存器相同的控制信号来实现。

成功修改网表后,必须提交逻辑更改。使用place_design和route_design命令完成此操作。