视频链接

DDR4电路设计01_哔哩哔哩_bilibili

DDR4硬件电路设计

1、DDR4基本介绍

2011年1月4日,三星电子完成史上第一条DDR4内存。DDR4相比DDR3最大的区别有三点:16bit预取机制(DDR3为8bit),同样内核频率下理论速度是DDR3的两倍;更可靠的传输规范,数据可靠性进一步提升;工作电压降为1.2V,更节能。

DDR4:第四代双倍数据率同步动态随机存取存储器(Double-Data-Rate fourth Synchronous Dynamic Random Access Memory,一般称为DDR4 SDRAM)。

//

感兴趣的话可以做一些仿真(sigrity: 时域、频域、电热仿真等)

详细内容参考B站更新的sigrity仿真内容

Sigrity-Power SI-走线阻抗和耦合性检查分析01_哔哩哔哩_bilibili

Sigrity-POWER SI 模型抽取-S参数的提取-01_哔哩哔哩_bilibili

Sigrity-SPEED2000 SRC-SI Metrics Check串扰分析01_哔哩哔哩_bilibili

POWER SI-噪声耦合分析01_哔哩哔哩_bilibili

POWER SI-3DFEM全波场S参数模型提取01_哔哩哔哩_bilibili

Power DC直流压降仿真分析01_哔哩哔哩_bilibili

Sigrity-Speed 2000 DDR Simulation 01_哔哩哔哩_bilibili

Optimize PI电容优化仿真分析01_哔哩哔哩_bilibili

//

DDR的厂家有三星、镁光、海力士、东芝、长鑫(国产)、紫光(国产)等。

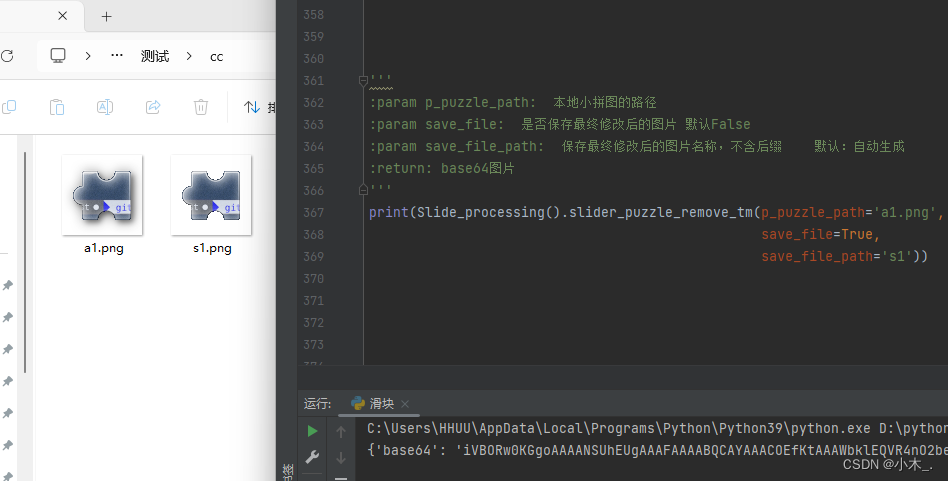

2、DDR4命名规范及详解(以镁光为例)

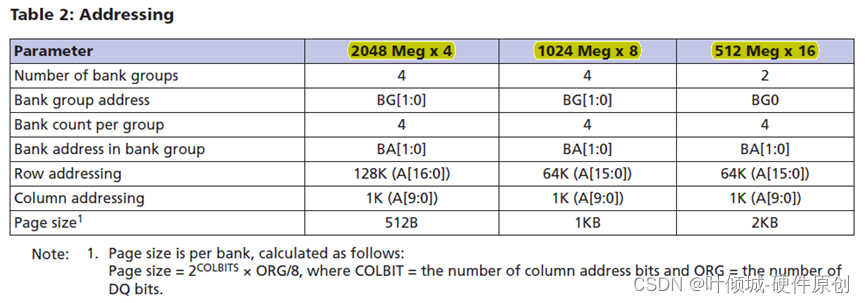

2.1、DDR4容量计算

2.2、DDR4的速率

2.3、DDR4封装(78球和96球;7种尺寸大小)

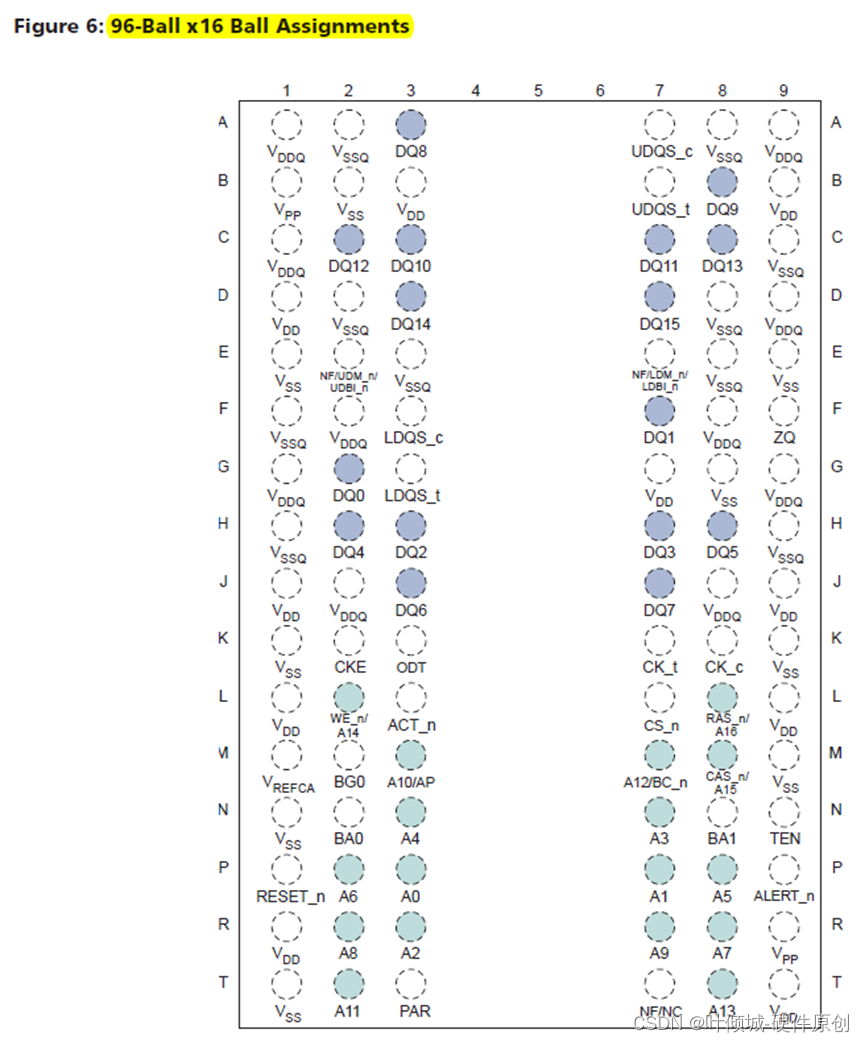

封装(Packages):4/8bit芯片采用78球FBGA封装,16bit芯片采用96球FBGA封装。 (具体的参考datasheet P24-P25)

尺寸:13.2MM X 9MM

尺寸:12MM X 8MM

尺寸:11MM X 7.5MM

尺寸:14MM X 9MM

尺寸:14MM X 8MM

尺寸:13.5MM X 7.5MM

尺寸:13MM X 7.5MM

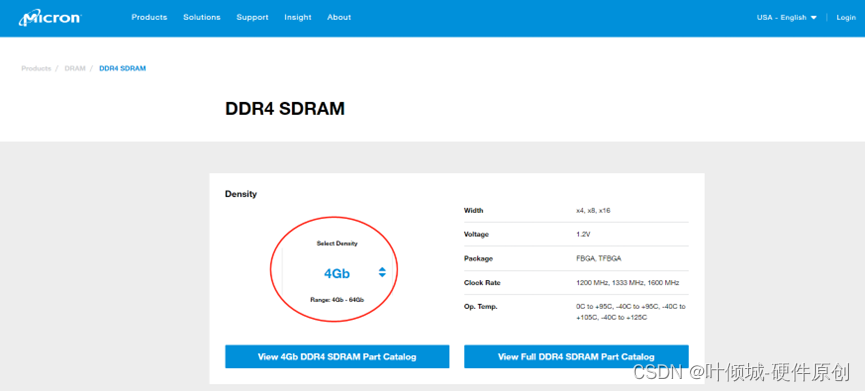

2.4、DDR4的器件选型

DDR4 SDRAM | Micron Technology Inc.(镁光的官网)

器件的选型需要根据DDR controller来选型。

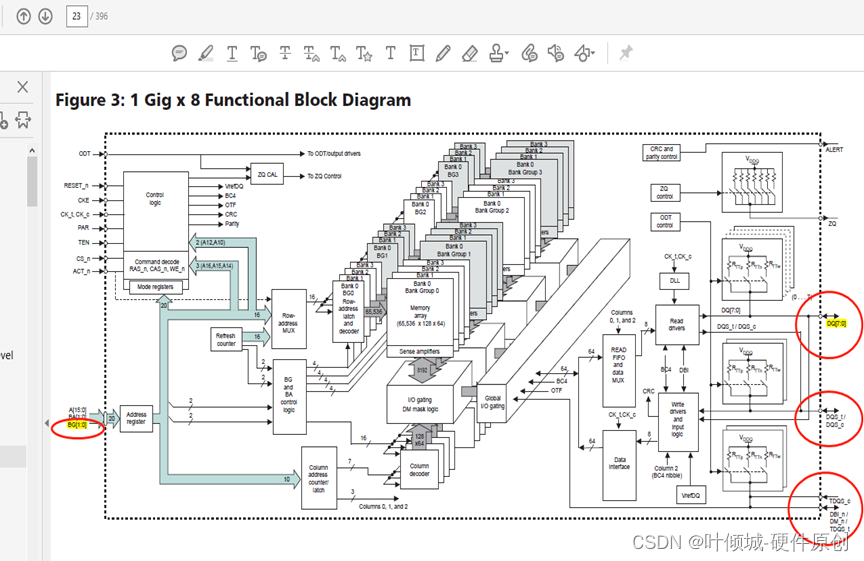

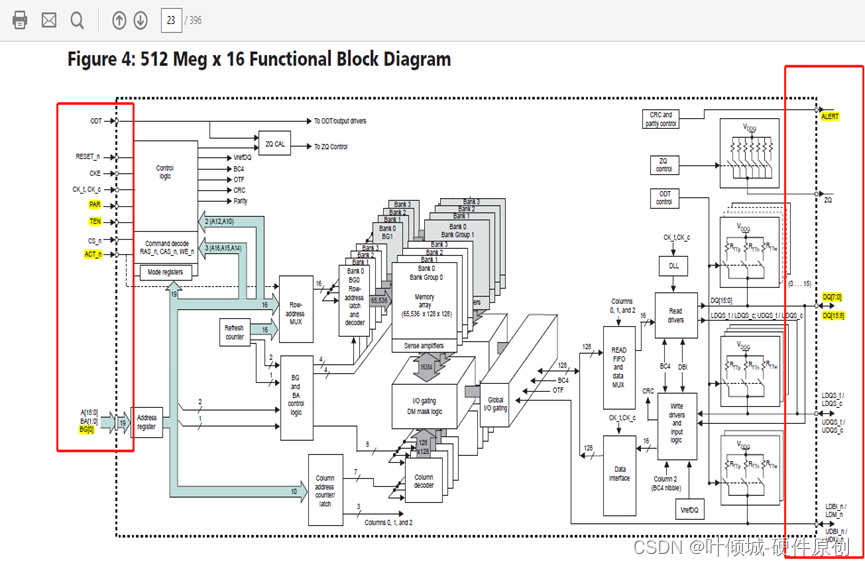

3、DDR4 X16功能框图(注意X4 X8 X16区别)

在原理图设计的时候尤其要注意。

4、DDR4管脚定义(注意X8和X16的信号区别)

DDR4的管脚可以分为电源线、时钟、数据线、地址线和控制线。

控制信号主要是用来完成DDR4与DDR4 Controller之间的状态切换。

4.1、电源线

对于电源电压,DDR4 SDRAM系统要求三个电源,分别为VDDQ、VTT和VREF。

| 管脚符号 | 类型 | 描述 |

| VDD | Supply | 电源电压,1.2V(+/-0.06V) |

| VDDQ | Supply | DQ电源,1.2V(+/-0.06V),为了降低噪声,在芯片上进行了隔离。 |

| VREFCA | Supply | 控制、命令、地址的参考电压。VREFCA在所有时刻(包括自刷新)都必须保持规定的电压。 |

| VSS | Supply | 地。 |

| VSSQ | Supply | DQ地,为了降低噪声,在芯片上进行了隔离。 |

| ZQ | Reference | 输出驱动校准的外部参考。这个脚应该连接240ohm电阻到VSSQ。 |

| VPP | Supply | DRAM激活供电:2.5V(最小2.375V、最大2.75V) |

1、主电源VDD和VDDQ

主电源的要求是VDDQ=VDD=1.2V,VDDQ是给IO buffer供电的电源,VDD是给内核供电。但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

2、参考电源VREFCA

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2。

3、用于匹配的电压VTT

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

//常用TPS51200电源芯片

实战Power5-DDR---TPS51200---01_哔哩哔哩_bilibili

参考B站视频讲解//

4、激活电压VPP(DRAM Activating Power Supply)

VPP一般为2.5V。

VPP激活电压,必须要同时或者早于VDD,电压值也要全时间段都高于VDD。

4.2、时钟

| 管脚符号 | 类型 | 描述 |

| CK_t、CK_c | Input | 差分时钟输入。(所有的地址、控制、命令信号都是通过CK_t的上升沿与CK_c的下降沿进行采样的) |

DDR4的工作时钟依赖于DDR controller的input,一般也即CPU或者交换芯片。

4.3、数据组

| 管脚符号 | 类型 | 描述 |

| DQ | I/O | 数据输入/输出,双向数据总线。 |

| DML_B/ DBIL_B DMU_B/ DBIU_B | I/O | 数据掩码以及数据总线倒置:DM信号是作为写数据的掩码信号,当DM信号为低电平时,写命令的输入数据对应的位将被丢弃。DM在DQS的两个条边沿都采样。同时,在MR5中的A10,A11,A12可选择此信号是DM还是DBl。在X8设备中, MR1的A11可控制此信号是DM或者TDQS, DBI为低电平时,DDR4 SDRAM会将数据进行翻转存储以及输出,反之, DBI为高电平时,则不会翻转数据。TDQS仅支持X8设备。 (更加详细的看datasheet P28) |

| DQS_t,DQS_c UDQS_t,UDQS_c、 LDQS_t,LDQS_c、 | I/O | 数据选通信号:输入时与写数据同时有效,输出时与读数据同时有效,与读数据时边沿对齐的,但是跳变沿位于写数据的中心。在x16系统中,DQSL对应到DQL0_7;DQSU对应到DQU0_7;DQS_t,DQSL_t与DQSU_t分别与DQS_c, DQSL_c与DQSU_c,对应为差分信号对。DDR4 SDRAM仅支持选通信号为差分信号,不支持单根信号的数据选通信号。 |

4.4、地址、控制

地址

| BA0 BA1 | Input | Bank地址输入。(bank address inputs) |

| A0-A9, A10/AP, A11, A12/BC_N, A13 A14/WE_N A15/CAS_N A16/RAS_N | Input | 地址输入。A10有AP(Auto precharge自动预充电)功能、A12有BC_N(burst chop突发中止)功能、A14有WE_N(写使能)、A15有CAS_N(行地址选通)功能,A16有RAS_N(列地址选通)功能。 |

| BG0 BG1 | Input | bank group address inputs Bank Group地址输入;BG0-BG1可以选择当前的ACT、READ、WRITE或是PRE命令是对哪一个BANK组进行操作。在MODE REGISTER SET命令中,BG0也参与模式寄存器的选择。在X4、X8系统中,有BG0和BG1,而X16系统中,仅有BG0。 |

控制

| 管脚符号 | 类型 | 描述 |

| CKE | Input | 时钟信号使能。通过此电平,可以控制芯片是否进入低功耗模式。 |

| CS_n | Input | 片选。(DDR芯片使能)用于多个RANK时的RANK组选择。 |

| ODT | Input | 片上终端使能。 |

| RESET# | Input | 复位,低有效。正常操作过程中,此信号为高电平。 |

| ALERT_N | OUT | (Alert output) 报警信号,若命令/地址出现奇偶校验错误或者CRC错误,该PIN脚拉低,告知DDR控制器。(上拉4.7K到DDR_1V2) |

| TEN | IN | Connectivity test mode 连通性测试模式使能信号,高电平使能测试模式。正常操作过程中,必须拉低。(下拉499Ω到地。) |

| PAR | IN | 命令/地址信号的奇偶校验使能,可通过寄存器禁用或者使能。 |

| ACT_N | IN | 命令激活信号,这个信号为低电平时,可以通过A[14:16]地址信号线选择激活命令的行地址。为高电平时,Address信号线正常使用。 |

5、DDR4与DDR3的区别

DDR4新增功能

(1)新的JEDEC POD12接口标准(工作电压1.2V) ;

(2)DBI:可以降低功耗并且提升数据信号完整性;

(3)Bank群组结构:是个8n预取群组结构,它可以使用两个或者四个Bank组,这允许DDR4内存在每个Bank群组单独被激活、读取、写入或刷新操作,这样可以带来更高的内存速度和带宽;

(4)取消了Derating,时序仿真计算不再繁琐;

(5)DQ动态确定Vref,增加了眼图要求;

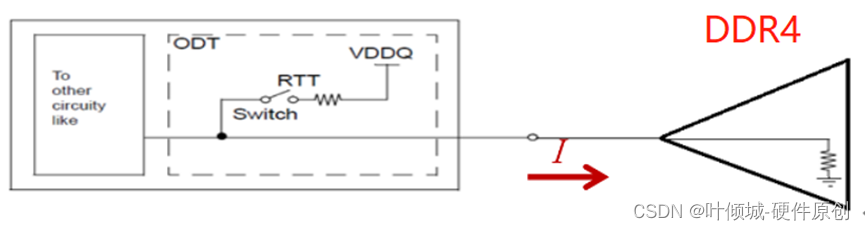

(6)新的终止调度:在DDR4中DQ bus可以转移终止到VDDQ,这样即使VDD电压降低的情况下也能保证稳定;

(7)新的数据总线CRC技术,可以进行传输过程中的错误侦测,特别对非ECC内存进行写入操作时有帮助;

(8)针对命令和地址总线的新的CA奇偶校验;突发长度和突发停止长度分别为8和4 ;

(9)正常和动态的ODT:改进ODT协议,并且采用新的Park Mode模式可以允许正常终结和动态吸入终结,而不需要去驱动ODT Pin。

(10)Differential Signaling(差分信号技术)信号分组;

DDR3地址信号的分组 DDR4地址信号的分组

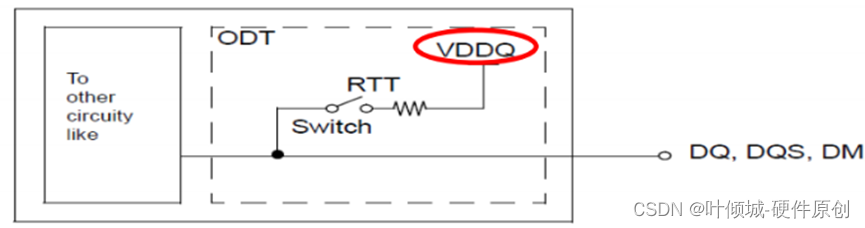

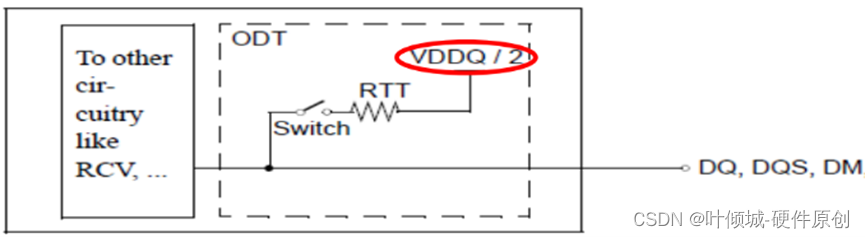

1、POD和SSTL的比较

POD电平的全称是Pseudo Open-Drain伪漏极开路。

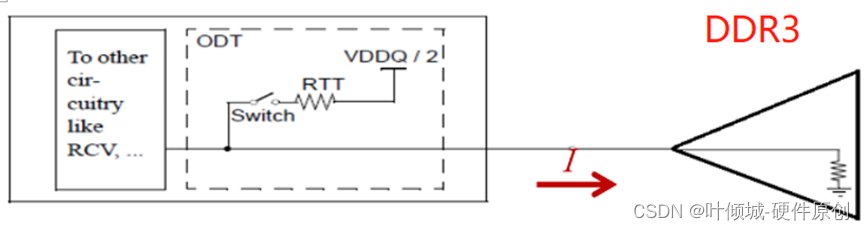

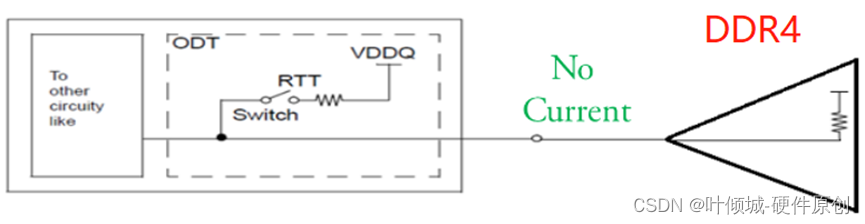

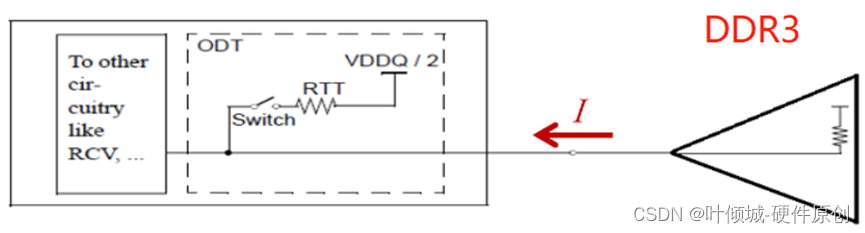

POD作为DDR4新的驱动标准,最大的区别在于接收端的终端电压等于VDDQ,而DDR3所采用的SSTL接收端的终端电压为VDDQ/2。这样做可以降低寄生引脚电容和I/O终端功耗,并且即使在VDD电压降低的情况下也能稳定工作。其等效电路如图1(DDR4), 图2(DDR3)。

DDR4 POD (Pseudo Open Drain)

DDR3 SSTL(Stub Series Terminated Logic)

可以看出,当DRAM在低电平的状态时,SSTL和POD都有电流流动

而当DRAM为高电平的状态时,SSTL继续有电流流动,而POD由于两端电压相等,所以没有电流流动。这也是DDR4更省电的原因。

DBI的全称是Data Bus Inversion数据总线反转/倒置,它与POD电平密不可分,它们也是DDR4区别于DDR3的主要技术突破。

2、数据总线倒置 (DBI)

3、ODT控制

为了提升信号质量, 从DDR2开始将DQ, DM, DQS/DQS#的Termination电阻内置到Controller和DRAM中, 称之为ODT (OnDie Termination)。Clock和ADD/CMD/CTRL信号仍需要使用外接的Termination电阻。

4、参考电压VREF

DDR信号一般通过比较输入信号和另外一个参考信号(Vref)来决定信号为高或者低,然而在DDR4中,一个VrefDQ却不见。在DDR4的设计中,VREFCA和DDR3相同,使用外置的分压电阻或者电源控制芯片来产生,然而VREFDQ在设计中却没有了,改为由芯片内部产生,这样既节省了设计费用,也增加了Routing空间。

6、DDR4基本技术原理

7、DDR4设计要点(★)

8、硬件实战设计 (★)

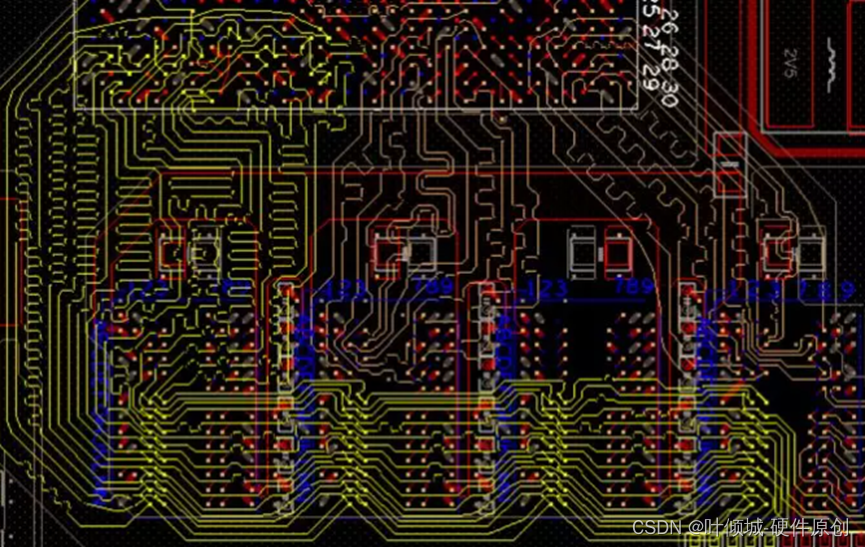

8.1、XCZU9EGFFVB1156硬件实战---1片16位DDR4

8.2、XAZU3EG-SFVC784硬件实战---2片16位DDR4

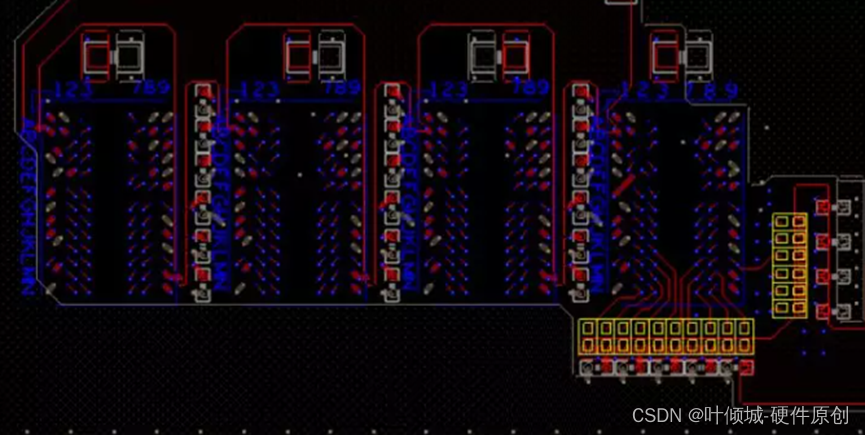

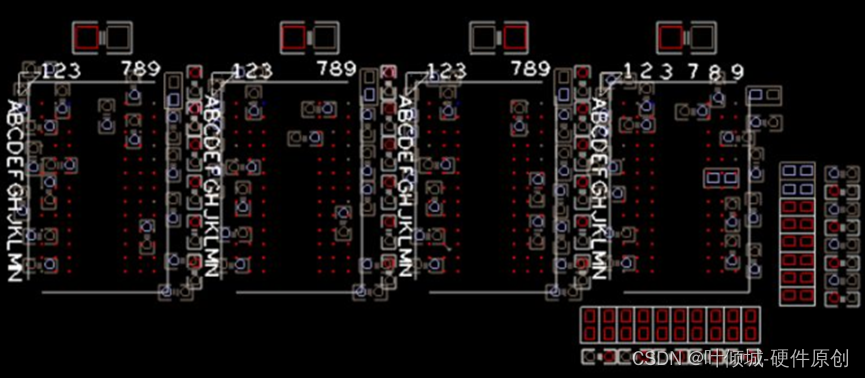

8.3、ZCU111硬件实战(16位)---4片16位DDR4

8.4、XCVU9PFLGA2104硬件实战-5片16位DDR4

8.5、VCU128硬件实战-5片DDR4(4片16位+1片8位)

8.6、瑞芯微 RK3399

9、DDR4 PCB设计要点

9.1、DDR4的PCB布局、布线通用设计要求

a)布局时走FLY-BYE拓扑结构。

b)电源走线保证足够的通流能力。

c)确保回流路径的连续性:DDR4走线禁止跨分割,尽量参考地平面,也可参考DDR的IO电源,禁止参考其他电源。

d)避免在参考平面边缘走线:当DDR4信号的走线靠近参考平面的边缘时,保证走线与参考平面的边缘≥40 Mil的间距。

e)避免换层走线以减少过孔的数量:由于DDR4的工作频率很高,时钟和数据信号速率一般都会达到400MHz以上,为了避免过孔的寄生电容和电感对信号质量的影响,需要通过控制换层的次数严格控制时钟线上过孔的数量。

f)保持信号线间距:当两个不同信号线之间距离过近时,会因电磁场的耦合导致串扰的产生。为了降低这种串扰,需要在不同类型信号线之间保持大于3W间距,禁止反焊盘上走线。

9.2、DDR4电源设计要求

a) VTT电源孤岛尽可能靠近内存颗粒以及终端调节模块放置。

b)终端调节模块的Sense引脚走线需要从VTT电源孤岛的中间引出。

c)降低Vref上的噪声。

d)禁止将VREF、VTT作为信号的参考平面,且然VREF和VTT电压相同,但VTT的噪声比较大,建议将VREF,VTT分开为不同的网络,从不同的电源或者通过分压电路进行供电。

电源处理

(1)VDD(1.2V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.2V);VDD的容差要求是5%,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性。

(2)VTT(0.6V)电源,它不仅有严格的容差性,而且还有很大的瞬间电流;可以通过增加去耦电容来实现它的目标阻抗;由于VTT是集中在上拉电阻处,不是很分散,且对电流有一定的要求,在处理VTT电源时,一般是在元件面同层通过铺铜直接连接,铜皮要有一定宽度(120mil)。

(3)VREF(0.6V)VREF要求更加严格的容差性,但是它承载的电流比较小。它不需要非常宽的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。因其相对比较独立,电流也不大,布线处理时建议用与器件同层的铜皮或走线直接连接,无须再电源平面层为其分配电源。注意铺铜或走线时,要先经过电容再接到芯片的电源引脚,不要从分压电阻那里直接接到芯片的电源引脚。

(4)VPP(2.5V)内存的激活供电,容差相对宽松,最小2.375V,最大2.75V。电流也不是很大,一般走根粗线或者画块小铜皮即可。

9.3、DDR4走线要求及其他

参考《DDR4设计规范文档(重要)》

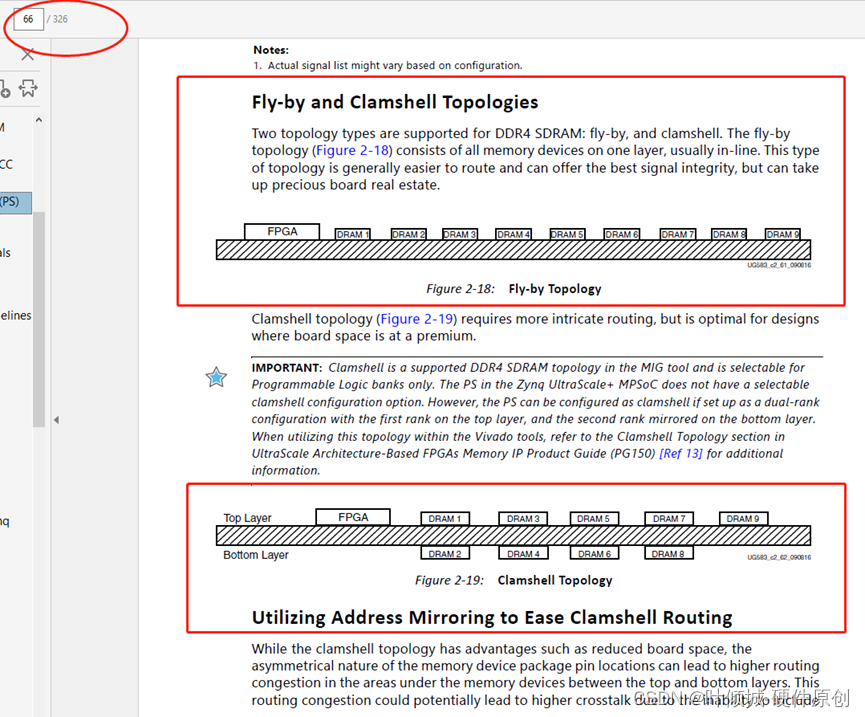

9.4、DDR4走线拓扑

在PCB上,DDR4 Layout分为所有内存颗粒在单面的 Fly-By 拓扑和双面的 Clamshell拓扑。Fly-By 拓扑更易于信号走线,信号完整性更好,但占用单板空间较大;Clamshell 拓扑更节约空间,但对走线要求更高,适用于对空间要求严格的应用场合。

DDR4的走线是“Fly-bye”结构。

(1)地址线布局布线需使用Fly-by的拓扑结构,不可使用T型,拓扑过孔到管脚的长度尽量短,长度在150mil左右

(2)VTT上拉电阻放置在相应网络的末端,即靠近最后一个DDR4颗粒的位置放置;注意VTT上拉电阻到DDR4颗粒的走线越短越好,走线长度小于500mil;每个VTT上拉电阻对应放置一个VTT的滤波电容(最多两个电阻共用一个电容)

(3)CPU端和DDR4颗粒端,每个引脚对应一个滤波电容,滤波电容尽可能靠近引脚放置。线短而粗,回路尽量短;CPU和颗粒周边均匀摆放一些储能电容,DDR4颗粒每片至少有一个储能电容。

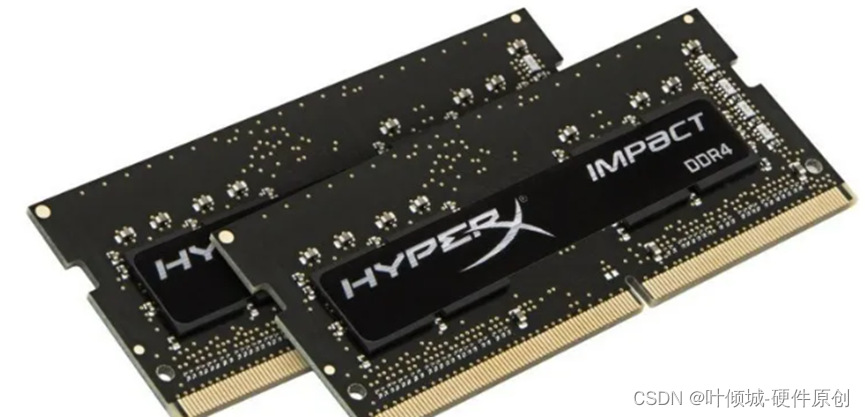

10、DDR的内存条

内存条外观变化明显,金手指变成弯曲状,频率提升明显,可达4266MHz,容量提升明显,可达128GB,功耗明显降低,电压达到1.2V、甚至更低。

DDR4内存金手指触点达到了284个,每一个触点间距只有0.85mm(DDR3内存金手指触点是240个,间距1mm)。因此DDR4的内存金手指部分也设计成了中间稍突出,边缘收矮的形状,在中央的高点和两端的低点以平滑曲线过渡,而且 DDR4防呆口位置和DDR3比较起来更靠中间一点。