文章目录

- 前言

- 时序约束的目的

- 一、时序约束种类

- 1、约束主时钟

- 2、约束衍生时钟

- 3、约束虚拟时钟

- 4、input delay

- 5、output delay

- 6、约束异步时钟组

- 7、约束互斥时钟

- 8、假路径约束

- 9、多周期约束

- 二、VIVADO时序报告

- 三、从时序的角度看为什么寄存器赋值慢一拍

前言

一边学习一边补充当中

时序约束的目的

- 告知EDA软件需要达到什么样的设计指标,然后EDA软件尽可能的优化布局布线以达到该约束指标

- 协助EDA软件进行分析设计当中的时序路径,以产生相应的时序报告,例如约束主时钟,EDA软件才可以根据此约束进行分析电路设计

一、时序约束种类

1、约束主时钟

SYSCLK_div SYSCLK_div_5mhz

(

.clk_out1 (w_clk_5mhz ),

.locked (w_clk_5mhz_lock),

.clk_in1 (i_clk )

);

对于这种直接使用Clocking Wizard IP核的时钟信号,输入输出我们都不需要进行约束,IP核会自动进行约束。

CLK_DIV_module#(

.P_CLK_DIV_CNT (40) //MAX = 65535

)CLK_DIV_module_U(

.i_clk (w_clk_5mhz ),

.i_rst (~w_clk_5mhz_lock),

.o_clk_div (w_clk_125khz )

);

对于这种我们自己设计的时钟分频模块,如果我们不对其进行约束的话,VIVADO就不知道w_clk_125khz的频率是多少,涉及到w_clk_125khz的时序逻辑,VIVADO就不会正确分析,所以我们需要对其进行约束。

2、约束衍生时钟

w_clk_5mhz是由i_clk分频出来的时钟,称为衍生时钟。

首先给衍生时钟命名;

选择主时钟pin

选择主时钟

设置分频或者倍频值

添加Source object,即我们需要约束的时钟w_clk_5mhz

注:这里需要勾选-add属性,这是因为时钟i_clk在主时钟约束那里已经被约束过了,加上add属性则可以避免冲突,在已有约束基础上再增加约束

w_clk_125khz同理,设置分频值为40即可,主时钟选择5mhz时钟,具体的工程代码设计可以先看之前介绍IIC的文章https://blog.csdn.net/m0_56222647/article/details/136815041

3、约束虚拟时钟

暂时没用到,后续补充

4、input delay

5、output delay

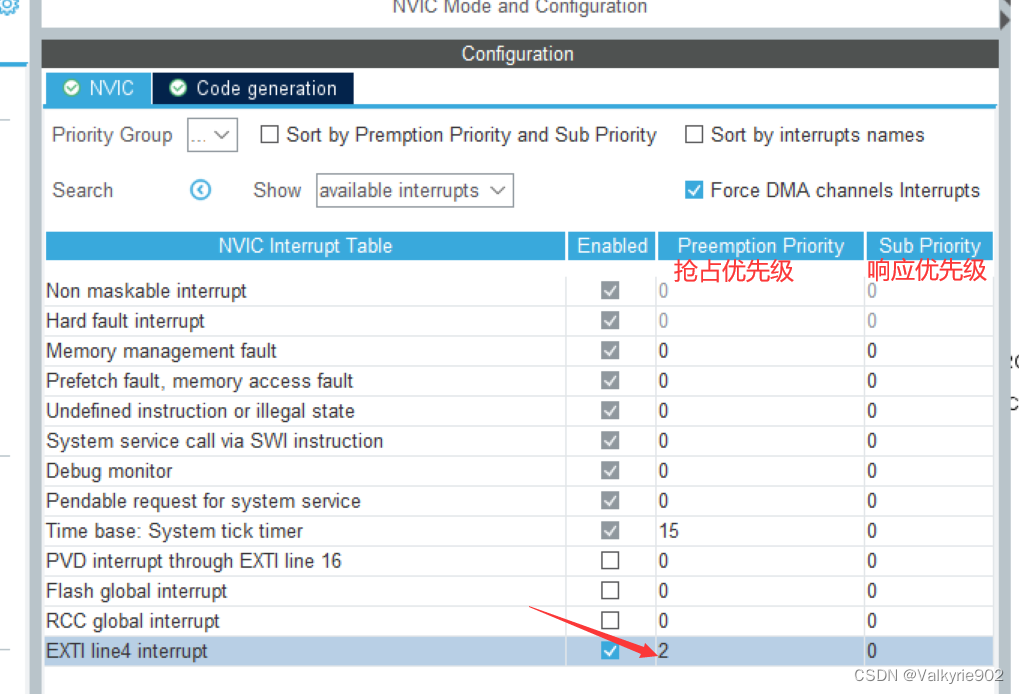

6、约束异步时钟组

静态时序分析是穷尽式的,所有寄存器之间路径都会被分析,但异步时钟寄存器之间是不用进行分析的,该约束就是告知VIVADO不要分析异步时钟路径

7、约束互斥时钟

物理互斥:即CLK1有信号时,CLK2则无信号,物理芯片上进行控制的

逻辑互斥:俩个时钟结果选择器,一次只能选择一个时钟

8、假路径约束

异步时钟路径也可以通过假路径约束

9、多周期约束

大概就让触发沿和锁存沿之间不再是只隔一个时钟周期,可以隔多个

二、VIVADO时序报告

打开布局布线后可以看到建立时间余量和保持时间,都是大于0的,时序正常。

估计是时序逻辑主要是使用主时钟i_clk分频出来的的5mhz(200ns),所以这里的建立时间余量这么大。

点击WNS可以看到最差建立时间余量这几条路径:如下图

点击第一条路径,可以在原理图里看到它的路径,原理图里面的路径,绿色为起点,红色为终点

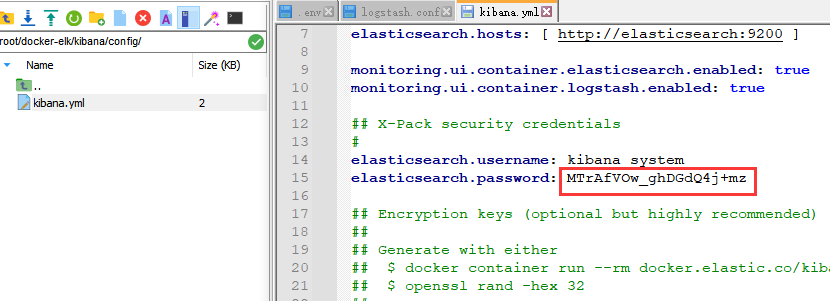

双击第一条路径可以打开时序报告:

源时钟路径,Incr是指增加的时延,Path是指当前时延总和

这里多提一嘴,经过MMCM后这里增加的时延是负的,这是由于相位调整的缘故,目的寄存器时钟也会引入负的延时,所以相对来说这个负的时延是无所谓的。

数据路径

这里是数据经过各个LUT,寄存器、进位链以及走线net的延时。

同时可以计算出数据到达时间:Tarrive = Tco + Tdatadelay = 1.964

目的时钟路径

个别名词解释:

clock pessimism : 时钟悲观度,由于温度影响,时钟最坏情况下会引入的偏移

clock uncertainly:时钟不确定度

FDCE(Setup):这里是指建立时间,按道理来说这里应该是负的,但是图中是正的,不知道啥情况,估计还是和时钟相位调整有关系吧

根据此可以计算出数据要求到达时间:

Trequired = Tcycle + Tskew - Tsu = 198.495

最终的建立时间裕量为:Trequired - Tarrive = 198.495 - 1.964 = 196.531

该数值和时序报告summary当中数值一致。

三、从时序的角度看为什么寄存器赋值慢一拍

- 时序逻辑电路并没有真正意义上的落后一拍,落后一拍的原因是因为Tco的存在,导致在当前时钟上升沿无法采集到最新的值,而只能采集到未变化的值

- 在仿真时,输入信号尽量用非阻塞赋值“<=”来模拟其来自寄存器的输出,这样的仿真结果更接近实际电路

- 可以采用“#1”这种赋值方式来模拟Tco的存在,这可以在仿真时带来很大的便利