2024.03.05:

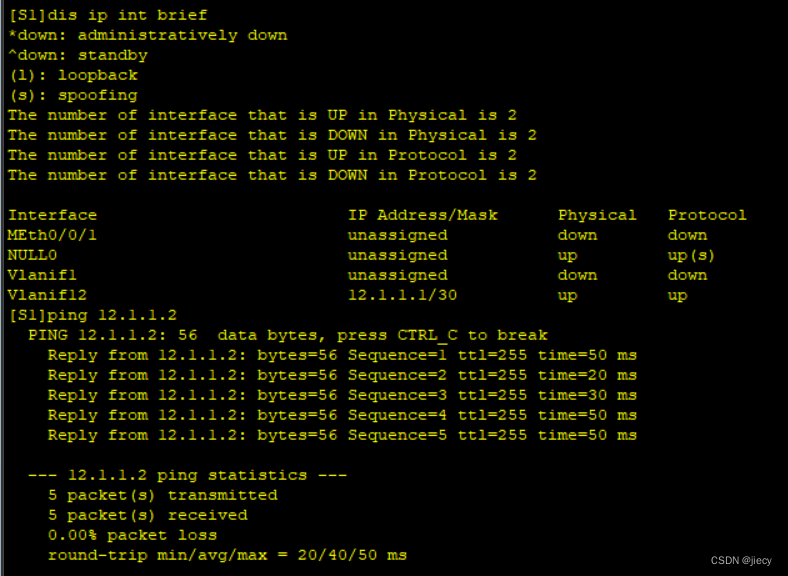

测试了开发板网线直连电脑可以传输数据。但是通过开发板→交换机→电脑,没有数据传输过去。通讯采用UDP通讯。首先是UDP传输不可靠,有可能存在丢包、包先后顺序有问题,这就无法满足后续对采集数据的傅里叶变换和傅里叶逆变换的处理。其次是尝试通过交换机传输数据过程中发现数据过不去交换机,项目时间紧,网络方面不熟悉查资料找人问都没有收获,进而改用TCP传输,TCP之前是做过的。

2024.03.07:

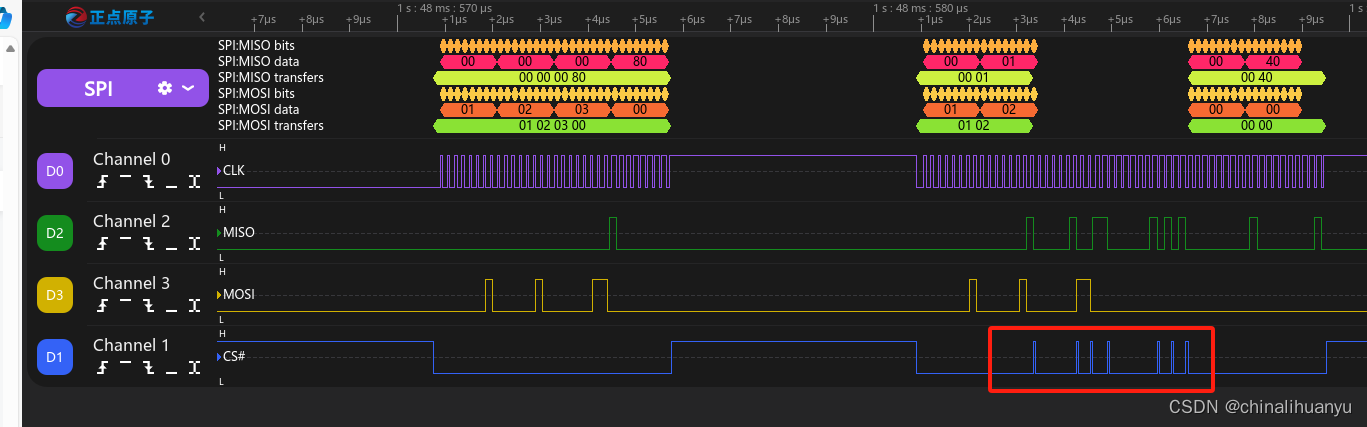

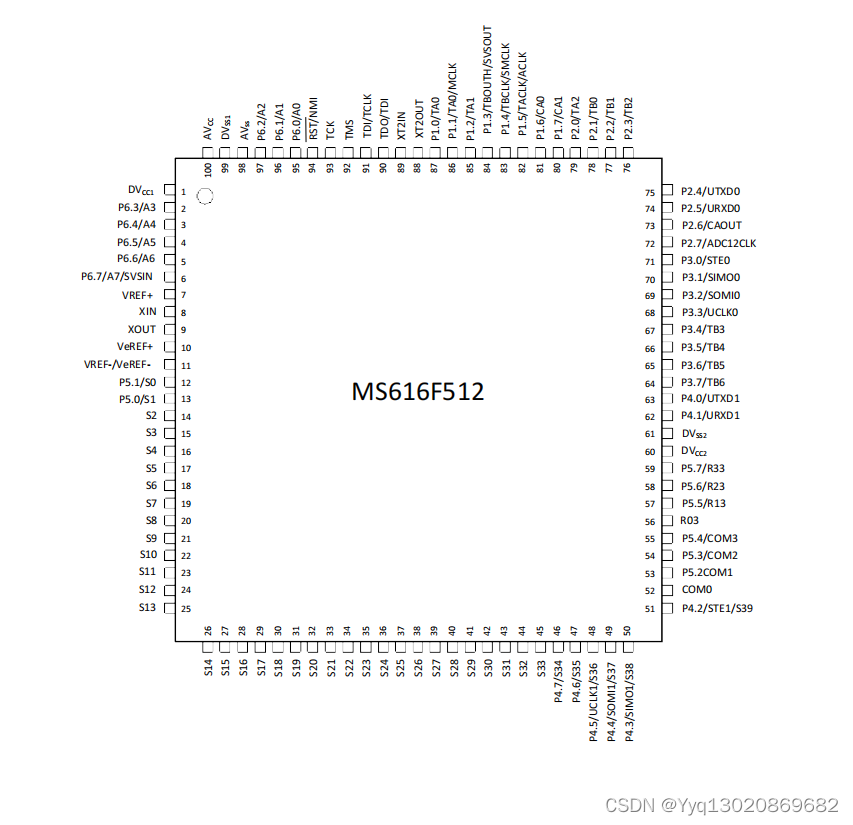

打算采用FPGA+W5500的形式尝试。我之前尝试用开发板通过杜邦线连接W5500模块,发现spi的CS信号有50ns的拉高干扰不知道哪里来的。后续如果有结果会进行更新。

2024.03.08——2024.03.15:

准备用STM32干了,但是STM32不满足项目实时传输需求。还得用FPGA。

2024.03.17:

网上搜索了Verilog编写的W5500程序,测试发现配置阶段没有CS的拉高干扰,但是后续发送数据还是有干扰,再后来修改了一下目的MAC地址,这回更差了,配置阶段都有问题了。还没有找到什么原因。o(╥﹏╥)o

而且这个程序在别人那里是可以的,我这里就不行。程序倒是不难理解。(等我调试好之后再把代码分享)。

2024.03.18:

- 自己修改了W5500模块的引脚。怀疑是不是模块接的地线不是一个IO区域的,所以导致不好使。

- 测试了将模块GND连接到了同一个IO区域上,还是不行。而且每次干扰都是50ns的拉高,为什么呢。

- 将CS下拉10k到地,也不行还是有被拉高的情况。后续再使用别人的板子测试一下我修改之后的W5500模块有没有问题吧。