安置

Vivado Design Suite放置程序将网表中的单元放置到目标AMD中的特定站点上装置与其他实现命令一样,Vivado放置程序工作于并更新,内存中的设计。

设计布局优化

Vivado砂矿器同时优化了以下方面的设计布局:

•定时松弛:选择在定时关键路径中放置单元,以最大限度地减少负松弛。

•电线长度:驱动整体放置,以最大限度地减少连接的整体电线长度。

•堵塞:Vivado砂矿器监测引脚密度并传播细胞以降低潜力路由拥塞。

设计规则检查

在开始放置之前,Vivado实现运行设计规则检查(DRCs),包括用户从report_drc中选择的DRCs,以及Vivado放置程序内部的内置DRCs。内部的DRCs检查非法放置,例如没有LOC约束和I/O的内存IP单元IOSTANDARD冲突的银行。

时钟和I/O放置

在设计规则检查之后,Vivado放置器在放置其他逻辑之前放置时钟和I/O单元细胞。时钟和I/O单元是同时放置的,因为它们通常通过复杂的特定于目标AMD设备的放置规则。对于UltraScale、UltraScale+和Versal设备,放置器还分配时钟轨道并预先路由时钟。向IOB注册单元格在此阶段处理属性,以确定哪些寄存器的IOB值为TRUE应映射到I/O逻辑站点。如果砂矿商未能兑现TRUE的IOB财产,则发出严重警告。

Placer目标

此放置阶段的放置目标是:

•I/O端口及其相关逻辑

•全局时钟缓冲器

•时钟管理瓦片(MMCM和PLL)

•千兆收发器(GT)电池

放置非固定逻辑当在放置的这个阶段放置未固定的逻辑时,放置器坚持物理约束,例如LOC属性和Pb块分配

重要!由于设备I/O架构的原因,LOC属性通常会约束单元以外的单元LOC已被应用于其。输入端口上的LOC也固定其相关I/O缓冲器的位置,IDELAY和ILOGIC。冲突的LOC约束不能应用于输入路径中的单个单元格。这同样适用于输出和GT相关单元。

时钟资源放置规则

时钟资源必须遵循7系列FPGA时钟中描述的放置规则

《资源用户指南》(UG472)、《UltraScale体系结构时钟资源用户指南”(UG572)和Versal自适应SoC时钟资源体系结构手册(AM003)。例如,一个输入驱动器全局时钟缓冲区必须位于具有时钟功能的I/O站点,必须位于对于7个串联器件,器件的相同上半部分或下半部分,以及对于UltraScale设备。这些时钟放置规则也会根据逻辑网表进行验证连接和设备站点。

当时钟和I/O放置失败时

如果Vivado放置程序无法找到时钟和I/O放置的解决方案,则放置程序会报告违反的放置规则,并简要描述了受影响的单元格。安置可能会因为以下几个原因而失败:

•冲突约束导致的时钟树问题

•时钟树问题过于复杂,砂矿商无法解决

•RAM和DSP块的放置与其他约束冲突,如Pb块

•资源过度利用

•I/O银行要求和规则

在某些情况下,Vivado放置器会临时在现场放置细胞,并试图放置其他细胞单元,因为它试图解决放置问题。临时安置往往会确定时钟和I/O放置故障的来源。手动放置临时失败的单元格放置可能有助于放置收敛。

提示:首先使用place_ports运行时钟和I/O放置步骤。然后运行place_design。如果端口放置失败,放置为

全局布局、详细布局和布局后优化

在时钟和I/O放置之后,剩余的放置阶段包括全局放置,详细放置和放置后优化。

Global Placement

全球布局包括两个主要阶段:布局规划和物理合成。

平面布置阶段

在布局规划过程中,将设计划分为相关逻辑和初始位置的集群是基于I/O和时钟资源的放置来选择的。Pblock约束被视为即使将IS_SOFT属性设置为True。针对SSI时该设计还被划分为不同的SLR,以最大限度地减少SLR交叉及其相关的延迟处罚。可以应用软SLR平面布置图约束来指导逻辑在此阶段进行分区。有关使用软SLR平面图约束的更多信息,请参阅《FPGA和SoC的超快设计方法指南》(UG949)。

物理合成阶段

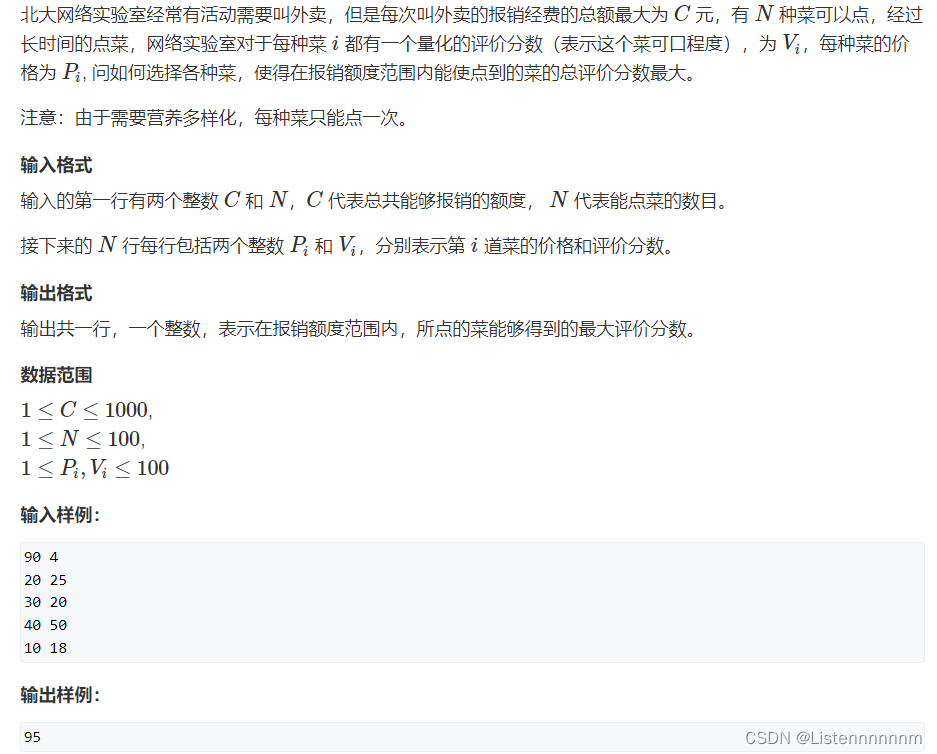

在物理合成过程中,放置器可以执行各种物理优化基于之后设计的初始布局,优化网表以用于后续布局阶段平面布置阶段。例如,对于基于扇出的复制,复制的驱动程序可以与其负载位于同一位置,因为初始位置是已知的。这可以缓解拥堵在之前不知道放置的情况下进行复制时引入place_design。优化是基于内部参数和时间来考虑的基于优化,如果时间为改进。如中所示,提供了以下优化,如下图所示。

•LUT分解和组合:如果LUT分解有所改善,则会破坏LUT形状定时(仅考虑具有SOFT_LUTNM属性的LUT)。LUT组合组合LUT,如果它提高了利用率。

•基于属性的重定时:基于属性的重新定时通过在寄存器或LUT上设置属性。这种优化非常适合具有在计时起点或终点上有足够的裕度。两个属性控制PSIP中的重定时。值为TRUE的PSIP_RETIMING_BACKWARD执行反向重定时,并且值为TRUE的PSIP_RETIMING_FORWARD执行正向重定时。属性可以应用于寄存器或LUT。当值为TRUE的PSIP_RETIMING_FORWARD为施加到寄存器,PSIP在由的Q引脚驱动的所有LUT负载上正向重定时登记当具有值TRUE的PSIP_ RETIMING_,驱动LUT的寄存器将被移动到LUT的输出。

当值为TRUE的PSIP_RETIMING_BACKWARD应用于LUT基元时由LUT驱动的寄存器将被移动到LUT输入。支持多级重定时将所述特性应用于沿着所述路径的所有LUT基元。所有重定时的单元格都将具有PHYS_OPT_MODIFIED属性设置为RETIMING。以下情况不适用于退休:

•在宏之间移动逻辑,如BRAM、UltraRAM和DSP

•在I/O站点中打包注册

•具有不同起点/终点时钟的路径

•有定时例外的路径

•阻止优化的属性,如DONT_TOUCH、ASYNC_REG等。

•极高扇出优化:极高扇出最优化复制寄存器驱动高扇出网(扇出>1000,松弛<2.0 ns)。

•关键细胞优化:关键细胞优化在故障路径中复制细胞。如果特定单元格上的负载相距很远,该单元格可能会使用新的驱动程序进行复制放置得更靠近负载集群。这种优化通常适用于驱动大块RAM的网络或URAM阵列或大量DSP,因为这些块的位置分布在更宽的范围内设备的区域。这种优化不需要高扇出(间隙<0.5ns)。

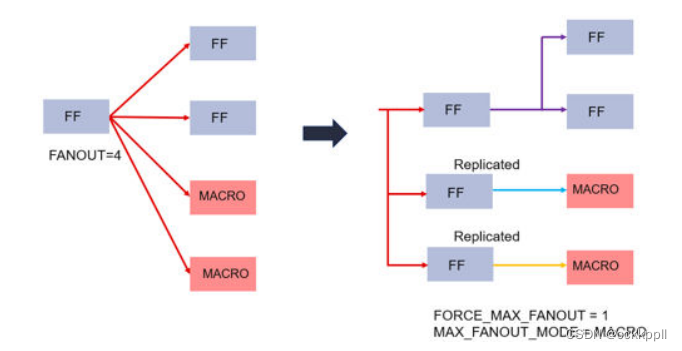

•扇出优化:MAX_Fanout属性值小于实际值的网络网络的扇出被考虑用于扇出优化。用户可以强制复制通过将FORCE_ MAX_。FORCE_MAX_FANOUT的值指定网络的最大物理扇出应该在复制优化后进行。在这种情况下,物理扇出是指实际的站点引脚负载,而不是逻辑负载。例如,如果复制副本驱动多个LUTRAM所有分组在同一切片中的负载,所有的组合扇出将为1同一切片中的LUTRAM。FORCE_MAX_FANOUT在物理过程中强制复制合成,而不管信号的松弛。用户可以基于物理具有MAX_FANOUT_MODE属性的设备属性。该物业可以承担CLOCK_REGION、SLR或MACRO的值。例如,MAX_FANOUT_MODE特性值为CLOCK_REGION的情况下,基于物理时钟区域复制驱动器放置在同一时钟区域中的负载将聚集在一起。MAX_FANOUT_MODE属性优先于FORCE_MAX_FANOUT属性和物理合成将尝试通过首先应用基于MAX_FANOUT_MODE的优化,然后全部其复制的驱动程序将继承FORCE_MAX_FANOUT属性以进行进一步的复制在时钟区域内。下图示例中说明了这一点,其中寄存器驱动四个载荷;两个寄存器和两个MACRO负载(块RAM、UltraRAM或DSP)。复制为寄存器加载和MACRO加载提供单独的驱动程序,然后为将复制MACRO加载,直到满足FORCE_MAX_FANOUT属性值。

注意:此优化发生在砂矿的早期。在放置器的后期阶段作为时间精度提高,复制的源寄存器和/或加载寄存器都可以移动到不同的时钟区域或SLR。

•DSP寄存器优化:DSP寄存器优化可以将寄存器移出DSP单元进入逻辑阵列或从逻辑到DSP单元,如果它改善了关键路径上的延迟的话。

•移位寄存器到流水线优化:移位寄存器到管线优化转换移位将具有固定长度的寄存器添加到动态调整的寄存器管道并放置管道以最佳方式改善定时。仅PHYS_SRL2PPIPELINE属性设置为TRUE的SRL被考虑用于该优化。FF的拉动/推动发生在SRL的Q引脚上。这个SRL长度需要固定,并且此优化不支持动态SRL。

•移位寄存器优化:移位寄存器优化改善了负间隙的定时移位寄存器单元(SRL)和其他逻辑单元之间的路径。

•块RAM寄存器优化:块RAM寄存器的优化可以将寄存器移出将块RAM单元转换为逻辑阵列或从逻辑转换为块RAM单元(如果它改进了关键路径上的延迟。

•URAM寄存器优化:UltraRAM寄存器优化可以将寄存器移出UltraRAM单元插入逻辑阵列或从逻辑单元到UltraRAM单元(如果它改善了上的延迟)关键路径。

•动态/静态区域接口网络复制:优化以在静态上复制驱动程序DFX流中可重构模块边界路径的设计。

•等效驱动器重新布线优化:此优化在以最小化路由重叠并提供驱动器和负载的更优化的协同定位。这有助于减少利用率和拥塞,并允许以后放置阶段,以更优化地移动驱动器和负载,从而提高QoR。有关这些优化的更多信息,请参阅物理优化部分。砂矿中的物理合成默认在所有砂矿中运行指令。在物理合成阶段结束时,一个表显示了优化。