冯·诺依曼结构计算机

1.冯·诺依曼结构计算机中数据采用二进制编码表示,其主要原因是()。

I.二进制的运算规则简单

Ⅱ.制造两个稳态的物理器件较容易

Ⅲ.便于用逻辑门电路实现算术运算

A.仅I、Ⅱ

B.仅I、Ⅲ

C.仅Ⅱ、Ⅲ

D.I、Ⅱ和Ⅲ

解析:

在冯·诺依曼结构的计算机中,数据确实是采用二进制编码来表示的。选择二进制的主要原因包括:

I. 二进制的运算规则简单:二进制只有两个数字(0和1),这使得运算规则相比于其他数制更为简单。

Ⅱ. 制造两个稳态的物理器件较容易:在物理上实现只有两个状态(例如,开/关、高电压/低电压)的器件比实现多状态的器件要容易得多。

Ⅲ. 便于用逻辑门电路实现算术运算:二进制系统可以简单地使用逻辑门电路进行处理,这些逻辑门(如AND, OR, NOT)是构建更复杂的算术和逻辑运算电路的基础。

因此,正确答案是:

D. I、Ⅱ和Ⅲ

笔记:

冯·诺依曼结构的五个组成部分:

· 中央处理单元(CPU):包括控制单元(CU)和算术逻辑单元(ALU)。

· 内存(Memory):存储数据和指令。

· 输入设备(Input devices):用于数据输入。

· 输出设备(Output devices):用于信息输出。

· 存储器总线(Buses):连接CPU、内存和I/O设备,用于组件之间的数据传输。

存储程序概念:

指令和数据以相同的格式存储在内存中,并且指令可以像数据一样被读取和写入。

顺序执行指令:

指令通常按照存储的顺序执行,除非显式地通过跳转或分支指令改变执行顺序。

二进制表示:

数据和指令都用二进制形式表示,这是由于二进制简单、易于电子实现和逻辑设计。

寄存器的作用:

包括累加器(ACC)、指令寄存器(IR)、程序计数器(PC)、存储地址寄存器(MAR)、存储数据寄存器(MDR)等,它们在CPU中快速处理和存储临时数据。

运算过程:

CPU的算术逻辑单元(ALU)执行算术运算和逻辑运算,而控制单元(CU)解析和执行指令。

2.下列关于冯·诺依曼结构计算机基本思想的叙述中,错误的是()。

A.程序的功能都通过中央处理器执行指令实现

B.指令和数据都用二进制表示,形式上无差别

C.指令按地址访问,数据都在指令中直接给出

D.程序执行前,指令和数据需预先存放在存储器中

解析:

在冯·诺依曼结构中,数据通常不是直接在指令中给出的。而是通过指令指定数据的地址来访问存储器中的数据。这种方式称为存储器寻址。指令包含操作码(指定要执行的操作类型)和操作数(通常是数据或数据的地址信息)。数据可以存放在寄存器、内存单元或其他存储设备中,并通过指令中提供的地址来访问。

故,选项C是错误的,其他选项是正确的。

笔记:

冯·诺依曼结构的指令和数据处理要点:

· 数据不是在指令中直接给出,而是通过指令中的地址来访问存储器中的数据,这是存储器寻址的过程。

· 指令由操作码(定义操作类型)和操作数(通常指地址)组成。

· 数据可以存于寄存器、内存或其他存储设备中,并通过指令提供的地址被访问。

冯·诺依曼结构的指令和数据处理核心要点:

它采用存储程序控制,指令和数据以二进制形式存储在同一内存中,并通过中央处理单元以顺序方式执行。

存储器的地址编址方式

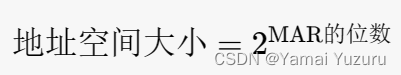

3.某CPU内部的MAR寄存器的位数为10,输出10位地址信息。它的MDR是16位,对外数据线是16根,该CPU可以直接访问的存储器的地址空间是(),按字节寻址的容量为(),按字寻址的容量为()

解析:

MAR(Memory Address Register,内存地址寄存器)的位数决定了CPU可以寻址的内存地址空间大小。MAR是10位,意味着它可以输出 2^10 个不同的地址信息,即可以直接访问的存储器地址空间为:

2^10 =1024 个地址

这个地址空间的大小是指它可以区分的不同内存位置的数量。

MDR(Memory Data Register,内存数据寄存器)通常与CPU的数据总线宽度相匹配,用于存储和内存交换的数据。在这个情况下,MDR是16位宽,对应的数据线也是16根。这意味着CPU每次可以读取或写入16位(即2字节)的数据。

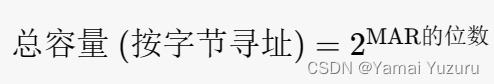

按字节寻址时,每个内存地址对应于1个字节,所以按字节寻址的容量是MAR能够寻址的地址数乘以每个地址的字节数:

1024 个地址×1 字节/地址=1024 字节=1 千字节 (KB)

按字寻址时,如果每个“字”等于MDR的宽度,即16位或2字节,那么按字寻址的容量将是MAR寻址的地址数乘以每个地址的字节数:

1024 个地址×2 字节/地址=2048 字节=2 千字节 (KB)

综上所述,该CPU可以直接访问的存储器的地址空间是1024个地址,按字节寻址的容量为1KB,按字寻址的容量为2KB。

笔记:

数据总线宽度(MDR的宽度)影响的是数据的传输效率,而不是可寻址的内存容量。

![]()

4.下列给出的部件中,其位数(宽度)一定与机器字长

相同的是()。

I.ALU

Ⅱ.指令寄存器

Ⅲ.通用寄存器

IV.浮点寄存器

A.仅I、Ⅱ

B.仅I、Ⅲ

C.仅Ⅱ、Ⅲ

D.仅Ⅱ、Ⅲ、IV

解析:

机器字长是指计算机用于一次性处理数据的标准大小,这通常与最基本的操作单元有关,如ALU(算术逻辑单元)操作的数据宽度,以及通用寄存器的大小。指令寄存器通常存储当前执行的指令,其大小不一定与机器字长相同,因为指令的长度可能与机器字长不同,取决于计算机的指令集架构。浮点寄存器用于存储浮点数,其大小也可能与机器字长不同,因为浮点数的标准大小可能不同于整数或其他数据类型的机器字长。

因此,与机器字长一定相同的部件是:

I. ALU(算术逻辑单元) - 因为ALU执行的操作通常处理的是完整的机器字长的数据。

III. 通用寄存器 - 通用寄存器通常用来存储和操作机器字长的数据。

选项中提供的浮点寄存器,它们可能与机器字长不同,因为浮点数的表示通常有专门的标准,并且可能需要比整数更多的位来表示。

故正确答案是:

B. 仅I、Ⅲ

笔记:

用A来代表ALU,R来代表寄存器,然后记住“AR同长”(ALU和通用寄存器与机器字长相同)。

对于指令寄存器和浮点寄存器,可以考虑它们的特殊用途,这就意味着它们可能有特殊的设计,与机器字长不一定相同。

补充:

指令寄存器(IR)

指令寄存器的特殊用途在于:

存储当前执行的指令:指令寄存器用来临时存储从内存取出的当前指令。这是执行指令周期的一个重要步骤。

指令长度多样性:在许多架构中,指令的长度可以多样化。有的指令集支持固定长度的指令,而有的支持可变长度。因此,指令寄存器的大小需要能够容纳最长的指令,而这个尺寸可能与机器字长不同。

浮点寄存器(FPR)

浮点寄存器的特殊用途包括:

存储浮点数:浮点寄存器专门用于在算术运算中存储和处理浮点数(实数),它们通常按照特定的浮点数标准(如IEEE 754)设计。

精度要求:浮点数的表示需要更高的精度,可能需要单精度(32位)或双精度(64位)甚至更高,以便精确表示小数点后的数值。这些精度要求可能导致浮点寄存器的大小超过了常规的整数机器字长。

存储器的数据存储

5.某计算机字长为32位,按字节编址,采用小端(Little Endian)方式存放数据。假定有一个double型变量,其机器数表示为1122 3344 5566 7788H,存放在00008040H开始的连续存储单元中,则存储单元00008046H中存放的是()。

A.22H

B.33H

C.66H

D.77H

解析:

在本题的上下文中,"按字节编址" 表明:

内存中每个字节都有一个独立的地址。

当存放一个数据(如题中的 double 类型变量)时,该数据将被分割成多个字节,并且这些字节将被顺序地存放在一系列连续的地址中。

对于一个32位系统来说,尽管字长为32位,但是按字节编址仍然允许每个独立的8位(1字节)单元被单独寻址。因此,在本题中,一个64位的 double 类型变量(占用8字节)将被分散存储到8个连续的字节地址中。

在本题的上下文中, "其机器数表示为1122334455667788H" 表明:

一个 double 类型的变量在计算机内存中以16进制数 1122334455667788 的形式存储。这里的 H 通常表示随后的数是十六进制格式。在计算机系统中,十六进制经常用于表示二进制数,因为它更加紧凑且易于转换(每4位二进制数对应1位十六进制数)。

在本题的上下文中, “采用小端(Little Endian)方式存放数据”表明:

在小端(Little Endian)模式下,数据的低位字节存放在起始地址,高位字节存放在更高的地址。因此,对于一个double型变量(假设在这种计算机中占用8个字节,即64位),其机器数表示为1122334455667788H将会按照如下方式存放:

低地址 -----------------> 高地址

88 77 66 55 44 33 22 11 (十六进制表示)

如果变量的起始地址是00008040H,则各字节存放的地址如下:

00008040H: 88H

00008041H: 77H

00008042H: 66H

00008043H: 55H

00008044H: 44H

00008045H: 33H

00008046H: 22H

00008047H: 11H

所以,存储单元00008046H中存放的是22H。

笔记:

在小端(Little Endian)模式下,数据的最低有效字节存放在最低的地址,而最高有效字节存放在最高的地址。

<-------小端

------------------------------------------------

机器数(分割后)

[低地址 -> 高地址]

[如0000 -> 0003]

------------------------------------------------

大端 ------->补充:

考虑一个4字节的32位数值 AABBCCDDH。

在小端模式下,存储顺序(从起始地址开始)将是 DD CC BB AA:

地址 数据

低地址 -> 高地址

0000 DD

0001 CC

0002 BB

0003 AA

在大端模式下,存储顺序将是 AA BB CC DD:

地址 数据

低地址 -> 高地址

0000 AA

0001 BB

0002 CC

0003 DD 6.某计算机存储器按字节编址,采用小端方式存放数据。假定编译器规定int型和short型长度分别为32位和16位,并且数据按边界对齐存储。某C语言程序段如下:

struct{

int a;

char b;

short c;

} record;

record.a=273;

若record变量的首地址为0xC008,则地址0xC008中内容及record.c的地址分别为()。

A.0x00、0xC00D

B.0x00、0xC00E

C.0x11、0xC00D

D.0x11、0xC00E

解析:

首先,我们需要理解题目中给出的结构体 record 的成员变量在内存中是如何对齐的。按照题目描述,结构体包含一个 int 类型的 a(占用4个字节,即32位)、一个 char 类型的 b(占用1个字节)、和一个 short 类型的 c(占用2个字节,即16位)。

小端字节序(Little Endian)只影响多字节数据类型(如 int、short、long、float、double 等)在内存中的字节顺序,而不影响结构体中字段的存储顺序。结构体中的字段按照它们在代码中定义的顺序依次存储在内存中,但字段内部的字节顺序会受到所采用的字节序模式的影响。

对于上面的例子,record 结构体中的字段 a、b 和 c 会按照它们在结构体中定义的顺序顺序存储,但是字段 a 和字段 c(如果它们的值超过了一个字节)的内部字节顺序会按照小端模式存储。具体来说:

对于 int a,如果 a 的值是 273(十进制),在内存中小端表示为:

273的十进制 = 1 * 256 + 1 * 16 + 1 = 256 + 16 + 1 = 273

273的十六进制 = 0x0111这个十六进制数要在内存中以小端顺序存储,所以低地址端存放 0x10,紧接着是 0x01,在 4 字节的 int 中,其余字节填充为 0x00,具体如下:

0xC008: 0x11

0xC009: 0x01

0xC00A: 0x00

0xC00B: 0x00对于 char b,它是单个字节,所以不受字节序的影响,直接按顺序存储。

对于 short c,如果给定了值,它在内存中的存储也会受到小端字节序的影响,就是说其内部的字节顺序会是低字节在前,高字节在后。

结构体字段的存储顺序与字节序无关,但每个字段的内部字节存储顺序会受到字节序的影响。

地址 内容

0xC008 record.a 的第一个字节

0xC009 record.a 的第二个字节

0xC00A record.a 的第三个字节

0xC00B record.a 的第四个字节

0xC00C record.b

0xC00D 填充,为了使 record.c 对齐

0xC00E record.c 的第一个字节

0xC00F record.c 的第二个字节笔记:

在小端模式下,结构体字段按照定义顺序连续存储,但多字节类型字段内部的字节顺序是反的(即低位字节存储在起始的低地址),并且可能会有对齐填充以满足数据类型的对齐要求。