嵌入式系统的基本素养包括以下几个方面:

-

硬件知识:嵌入式系统通常由硬件和软件组成,了解和熟悉硬件的基本知识,包括微处理器、存储器、外设等,并了解它们的工作原理和特性。

-

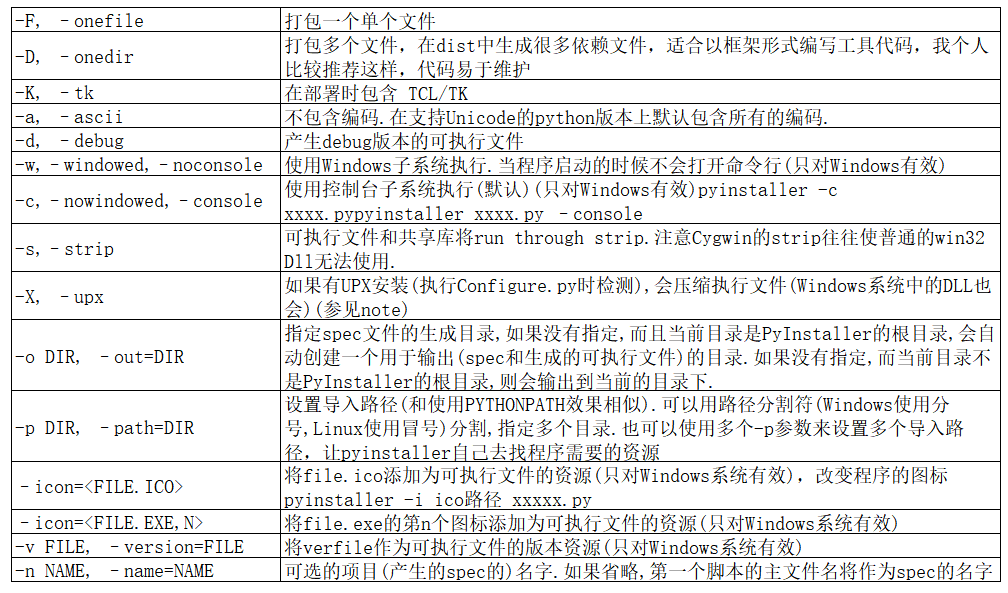

软件编程:熟悉至少一种编程语言,如C/C++,并具备良好的编程能力。嵌入式系统通常需要编写底层驱动程序、中间件和应用程序等,具备嵌入式软件开发经验和技能。

-

系统设计能力:了解嵌入式系统的整体架构和设计原理,能够根据需求和约束进行系统设计,并能够对系统进行性能优化和资源管理。

-

实时系统知识:嵌入式系统通常需要实时响应和处理数据,因此了解实时系统的基本概念和原理,掌握实时任务调度算法和实时性分析方法等是必要的。

-

通信协议和接口:掌握常用的通信协议和接口标准,如UART、SPI、I2C、CAN、Ethernet等,并能够进行数据传输和通信。

-

调试和故障排除能力:嵌入式系统常常会遇到各种问题和故障,因此要具备良好的调试和故障排除能力,善于使用各种工具和仪器进行调试和分析。

-

学习和研究能力:嵌入式系统技术发展迅速,新的硬件和软件技术不断涌现,掌握学习和研究的方法,能够持续学习和跟进最新的嵌入式技术是非常重要的。

总之,嵌入式系统的基本素养要包括硬件知识、软件编程、系统设计、实时系统、通信协议和接口、调试和故障排除能力以及学习和研究能力等方面的知识和技能。

政安晨的个人主页:政安晨

欢迎 👍点赞✍评论⭐收藏

收录专栏: 机器学习智能硬件开发全解

希望政安晨的博客能够对您有所裨益,如有不足之处,欢迎在评论区提出指正!

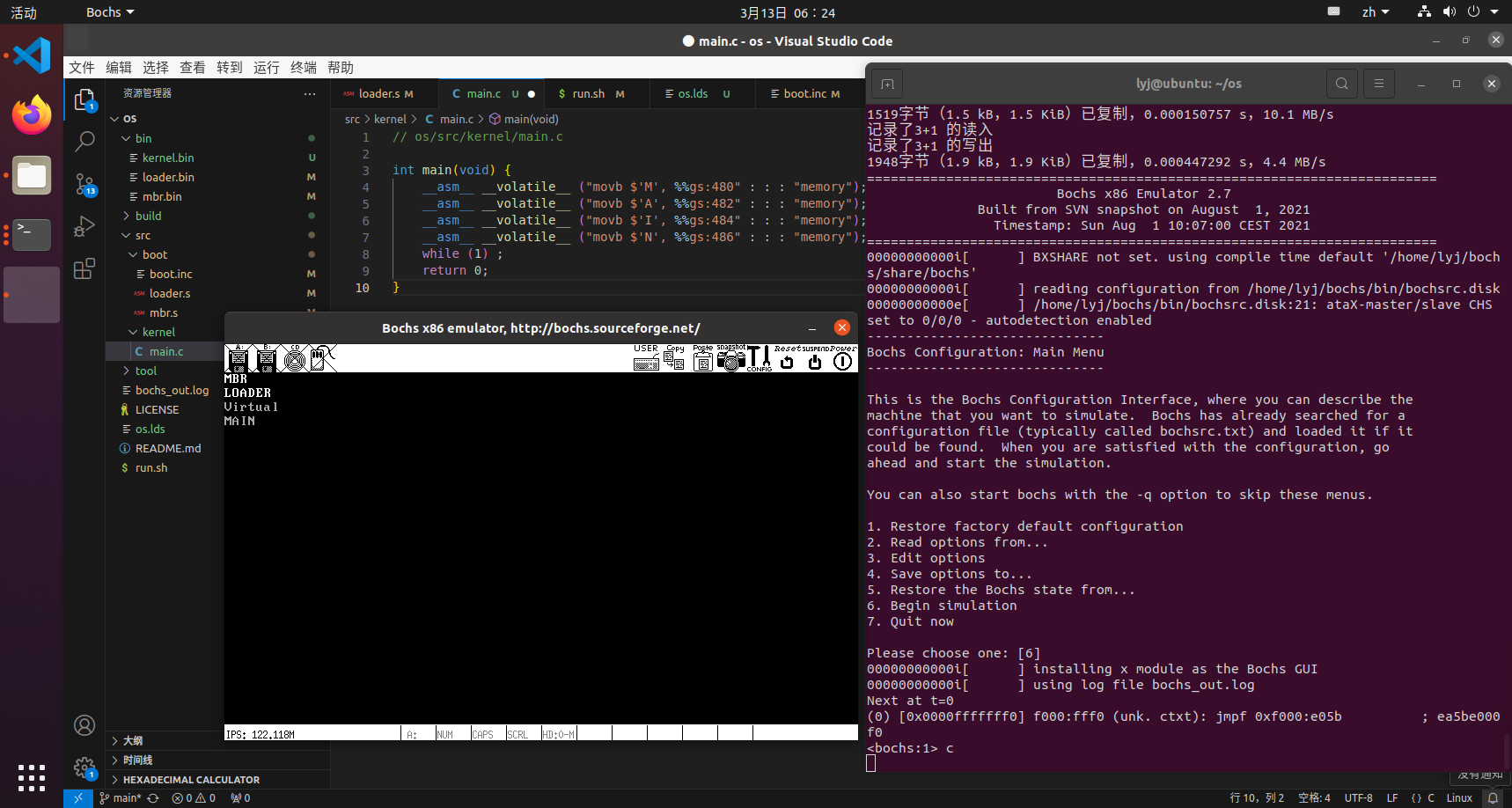

技术体系结构

嵌入式开发很大一部分工作跟底层紧密相关,如系统移植、BSP开发、驱动开发等,和芯片、硬件、以及算法、中间件、系统打交道的地方都比较多。

要想成为一名真正的嵌入式工程师,除了要精通C语言编程,还要对计算机原理和系统结构、CPU工作原理、相关编程语言、硬件电路、通信协议、操作系统、验证测试等相关知识和理论有一定的掌握。

在这篇文章中,咱们重点掌握处理器工作原理,因为CPU在处理器中比较典型,嵌入式系统中MCU本质上也是通用CPU处理器的简化版,咱们接下来可以用CPU为例,重点理解。

掌握这类技术体系结构的好处如下:

掌握了CPU的工作原理,可以更好地理解指令到底是如何执行的;

掌握计算机的工作原理和系统结构,可以更好地理解程序的编译、链接、安装和运行机制;

掌握一门汇编语言,可以从底层的角度去看C语言,可以帮助我们更好地理解C语言。我们编写的C程序,最终都会转换成CPU所支持的二进制指令,而汇编语言又是这些指令集的助记符,通过反汇编代码,我们可以更加深刻地理解编译器的特性和C语言的语法。

如果你在芯片原厂从事嵌入式研发工作,可能还要和一帮IC工程师、硬件工程师打交道,和他们一起解决芯片、硬件电路中的各种问题。为了更好地和他们沟通,你可能还需要对半导体知识、IC行业的专业术语有一定的了解,如逻辑综合、前端设计、后端设计、仿真验证等。

本着直达本质的探究精神,咱们这篇文章打算从半导体工艺开始,给大家科普一下CPU的制造过程,科普一下一款处理器是如何从一堆沙子变成市场上销售的芯片的,以及CPU的工作原理和计算机体系结构的相关知识。

希望通过咱们这篇文章的学习,让大家对半导体工艺、芯片、CPU、指令集、微架构、计算机系统架构、总线与地址等有一个完整的认知框架,为后续的学习打下基础。

处理器是怎样诞生的

处理器是一类芯片,芯片属于半导体,半导体是介于导体和绝缘体之间的一类物质,元素周期表中硅、锗、硒、硼的单质都属于半导体。

这些单质通过掺杂其他元素生成的一些化合物,也属于半导体的范畴。

这些化合物在常温下可激发载流子的能力大增,导电能力大大增强,弥补了单质的一些缺点,因此在半导体行业中广泛应用,如氮化硅、砷化镓、磷化铟、氮化镓等。

在这些半导体材料中,目前只有硅在集成电路中大规模应用,充当着集成电路的原材料。

在自然界中,硅是含量第二丰富的元素,如沙子,就含有大量的二氧化硅。

可以说制造芯片的原材料是极其丰富、取之不尽的:

一堆沙子,可以和水泥做搭档,沉寂于一座座高楼大厦、公路桥梁之中;

也可以在高温中凤凰涅槃、浴火重生,变成集成电路高科技产品。到底要经过怎样奇妙的变化,才能让一堆沙子变成一颗颗芯片呢?

从沙子到单晶硅

如何从沙子中提取单晶硅呢?沙子的主要成分是二氧化硅,这就涉及一系列化学反应了,其中最主要的过程就是使用碳经过化学反应将二氧化硅还原成硅。

经过还原反应生成的硅叫粗硅,粗硅里面包含很多杂质,如铁、碳元素,还达不到制造芯片需要的纯度(需要99.999999999%以上)标准,需要进一步提纯。提纯也需要一系列化学反应,如通过盐酸氯化、蒸馏等步骤。提取的硅纯度越高,质量也就越高。

经过一系列化学反应、提纯后生成的硅是多晶硅。将生成的多晶硅放入高温反应炉中融化,通过拉晶做出单晶硅棒。

如下图所示:

为了增强硅的导电性能,一般会在多晶硅中掺杂一些硼元素或磷元素,待多晶硅融化后,在溶液中加入硅晶体晶种,同时通过拉杆不停旋转上拉,就可以拉出圆柱形的单晶硅棒。根据不同的需求和工艺,单晶硅棒可以做成不同的尺寸,如常见的6寸、8寸、12寸等。

接下来,将这些单晶硅棒像切黄瓜一样,切成一片一片的,每一片我们称为晶圆(wafer)。晶圆是设计集成电路的载体,我们设计的模拟电路或数字电路,最终都要在晶圆上实现。

晶圆上的芯片电路尺寸随着半导体工艺的发展也变得越来越小,目前已经达到了纳米级,越来越精密的半导体工艺除了要求单晶硅的纯度极高,晶圆的表面也必须光滑平整,切好的晶圆还需要进一步打磨抛光。

晶圆表面需要光滑平整到什么程度呢?

打个比方,假如需要从北京到上海铺设一段铁轨,对铁轨的要求就是两者之间的高度差不超过1mm。一粒灰尘落在晶圆上,就好像一块大石头落在马路上一样,会对芯片的良品率产生很大的影响,所以大家会看到芯片的生产车间对空气的洁净度要求非常高,员工必须穿着防尘服才能进入。在每一个晶圆上,都可以实现成千上万个芯片电路,如下图所示:

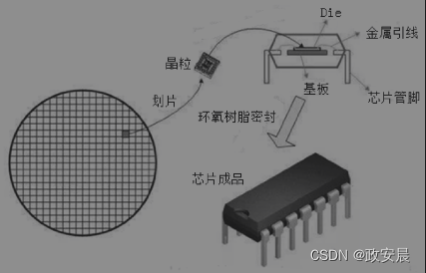

晶圆上的每一个小格子都是一个芯片电路的物理实现,我们称之为晶粒(Die)。

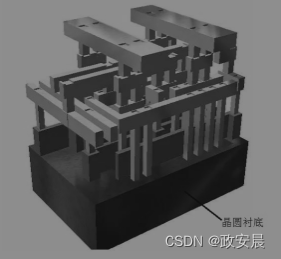

接下来还要对晶圆上的这些芯片电路进行切割、封装、引出管脚,然后就变成了市场上常见的芯片产品,最后才能焊接到我们的电路板上,做成整机产品,如下图所示:

在一个晶圆上是如何实现电路的呢?将晶圆拿到显微镜下观察,你会发现,在晶圆的表面上全是纵横交错的3D电路,犹如一座巨大的迷宫,如下图所示:

要想弄明白在晶圆上是如何实现我们设计的电路的,就需要先了解一下电子电路和半导体工艺的知识:

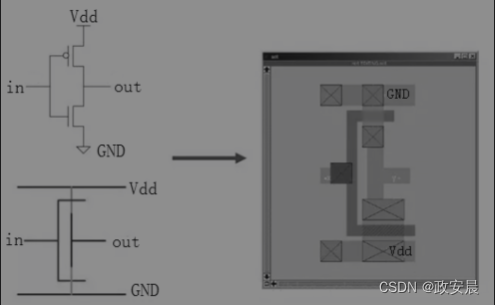

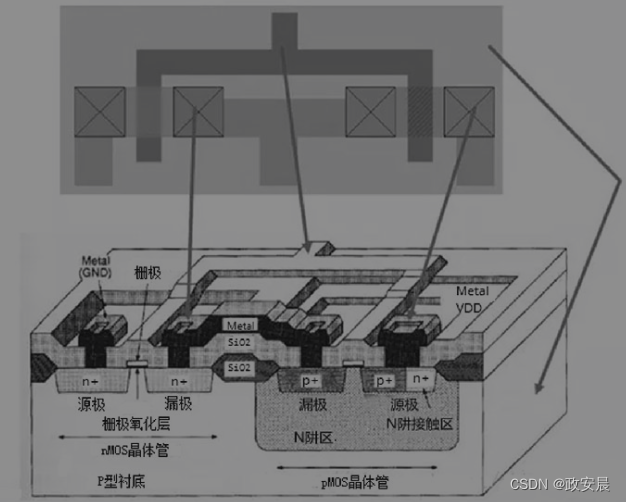

电路一般由大量的三极管、二极管、CMOS管、电阻、电容、电感、导线等组成,我们搞懂了一个CMOS元器件在晶圆上是如何实现的,基本上也就搞懂了整个电路在晶圆硅片上是如何实现的。

这些电子元器件的实现原理,其实就是PN结的实现原理。

PN结是构成二极管、三极管、CMOS管等半导体元器件的基础。

PN结的工作原理

想要了解PN结的导电原理,还得从金属的导电原理说起。

一个原子由质子、中子和核外电子组成。中子不带电,质子带正电,核外电子带负电,整个原子显中性。根据电子的能级分布,一个原子的最外层电子数为8时最稳定。如钠原子,核外电子层分布为2—8—1,最外层1个电子,能量最大、受原子核的约束力小,所以最不稳定,受到激发容易发生跃迁,脱离钠原子,成为自由移动的电子。这些自由移动的电子在电场的作用下,会发生定向移动形成电流,这就是金属导电的原理。很多金属原子的最外层电子数小于4,容易丢失电子,称为自由移动的电子,所以金属容易导电,是导体。而对于氯原子,最外层有7个电子,倾向于从别处捕获一个电子,形成最外层8个电子的稳定结构,氯原子因为不能产生自由移动的电子,所以不能导电,是绝缘体。

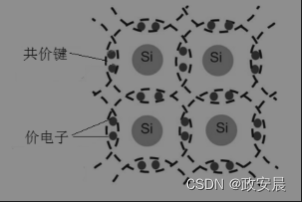

半导体元素,一般最外层有4个电子,情况就变得比较特殊:这些原子之间往往通过“共享电子”的模式存在,多个原子之间分别共享其最外层的电子,通过共价键形成最外层8个电子的稳定结构,如下图所示(硅原子之间的共价键):

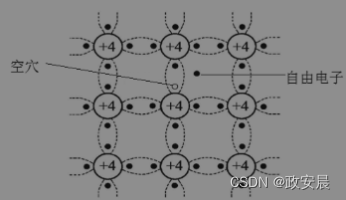

这种稳定也不是绝对的,当这些电子受到能量激发时,如下图所示,也会有一部分发生跃迁,成为自由移动的电子,同时在共价键中留下同等数量的空穴。

(自由电子和空穴的产生)

这些自由移动的电子虽然非常少,但是在电场的作用下,也会发生定向移动,形成电流。电子的移动产生了空穴,临近的电子也很容易跳过去填补这个空穴,产生一个新的空穴,造成空穴的移动。空穴带正电荷,空穴的移动和自由电子的移动一样,也会产生电流。

金属靠自由电子的移动产生电流导电,而半导体则有两种载流子:自由电子和空穴。但是由于硅原子比较稳定,只能生成极少数的自由电子和空穴,这就决定了硅无法像金属那样导电,但也不像绝缘体那样一点也不导电,因此我们称之为半导体。正是由于硅的这种特性,才有了半导体的飞速发展。

既然半导体内自由电子和空穴浓度很小,导电能力弱,那我们能不能想办法增加这两种载流子的浓度呢?载流子的浓度上去了,导电能力不就增强了吗?只要有利润空间,办法总是有的,那就是掺杂。我们可以在一块半导体两边分别掺入两种不同的元素:一边掺入三价元素,如硼、铝等;另一边掺入五价元素,如磷。

硼原子的电子分布为2—3,最外层有3个电子。如下图所示,在和硅原子的最外层4个电子生成共价键时,由于缺少一个电子,于是从临近的硅原子中夺取一个电子,因而产生一个空穴位。每掺杂一个硼原子,就会产生一个空穴位,这种掺杂三价元素的半导体增加了空穴的浓度,我们一般称之为空穴型半导体,或称P型半导体。

(掺杂硼元素的P型半导体)

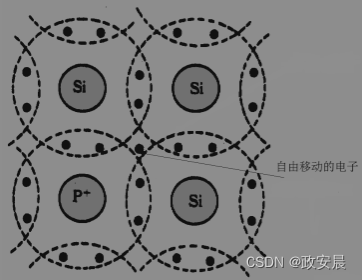

磷原子的最外层有5个电子,如下图所示,在和硅原子的最外层4个电子生成共价键时,还多出来一个电子,成为自由移动的电子。每掺杂一个磷原子,就会产生一个自由移动的电子。这种掺杂五价元素的半导体增加了自由电子的浓度,我们一般称之为电子型半导体,或称N型半导体。

(掺杂磷元素的N型半导体)

我们在一块半导体的两边分别掺入不同的元素,使之成为不同的半导体,如下图所示,一边为P型,一边为N型。在两者的交汇处,就会形成一个特殊的界面,我们称之为PN结。理解了PN结的工作原理,也就理解了半导体器件的核心工作原理。接下来我们就看看PN结到底有什么名堂。

(PN结两边的自由电子、空穴分布)

掺杂不同元素的半导体两边由于空穴和自由电子的浓度不同,因此在边界处会发生相互扩散:空穴和自由电子会分别越过边界,扩散到对方区域,并与对方区域里的自由电子、空穴在边界附近互相中和掉。如下图所示,P区边界处的空穴被扩散过来的自由电子中和掉后,剩下的都是不能自由移动的负离子,而在N区边界处留下的则是正离子。这些带电的正、负离子由于不能移动,就会在边界附近形成了耗尽层,同时会在这个区域内生成一个内建电场。

(PN结区域的内建电场)

这个内建电场会阻止P区的空穴继续向N区扩散,同时也会阻止N区的自由电子继续向P区扩散,空穴的扩散和自由电子的漂移从而达到一个新平衡,这个区域就是我们所说的PN结:载流子的移动此时已达到动态平衡,因此流过PN结的电流也变为0。这个PN结看起来也没什么,但它有一个特性:单向导电性。正是这个特性确立了它在电路中的重要地位,也构成了整个半导体“物理大厦”的核心基础。

我们先来看看这个特性是怎么实现的:在上图中,当我们在PN结两端加正向电压时,即P区接正极,N区接负极,此时就会削弱PN结的内建电场,平衡被打破,空穴和自由电子分别向两边扩散,形成电流,半导体呈导电特性。当我们在PN结两端加反向电压时,内建电场增强,此时会进一步阻止空穴和自由电子的扩散,不会形成电流,半导体呈现高阻特性,不导电。

从PN结到芯片电路

无论二极管、三极管还是MOSFET场效应管,其内部都是基于PN结原理实现的。通过上面部分,我们已经了解了PN结的工作原理,接下来我们就看看如何在一个晶圆上实现PN结。PN结的实现会涉及半导体工艺的方方面面,包括氧化、光刻、显影、刻蚀、扩散、离子注入、薄膜沉淀、金属化等主要流程。

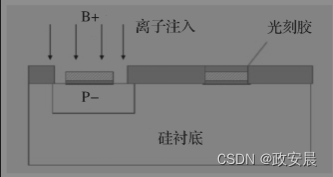

为了简化流程,方便理解,我们就讲讲两个核心的步骤:离子注入和光刻。离子注入其实就是掺杂,如下图所示,就是往单质硅中掺入三价元素硼和五价元素磷,进而生成由PN结构成的各种元器件和电路。而光刻则是在晶圆上给离子注入开凿各种掺杂的窗口。

(通过光刻胶制作掺杂窗口)

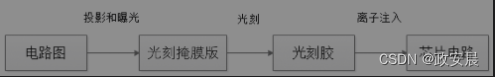

在晶圆上进行离子注入掺杂之前,首先要根据电路版图制作一个个掺杂窗口,如下图所示,这一步需要光刻胶来协助完成:在硅衬底上涂上一层光刻胶,通过紫外线照射掩膜版,将电路图形投影到光刻胶上,生成一个个掺杂窗口,并将不需要掺杂的区域保护起来。那如何产生这个掺杂窗口呢?原理很简单,就和我们使用感光胶片去洗照片一样,还需要一个叫作光刻掩膜版的东西。

光刻掩膜版原理和我们照相用的胶片差不多,由透明基板和遮光膜组成,如下图所示,通过投影和曝光,我们可以将芯片的电路版图保存在掩膜版上。然后通过光刻机的紫外线照射,利用光刻胶的感光溶解特性,被电路图形遮挡的阴影部分的光刻胶保存下来,而被光照射的部分的光刻胶就会溶解,成为一个个掺杂窗口。最后通过离子注入,掺杂三价元素和五价元素,就会在晶圆的硅衬底上生成主要由PN结构成的各种CMOS管、晶体管电路。

我们设计的芯片物理版图的每一层电路,都需要制作对应的掩膜版,重复以上过程,就可以在晶圆上制作出迷宫式的3D立体电路结构。

(半导体工艺主要流程)

随着集成电路规模越来越大,在一个几英寸的晶圆硅衬底上,要实现千万门级、甚至上亿门级的电路,需要几十亿个晶体管,电路的实现难度也变得越来越大。尤其是纳米级的电路,如现在流行的14nm、7nm、5nm工艺制程,要将千万门级的晶体管电路都刻在一个指甲盖大小的硅衬底上,这就要求电路中的每个元器件尺寸都要非常小,同时要求“感光胶片”要非常精密,对电路图形的分辨率要非常高。这时候光刻机就闪亮登场了,光刻机主要用来将你设计的电路图映射到晶圆上,通过光照将你设计的电路图形投影到光刻胶上,光刻胶中被电路遮挡的部分被保留,溶解的部分就是掺杂的窗口。晶体管越多,电路越复杂,工艺制程越先进,对光刻机的要求越高,因为需要非常精密地把复杂的电路图形投影到晶圆的硅衬底上。光刻机因此也非常昂贵,如网上广泛讨论的荷兰光刻巨头ASML(阿斯麦),如下图所示,一台光刻机的售价为1亿欧元,很多芯片代工巨头,如台积电、三星、Intel、中芯国际,都是它的客户。

(ASML光刻机)

光刻机的作用是根据电路版图制作掩膜版,开凿各种掺杂窗口,然后通过离子注入,生成PN结,进而构建千千万万个元器件。将这些工艺流程走一遍之后,在一个晶圆上就生成了一个个芯片的原型:芯片电路,就如上面晶圆图所示的那样,晶圆上的每一个小格子都是一个芯片电路,这些芯片电路的专业术语叫作Die,翻译成中文叫作晶粒。

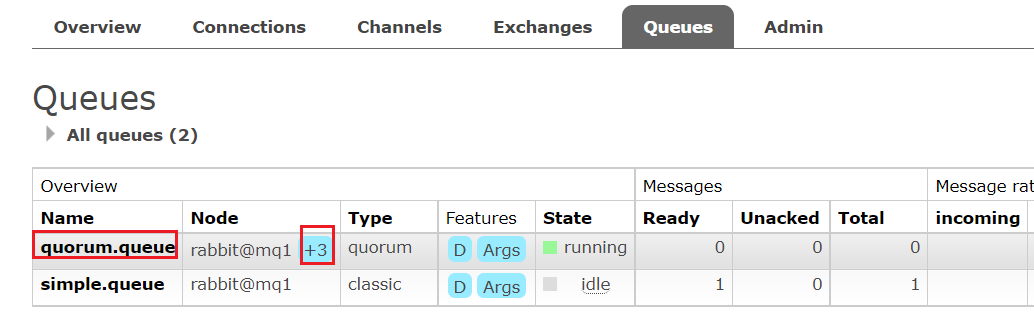

芯片的封装

单纯的芯片电路无法直接焊接到硬件电路板上,如下图所示,还需要经过切割、封装、引出管脚、芯片测试等后续流程,测试通过后经过包装,才会变成市场上我们看到的芯片的样子。

(从晶粒到芯片成品)

芯片的封装主要就是给芯片电路加一个外壳,引出管脚。芯片的封装不仅可以起到密封、保护芯片的作用,还可以通过管脚,直接将芯片焊接到电路板上。芯片的封装技术经过几十年的发展,越来越先进,芯片的面积也越来越小。常见的封装形式有DIP、QFP、BGA、CSP、MCM等。

DIP(Dual in-line Package),指采用双列直插形式封装集成电路芯片,芯片有2排管脚,可以直接插到电路板上的芯片插座上,或者插到PCB电路板上穿孔焊接,非常方便。DIP一般适用于中小规模的集成电路芯片,芯片的管脚数比较少,如下图所示,我们常见的C51单片机、早期的8086 CPU都采用这种封装。

(早期8086 CPU芯片(DIP))

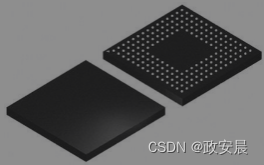

在超大规模集成电路设计中,当芯片的主频很高、芯片的管脚很多时,使用DIP就不太合适了,我们一般会使用球栅阵列封装(Ball Grid Array Package,BGA)。

如下图所示,使用BGA的芯片管脚不再从芯片周边引出,而是采用表面贴装型封装:

在印刷基板的背面按照阵列方式制作出球形凸点来代替管脚,然后将芯片电路装配到基板的正面,最后用膜压树脂或灌封方法进行密封。BGA封装适用于CPU等管脚比较多的超大规模集成电路芯片。

(BGA芯片)

芯片级封装(Chip Scale Package,CSP)是一种比较新的芯片封装技术,封装后的芯片尺寸更接近实际的芯片电路。随着电子设备越来越微型化,对芯片的面积、厚度要求也越来越高,通过CSP封装可以让芯片的封装面积和原来面积之比超过1:1.14,芯片封装的厚度也大大减小,从而缩减了芯片的体积。DIP和CSP芯片尺寸对比如下图所示:

(DIP和CSP芯片尺寸对比)

CSP可以让芯片面积减小到DIP的四分之一,同时具备信号传输延迟短、寄生参数小、电热性能更好的优势,更适合高频电路的封装。CSP技术在目前的芯片和微型电子设备中被广泛使用。

随着市场上智能手表、运动手环等智能硬件的流行,对芯片的封装尺寸也有了更严苛的要求,层叠封装(Package-on-Package,PoP)技术此时就应运而生了。PoP可以将多个芯片元器件分层堆叠、互连,封装在一个芯片内,从而让整个芯片更薄、体积更小。现在很多智能手机,为了薄化电路板,一般会将LPDDR内存芯片和eMMC存储芯片封装在一起,或者将应用处理器和基带芯片封装在一起。如苹果的iWatch,直接将应用处理器、LPDDR4X DRAM和eMMC Flash存储芯片封装在一个芯片内,大大减少了整个芯片和电路板的尺寸,然后和发动机、电池板等器件像汉堡一样三层封装在一起,可以将整个电子产品做得更加轻薄、小巧。

芯片封装好后,还要经过最后一步:测试。测试主要包括芯片功能测试、性能测试、可靠性测试等。测试的主要工作就是测试芯片的功能、指标、参数和前期的设计目标是否一致,筛选掉制造过程中有缺陷的芯片,或者根据性能对芯片进行分级,包装成不同规格等级的芯片,最终测试通过的芯片才能拿到市场上销售。

处理器是怎么设计出来的

通过刚才的文章,我们已经知道了芯片制造的基本流程:从沙子中提取硅、把硅切成片,在硅片上通过掺杂实现PN结,实现各种二极管、三极管、CMOS管,就可以将我们设计的电路图转换为千万门级的大规模集成电路。接下来我们继续了解一款CPU芯片电路是怎样设计出来的:

首先,我们需要了解一下CPU内部的结构及工作原理。想要搞懂CPU的工作原理,这里又不得不说一下图灵机。图灵机原型证明了实现通用计算机的可能性,奠定了现代计算机发展的理论基石。

计算机理论基石:图灵机

现代计算机理论的技术源头可以追溯到几十年前的图灵机。在20世纪40年代,英国科学家图灵在他发表的一篇论文中提出了图灵机的概念,大家有兴趣可以在网上搜搜这篇论文,公式很复杂,也很难看懂。我们简化分析,可以简单地理解为:任何复杂的运算都可以分解为有限个基本运算指令。

图灵机的构造如下图所示:

一条无限长的纸带Tape、一个读写头Head、一套控制规则Table、一个状态寄存器。图灵机内部有一个机器读写头Head,读写头可以一直读取纸带,图灵机根据自己有限的控制规则,根据纸带的输入,不断更新机器的状态,并将输出打印到纸带上。

(图灵机原理图)

比较图灵机原型与现代计算机,你会发现有很多相似的地方。

● 无限长的纸带:相当于程序代码。

● 一个读写头Head:相当于程序计数器PC。

● 一套控制规则Table:相当于CPU有限的指令集。

● 一个状态寄存器:相当于程序或计算机的状态输出。

不同架构的CPU,指令集不同,支持运行的机器指令也不同,但是有一条是相同的:每一种CPU只能支持有限个指令,任何复杂的运算最终都可以分解成有限个基本指令来完成:加、减、乘、除、与、或、非、移位等算术运算或逻辑运算。在个人计算机上,我们可以玩游戏、上网、聊天、听音乐、看视频,这些复杂多变的应用程序,最终都可以分解成CPU所支持的有限个基本指令,通过指令的组合运算来完成。

CPU内部结构及工作原理

基于图灵机的构想,现代计算机的基本结构就逐渐清晰了。如下图所示,CPU内部构造很简单,只包含基本的算术逻辑运算单元、控制单元、寄存器等,仅支持有限个指令。CPU支持的有限个基本指令集合,称为指令集。程序代码存储在内部存储器(内存)中,CPU可以从内存中一条一条地取指令、翻译指令并执行它。

(CPU内部结构)

CPU内部的算术逻辑单元(Arithmetic and Logic Unit,ALU)是处理器最核心的部件,相当于CPU的大脑。理解了ALU的工作流程基本上也就理解了计算机的工作流程。ALU由算术单元和逻辑单元组成,算术单元主要负责数学运算,如加、减、乘等;逻辑单元主要负责逻辑运算,如与、或、非等。

ALU只是纯粹的运算单元,要想完成一个指令运行的整个流程,还需要控制单元的协助。控制单元根据程序计数器PC中的地址,会不断地从内存RAM中取指令,放到指令寄存器中并进行译码,将指令中的操作码和操作数分别送到ALU,执行相应的运算。以两个整数A、B相加的指令为例,如上图所示,控制单元通过指令译码电路会将该指令分解为操作码和操作数,再根据操作数地址从内存RAM中加载(Load)数据A和B,传送到ALU的输入端,然后将操作运算类型(操作码)即加法也告诉ALU。ALU有了输入数据和操作类型,就可以直接进行相应的运算了,并输出运算结果。

为了效率考虑,运算结果一般会先保存到寄存器中,然后由控制单元将该数据从寄存器存储(Store)到内存RAM中。执行到这一步,一个完整的加法指令执行流程就结束了,控制单元会继续取下一条指令,然后翻译指令、运行指令,周而复始。CPU内部有个程序计数器(Program Counter,PC),系统上电后默认初始化为0,控制单元会根据这个PC寄存器中的地址到对应的内存RAM中取指令,然后PC寄存器中的地址自动加一。通过这种操作,控制单元就可以不停地从内存RAM中取指令、翻译指令、运行指令,程序就可以源源不断地运行下去了。

早期CPU的工作频率和内存RAM相比,差距不是一般的大。控制单元从RAM中加载数据到CPU,或者将CPU内部的数据存储到RAM中,一般要经过多个时钟读写周期才能完成:找地址、取数据、配置、输出数据等。运算速度再快的CPU,也只能傻傻地干等几个时钟周期,等数据传输成功后才可以接着执行下面的指令。内存带宽的瓶颈会拖CPU的后腿,影响CPU的性能。

为了提高性能,防止RAM拖后腿,CPU一般都会在内部配置一些寄存器,用来保存CPU在计算过程中的各种临时结果和状态值。ALU在运算过程中,当运算结果为0、为负、数据溢出时,也会有一些Flags标志位输出,这些标志位对控制单元特别有用,如一些条件跳转指令,其实就是根据运算结果的这些标志位进行跳转的。

CPU跳转指令的实现其实也很简单:根据ALU的运算结果和输出的Flags标志位,直接修改PC寄存器的地址即可,控制单元会自动到PC指针指向的内存地址取指令、翻译指令和运行指令。跳转指令的实现,改变了程序按顺序逐步执行的线性结构,可以让程序执行更加灵活,可以实现更加复杂的程序逻辑,如程序的分支结构、循环结构等。

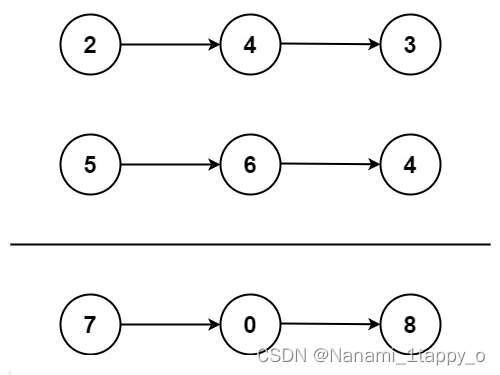

CPU所支持的加、减、乘、与、或、非、跳转、Load/Store、IN/OUT等基本指令,一般称为指令集。任何复杂的运算都可以分解为指令集中的基本指令。在软件层面上,我们可以把这些有限的基本指令进行不同的组合,实现各种不同的功能:播放视频、播放音乐、图片显示、网络传输。

我们也可以基于这些基本指令实现新的指令,以除法运算为例,如果CPU在硬件电路上不支持除法指令,我们就可以基于CPU指令集中的原生加、减、移位等指令来模拟除法的实现,生成新的除法指令。

这种由基本指令组成的不同组合,我们称为程序。为了编程方便,我们给每个二进制指令起一个别名,使用一个助记符表示,这些助记符就是汇编语言,由助记符组成的指令序列就是汇编程序。汇编语言的可读性虽然比二进制的机器指令好了很多,但是当汇编程序很大、程序的逻辑很复杂时,维护也会变得无比艰难,这时候高级语言就开始问世了,如C、C++、Java等。高级语言的读写更符合人类习惯,更适合开发和阅读,如下图所示,编写好的高级语言程序通过编译器,就可以翻译成CPU所能识别的二进制机器指令。

(高级语言的编译流程)

CPU内部的各种运算单元,无论是算术逻辑单元、控制单元,还是各种寄存器、译码电路,其实都是由大量逻辑门电路组合构成的:与门、或门、非门等。

这些基本的门电路通过逻辑组合、封装和抽象,就构成了一个个具有特定功能的模块:寄存器、译码电路、控制单元、算术逻辑运算单元等。具有不同功能的模块再经过不断地抽象、堆叠和组合,就构成了一个完整的CPU内部电路系统组件。

随着集成电路的发展,CPU也变得越来越复杂,现在的CPU可由上亿个门电路、几十亿个晶体管组成。如果靠手工一个一个门电路地连接它们,效率太低了,目前的CPU设计,一般都使用VHDL或Verilog硬件描述语言(Hardware Description Language,HDL)来整合ALU、内控制单元、寄存器、Cache等电路模块,然后通过电子设计自动化(Electronic Design Automation,EDA)工具将其转换为逻辑门电路。借助HDL编程和EDA开发工具,数字IC设计工程师只需要关心数字电路的逻辑功能实现,而具体物理电路的实现、布线和连接则由EDA工具自动完成,大大提升了工作效率。

CPU设计流程

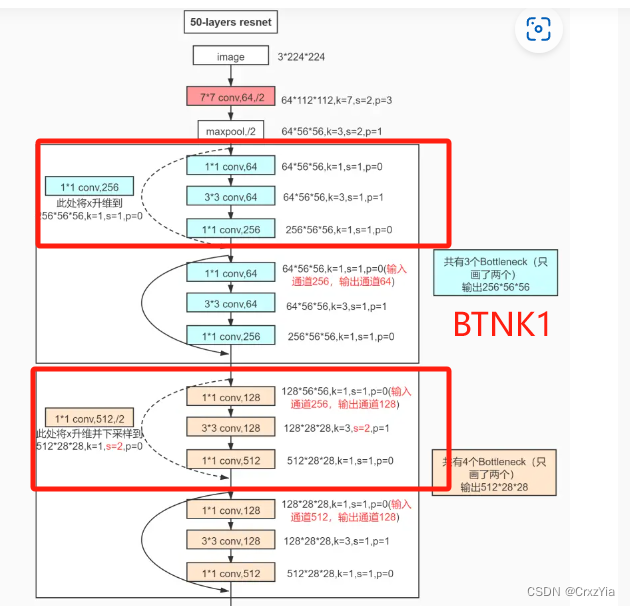

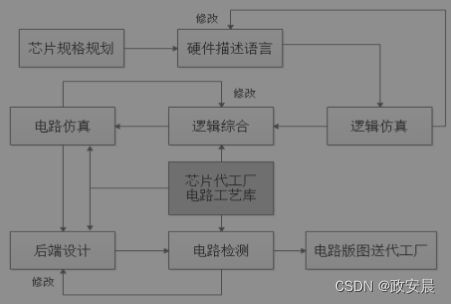

集成电路(Integrated Circuit,IC)设计一般分为模拟IC设计、数字IC设计和数模混合IC设计。数字IC设计一般都是通过HDL编程和EDA工具来实现一个特定逻辑功能的数字集成电路的。以设计一款ARM架构的SoC芯片为例,它的基本设计流程如下图所示:

(SoC芯片设计流程)

1.设计芯片规格

根据需求,设计出芯片基本的框架、功能,进行模块划分。有些复杂的芯片可能还需要建模,使用MATLAB、CADENCE等工具进行前期模拟和仿真。

2.HDL代码实现

使用VHDL或Verilog硬件描述语言把要实现的硬件功能描述出来,接着通过EDA工具不断仿真、修改和验证,直到芯片的逻辑功能完全正确。这种仿真我们一般称为前端仿真,简称前仿。

前仿只验证芯片的逻辑功能是否正确,不考虑延时等因素。这个阶段也是芯片设计最重要的阶段,会耗费大量的时间去反复验证芯片逻辑功能的正确性。

芯片公司内部一般也会设有数字IC验证工程师岗位,招聘工程师专门从事这个工作。以设计一个1位加法器为例,我们可以通过EDA工具编写下面的Verilog代码来实现,并通过EDA工具提供的仿真功能来验证加法器的逻辑功能是否正确。

3.逻辑综合

(数字电路的实现:逻辑门电路的组合)

如上图所示,前端仿真通过后,通过EDA工具就可以将HDL代码转换成具体的逻辑门电路。专业说法是将HDL代码翻译成门级网表:Gate-level netlist,网表文件用来描述电路中元器件之间的连接关系。有数字电路基础的人都知道,任何一个逻辑运算都可以转化为基本的门级电路(与门、或门、非门等)的组合来实现,而网表就是用来描述这些门级电路的连接信息的。

在综合过程中,有时候还需要设定一些约束条件,让综合出来的具体电路在芯片面积、时序等参数上满足预期要求。此时的电路考虑了延时等因素,和实际的芯片电路已经很接近了。

现在很多IC设计公司一般都是Fabless。Foundry在集成电路领域一般指专门负责生产、制造芯片的厂家,如台积电、中芯国际等。Fabless是Fabrication(制造)和less的组合词,专指那些只专注于集成电路设计,而没有芯片制造工厂的IC设计公司。像高通、联发科、海思半导体这些没有自己的芯片制造工厂,需要台积电、中芯国际代工生产的IC设计公司就是Fabless,而像Intel、三星半导体这些有自己芯片制造工厂的IC设计公司就不能称为Fabless。

对于一些Fabless的IC设计公司而言,门级电路一般是由晶圆厂,也就是芯片代工厂以工艺库的形式提供的,如中芯国际、台积电、三星半导体等。如果你设计的芯片委托台积电代工制造,工艺制程是14nm,那么当你在设计芯片时,台积电会提供给你14nm级的工艺库,里面包含各种门电路,经过逻辑综合生成的电路参数,如延时参数,和台积电生产芯片实际使用电路的工艺参数是一致的。

4.仿真验证

通过逻辑综合生成的门级电路,已经包含了延时等各种信息,接下来还需要对这些门级电路进行进一步的静态时序分析和验证。为了提高工作效率,除了使用仿真软件,有时候也会借助FPGA平台进行验证。前端仿真发生在逻辑综合之前,专注于验证电路的逻辑功能是否正确;逻辑综合后的仿真,一般称为后端仿真,简称后仿。后端仿真会考虑延时等因素。

后端仿真通过后,从HDL代码到生成门级网表电路,整个芯片的前端设计就结束了。

5.后端设计

通过前端设计,我们已经生成了门级网表电路,但门级网表电路和实际的芯片电路之间还有一段距离,我们还需要对其不断完善和优化,将其进一步设计成物理版图,也就是芯片代工厂做掩膜版需要的电路版图,这一阶段称为后端设计。后端设计包括很多步骤,具体如下:

● DFT:Design For Test,可测试性设计。芯片内部一般会自带测试电路,如插入扫描链、引出JTAG调试接口。

● 布局规划:各个IP电路模块的摆放位置、时钟线综合、信号线的布局等。

● 物理版图验证:检查设计规则、连线宽度、间距是否符合工艺要求和电气规则。

物理版图验证通过后,芯片设计公司就可以将这个物理版图以GDSII文件的格式交给芯片制造代工厂(Foundry)去流片了。到了这一步,整个芯片设计、仿真、验证的流程就结束了,我们称为tap-out。

物理版图是由我们设计的芯片电路转化而成的几何图形。

如下图所示,和PCB版图类似,物理版图中包含了集成电路元器件的尺寸大小、各层电路的拓扑关系等。物理版图也分为好多层,版图中不同的颜色代表不同的层,每一层都代表不同的电路实现。

(从逻辑门电路到物理版图的转换)

芯片代工厂根据物理版图提供的这些信息来制造掩膜板,然后使用光刻机,通过掩膜板在晶圆的硅片衬底上开凿出各种掺杂窗口,接着对硅片进行离子注入,掺杂不同的三价元素和五价元素,生成PN结,进而构成二极管、三极管、CMOS管等基本元器件,构建出各种门电路。

如下图所示,光刻机根据物理版图的不同层,制作不同的掩膜板,从底层开始,逐层制作,就可以在晶圆硅片衬底上生成多层立体的3D电路结构。

(从物理版图到实际的芯片电路)

晶圆上的一个个CPU芯片电路在经过切割、封装、引出管脚、测试后,就是我们在市场上常见的各种CPU芯片了。

到这里,我们已经把芯片设计、制造的整个大致流程给大家分享完了。

芯片的设计和制造看起来很简单,但实际上每个环节都有极高的技术含量。集成电路行业是一个极其专业而且高度分工的行业,每个环节都有不同的行业巨头或隐形冠军把守,从芯片的设计、验证仿真、制造加工、封装测试到各种EDA工具、IP核、光刻机、刻蚀机,每个环节都有非常专业的制造商、服务商、EDA工具商精密严谨地配合,大家互相促进,将CPU芯片一代又一代地不断更新迭代下去。

有了CPU处理器,还需要配套的主板或开发板、内存RAM、硬盘或Flash存储器,才能构成一个完整的计算机整机系统,这样才能运行我们编写的程序软件。

咱们这篇文章告一段落,在以后的文章中,咱们将继续给大家分享一些有关计算机体系结构的知识。