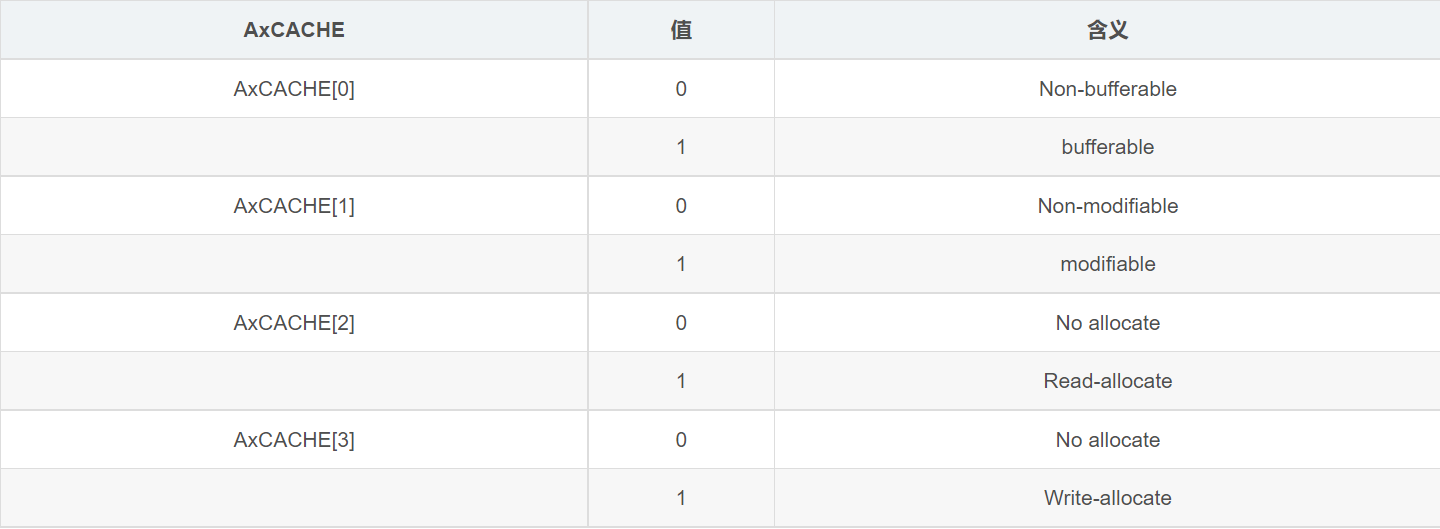

1、Axcache相关知识点

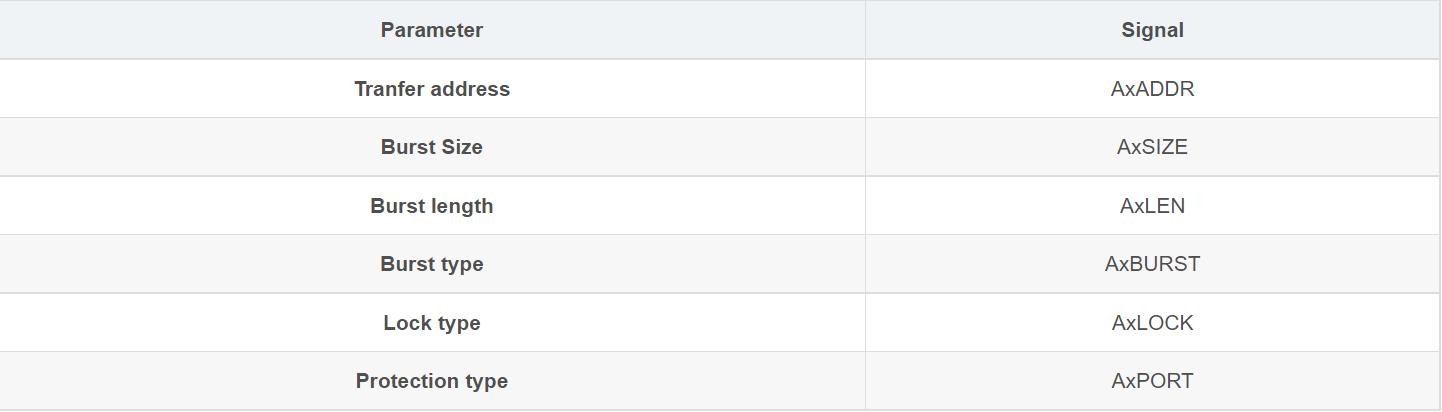

xilinx 文档Pg059推荐:

信号列表

2.3 信号含义

2.3.1 AxCACHE[0]信号bufferable

buffer:缓冲

这个信号是用来衡量AXI传输过程中过的缓冲能力的,为什么需要缓冲?

就跟我们上篇文章中讨论的Outstanding传输机制有关,先传输的命令会进行等待,依次吐出数据,以此来提升传输效率,因此这个信号置0,即无缓冲能力,置1,信号在到达其最终地址前可以缓冲数个周期(无论是读还是写都是如此)

具体的bufferable结构如何实现也存在很多的方法,一个最简单的肯定是在同时钟域的条件下,用类似同步FIFO的结构,来缓冲载入的命令,再依次读出,即可参考文章如下。

【数字IC手撕代码】Verilog同步FIFO|题目|原理|设计|仿真

2.3.2 AxCACHE[1]信号modifiable

AXI3.0中AxCACHE[1]信号被称作Cacheable,而非modifiable,我们这里还是取用AXI4.0协议来做讲解,采用modifiable的概念

modify:改变

这个信号是用来衡量在传输过程中相关的地址与控制信号是否会发生改变,假如AxCACHE[1]置1,信号可以发生改变,置0,信号不能发生改变,具体是哪些信号不能发生改变呢?

【AXI】解读AXI协议中的burst突发传输机制中,核心的起始地址,传输大小,传输长度,传输种类都进行过解读,这些是决定传输形式的最重要的四个信号,而不核心的Lock Type,Protection Type属于进阶内容,以后再讨论,这里也可以暂时一放,但是读者需要注意的是,就算是能改变,改变的也是前四个信号,后两个“Lock type和Protection type”在AxCACHE[1]为1的时候同样不能改变。

请读者思考,为什么在传输过程中我们需要设定控制信号可变或者控制信号不可变呢? 列举以下这些例子,以供参考

1.一个传输切分成了多个传输

2.多个传输合并成了一个传输

3.读传输多抓了一些数据存在Cache里

4.写传输激活了更大范围的地址空间

稍微解释一下2和3,其它的操作modifiable的原因也是相似的

2.多个传输合并成了一个传输

先后发送了两个burst读传输操作,前一个是针对于32bit数据通路的低16位进行,后一个是针对于32bit数据通路的高16bit进行,其他的burst参数一致,假如我们设定了modifiable后,在outstanding传输机制中,我们更倾向于将其合并,将两个读操作进行合并为一个来进行,当然这里面涉及到很多的考量,比如说地址之间依赖关系,或者是什么情况下可以进行合并、等等等。但若是这些事情都被解决了,传输的合并势必会提高整个AXI协议的效率。

3.读传输多抓了一些数据存在Cache里

之前就一直在讨论Cache中应该放什么样的数据,什么样的数据价值更高,一个普遍的观点是,假如我们抓取了0x0000_1000这个地址的数据,那这个地址周边的数据如0x0000_0111这种的离得很近的地址最终被读取的可能型一定比地址离它远的高,因此我们可不可以把它周边的数据也同样放到离CPU更近的位置来提高效率?modifiable给出了这种操作的可能性。

2.3.3 AxCACHE[2]信号

这个信号在AXI3中直接当作read-allocate的判断,但是在AXI4.0中被分配了新的意义,具体如下

对于读transaction而言

AxCACHE[2]置1,说明需要去cache中检查读地址是否之前被分配

AxCACHE[2]置0,说明不需要去cache中检查读地址是否被分配

对于写transaction而言

AxCACHE[2]置1,同样需要去cache中检查写地址是否被分配(虽然是写transaction,但是之前的读行为或其他主设备transaction行为同样可能使cache中存在这个地址)

AxCACHE[2]置0,说明不需要去cache中检查地址是否之前被分配

2.3.4 AxCACHE[3]信号

与AxCACHE[2]极其相似

对于写transaction而言

AxCACHE[3]置1,说明需要去cache中检查写地址是否之前被分配

AxCACHE[3]置0,说明不需要去cache中检查写地址是否被分配

对于读transaction而言

AxCACHE[3]置1,同样需要去cache中检查写地址是否被分配(虽然是读transaction,但是之前的写行为或其他主设备transaction行为可能使cache中存在这个地址)

AxCACHE[3]置0,说明不需要去cache中检查地址是否之前被分配

2.3.5 总结

具体是否应该去cache中检查是否allocate,由两个信号决定,即AxCACHE[2]和AxCACHE[3]共同决定。检查分配这个行为,只有 AxCACHE[3:2] = 2’b00 时才不需要检查cache中的数据,不过AxCACHE[3]和AxCAHE[2]置1,所代表的为什么cache中可能被分配的原因是不一样的,即“是读或写操作产生了分配,是自身还是其他主设备的操作产生了分配。”的区分

除此以外,AxCACHE[1]决定信号可否改变,AxCACHE[0]决定信号可否缓冲。

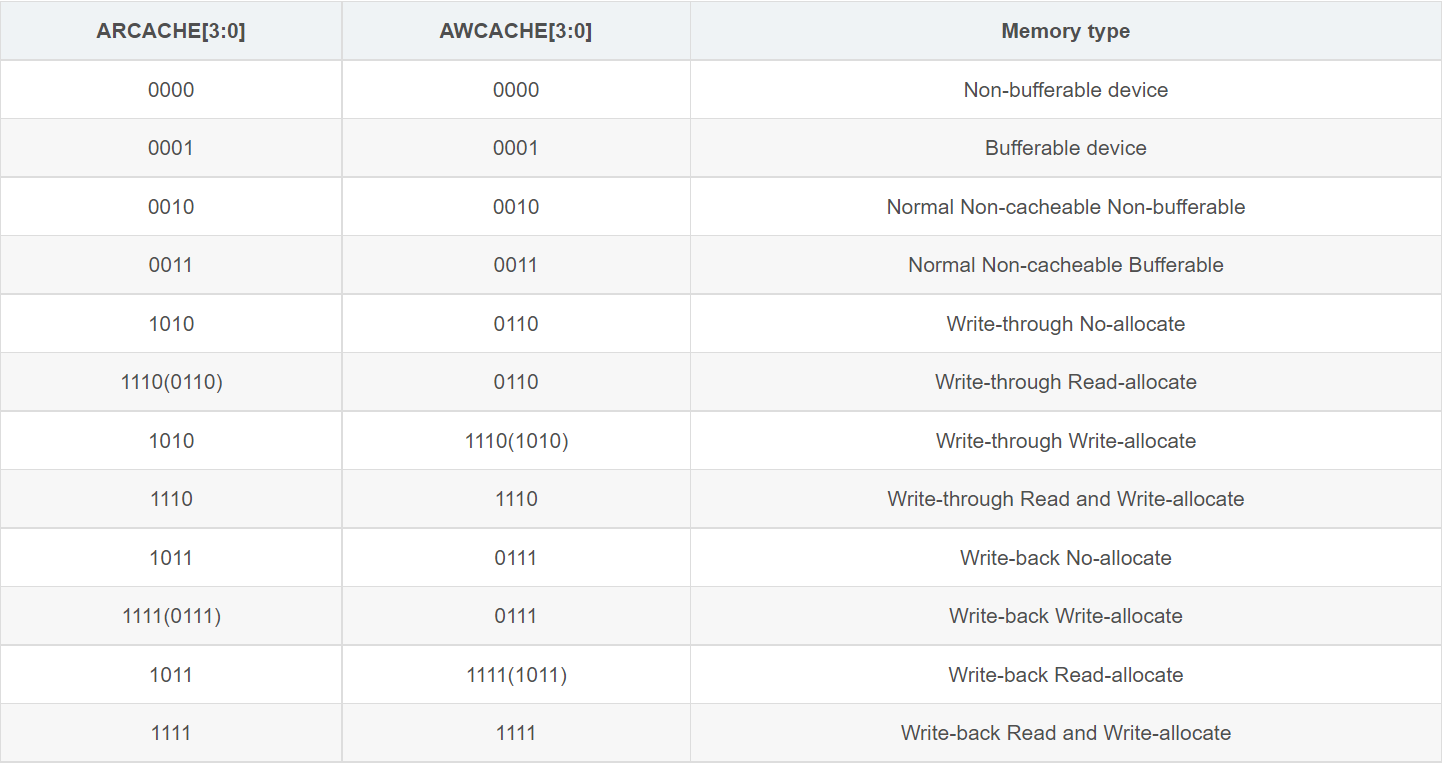

2.4 实例分析(memory为例)

为什么我们要用memory做例子解读?

因为对于内存来说,需要支持尽可能多的transaction种类,而对于很多其他从设备而言,只需要支持一部分transaction特性即可,使用meemory做例子,覆盖最广。

1.bufferable指能否缓冲

2.cacheable指是否需要去cache查找是否allocate

3.所谓的No-allocate并不是说读写transaction的分配被禁止

这些概念在协议中都有具体的规定,有需要的直接进行查阅即可,这些memory type的名字更多的是一种种类的划分,而非实际的含义

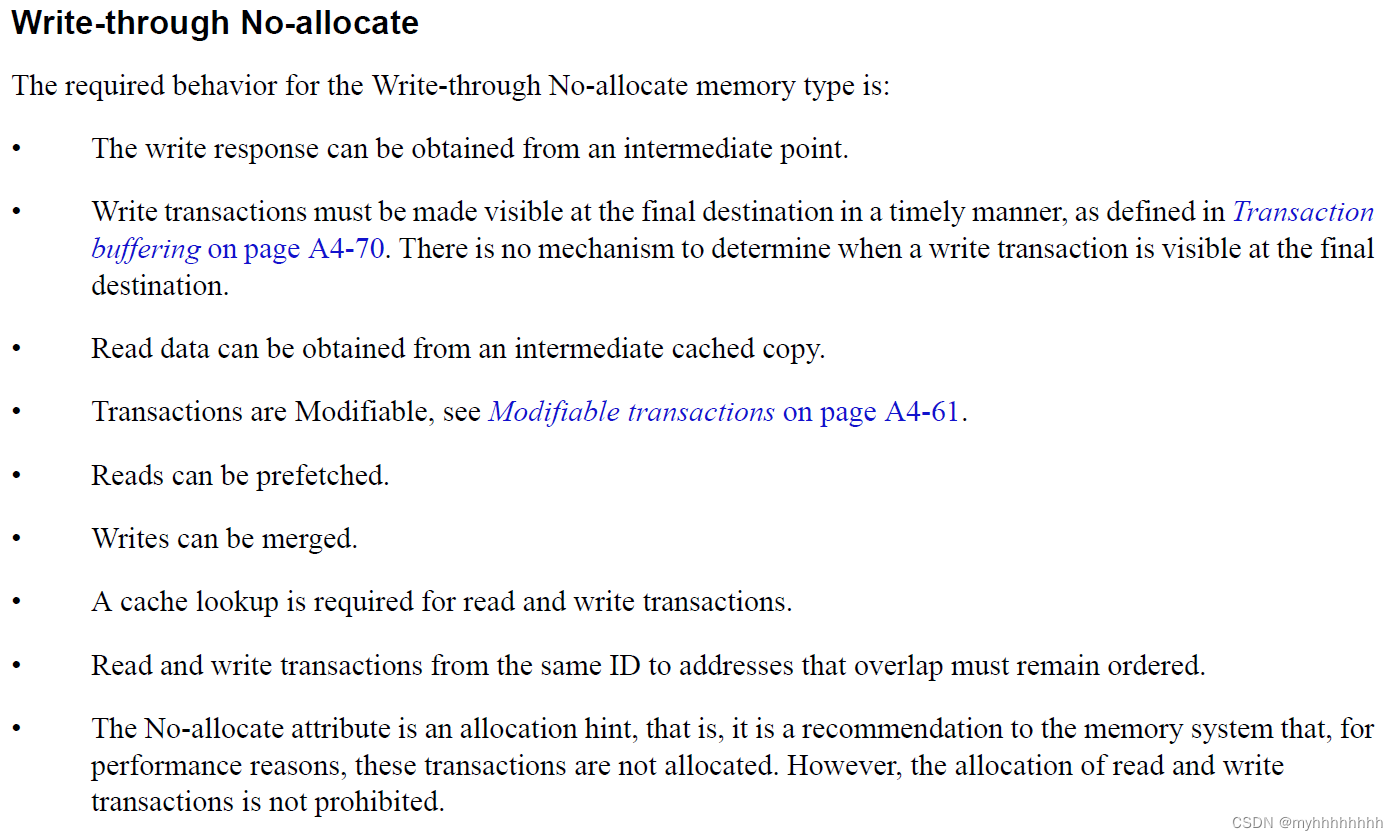

比如说“Write-through No-allocate”的含义是这样子