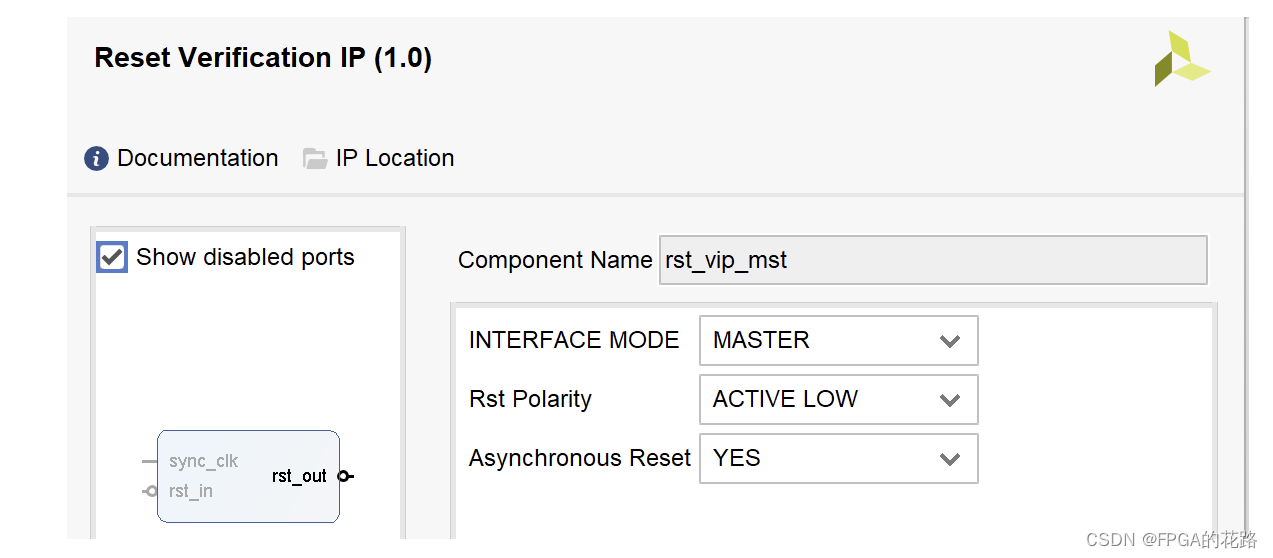

//置位复位信号

< hierarchy_path>.assert_reset();

//取消置位复位信号

< hierarchy_path>.deassert_reset();

//设置 RST_VIP 模式为 Master

< hierarchy_path>.set_master_mode();

//设置 RST_VIP 模式为 passthrough

< hierarchy_path>.set_passthrough_mode();

module rst_vip_0_exdes_tb(

);

wire rst_out;

//Simple loop integer

integer i;

// Simple loop integer.

integer j;

integer rst_initial_delay ;

integer rst_hold_length ;

integer wait_length_before_switch_mode;

integer wait_length_before_finish;

initial begin

rst_initial_delay =22;

rst_hold_length = 208;

wait_length_before_switch_mode=14;

wait_length_before_finish =12;

#(rst_initial_delay );

// Switch Passthrough RST VIP into Master mode

rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.set_master_mode();

#(rst_initial_delay );

// Passthrough RST VIP in runtime master mode assert_reset

rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.IF.assert_reset();

#0ps;

if( rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.IF.RST != 0) begin

$error("reset is not as expected in assert_reset of Passthrough VIP runtime master mode");

end

#(rst_hold_length);

// Passthrough RST VIP in runtime master mode deassert_reset

rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.IF.deassert_reset();

#0ps;

if( rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.IF.RST == 0) begin

$error("reset is not as expected in deassert_reset of Passthrough VIP runtime master mode");

end

#(wait_length_before_switch_mode);

rst_vip_0_exdes_tb.DUT.ex_design.rst_vip_passthrough.inst.set_passthrough_mode();

#(wait_length_before_finish);

$display("EXAMPLE TEST DONE : Test Completed Successfully");

$finish;

end

chip DUT(

.rst_out(rst_out)

);

endmodule

![[数据结构]队列](https://img-blog.csdnimg.cn/direct/dc8dd37d010f4e46a608d3dcac720b19.png)