先说一下tsmc的std cell

tsmc 7nm工艺下有专门的std synccell 命名如下:

SDFSYNC1RPQD1XXXXVT

SDFSYNC1SNQD1XXXXVT

SDFSYNC1QD1XXXXVT

不考虑VT, PWR和track,电压等差别,整个工艺库下只有这三种

实际在项目中synccell一般直接上ULVT,既然是SDF,就是带Scan接口的DFF,SN (set negtive)是低置位,RP(reset positive)是高复位,既没有SN也没有RP的就是无复位寄存器。

进一步解释

低置位:复位信号为0有效;对应的复位端pin name为SDN (set data negtive)

高复位:复位信号1有效,复位值为0;对应的复位端pin name为CD (clear data)

无复位:没有复位和置位信号,上电Q输出不可知

其实例化如下:

SDFSYNC1RPQD1xxxxxULVT UI_sync(.D(d), .SI(1'b0), .SE(1'b0), .CP(CLK), .CD(~rst_n), .Q(q));

SDFSYNC1SNQD1xxxxxULVT UI_sync(.D(d), .SI(1'b0), .SE(1'b0), .CP(CLK), .SDN(rst_n), .Q(q));

SDFSYNC1QD1xxxxxULVT UI_sync(.D(d), .SI(1'b0), .SE(1'b0), .CP(CLK), .Q(q));上面是对tsmc的标准DFF cell做一下介绍,接下来要根据这个DFF 介绍一下scan chain

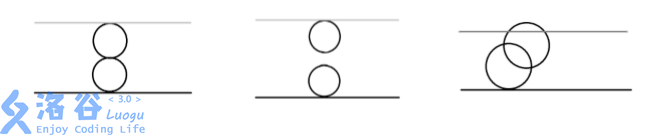

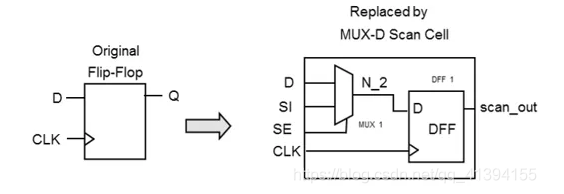

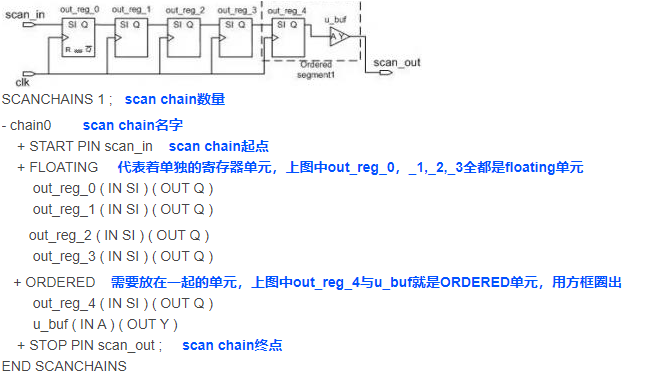

1:定义:满足可测试性设计(DFT),将设计中所有的触发器连接到一条或者若干条链上,称为scan chain,将一个复杂的时序电路转换为简单的组合电路进行测试,这一步是在逻辑综合(DC)中实现。

当SE=1当SI=1时,电路进入scan状态,当SI=0时,电路工作在normal状态。

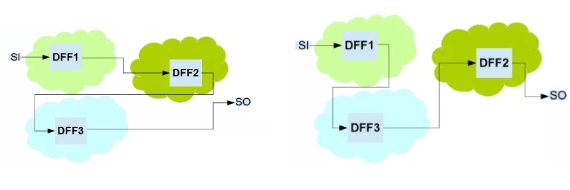

2:为什么进行scan chain reordering

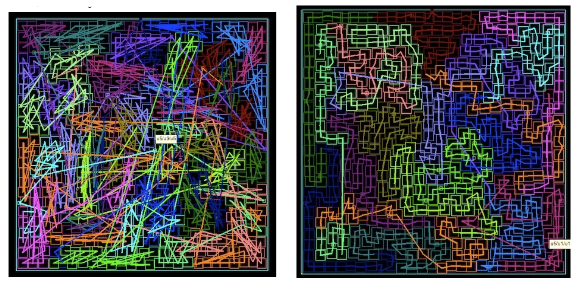

在DC综合阶段,工具没有寄存器的物理位置信息,按照字幕顺序做scan chain的插入,链接方式并不是最优的。在ICC2中place是基于time 和 congestion driven,所以原来寄存器在scan chain中是前后级关系,在ICC2中可能距离得比较远,导致寄存器SI端走线很乱,加重了design中的congestion issue问题。

3:如何做reordering

首先在逻辑综合阶段,写出scandef,其次在ICC中读入对应的scandef

import_def scan.def

在place_optimize和post_cts_opt命令进行reordering scan chain。

做了reordering scan chain之后,相邻的寄存器连线很近,会导致hold违例较多,因此在place阶段重排序之后,务必在cts_opt阶段继续做进一步优化。

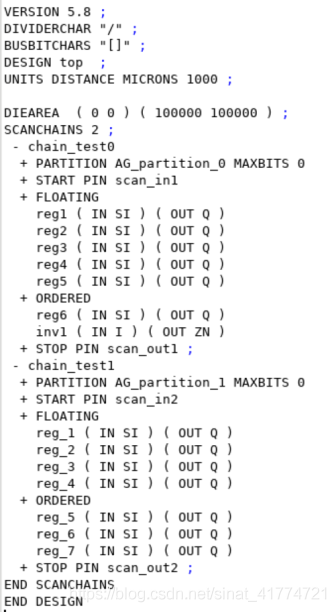

4:scan.def的结构

若case中已经有scan chain,可以通过下面命令直接输出scan.def和top.v文件

export_def -scan scan.def

export_verilog top.v5:完整Scan.def 的结构

本篇博客借鉴了两篇文章:

tsmc 7nm工艺下用做syncCell的stdCell介绍_cy413026的博客-CSDN博客

数字IC笔记-scan chain_卢卡猫的博客-CSDN博客