本文验证-gated_clock_conversion设置为on或off时,给Schematic带来的差异。

-gated_clock_conversion设置为on时,用于移除门控时钟,门控时钟是由门电路而非专用时钟模块(例如MMCM或PLL)生成的时钟。

门控时钟会对设计带来一些负面影响。

典型的危害包括:时钟信号可能会有毛刺;时钟歪斜(Clock Skew)会恶化。

- 当时钟负载少且时钟频率低(比如小于5MHz)时,可以适当使用门控时钟,此时建议手工插入BUFG。

- 设计中应该尽量避免使用门控时钟,时钟信号应尽可能由MMCM/PLL产生。

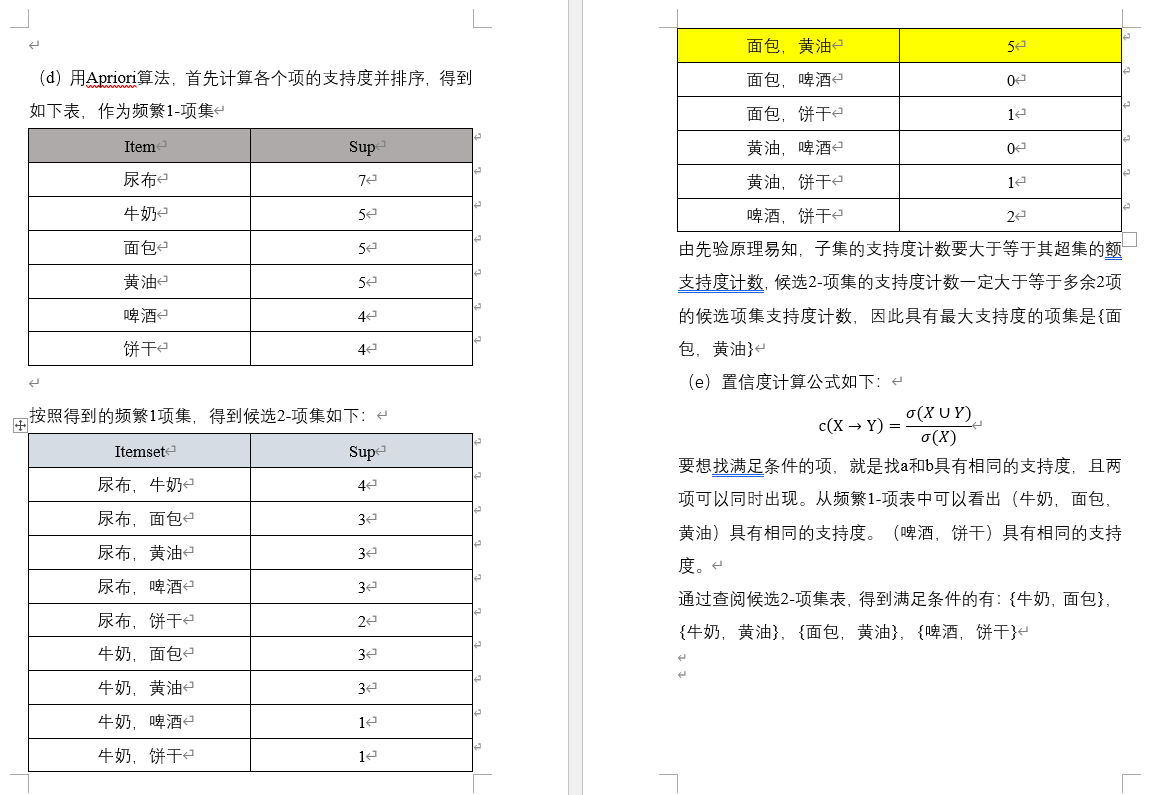

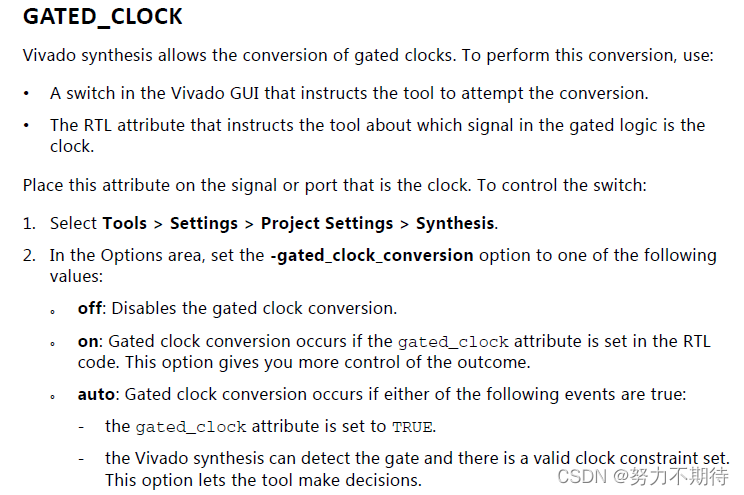

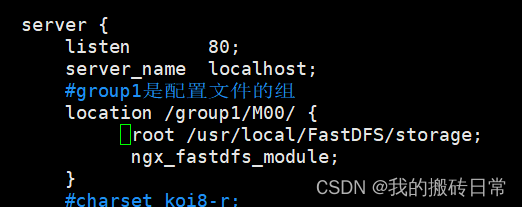

UG901有如下图的描述:

上图说明:要实现门控时钟的转换必须在综合设置中将-gated_clock_conversion设置为on或auto,且要在Verilog代码中设置gated_clock属性,两者缺一不可。设置gated_clock属性指定了门控时钟逻辑的输入时钟(而非输出时钟),比如:(* gated_clock = “true” *) input clk;中的clk就是输入时钟。

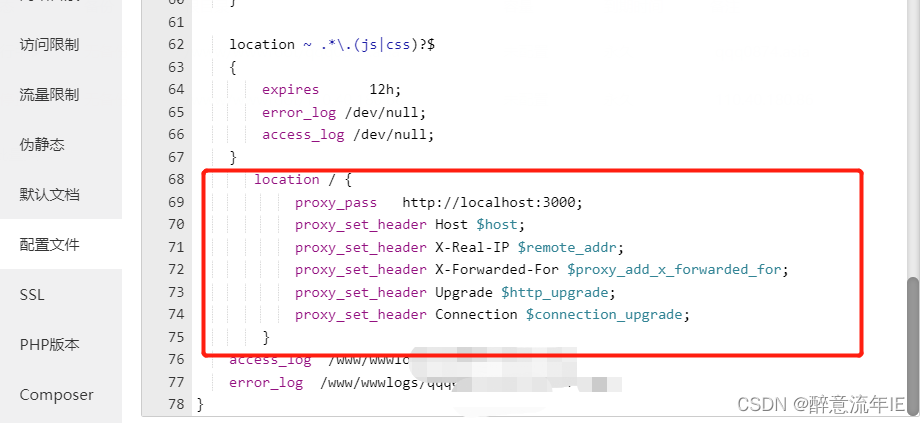

下图是门控时钟的测试代码。

测试代码1

module top(

(* gated_clock = "true" *) input clk,

input clk_en,

output reg cnt

);

wire pll_out;

assign pll_out = clk_en & clk;

always @(posedge pll_out)

begin

cnt <= cnt + 1;

end

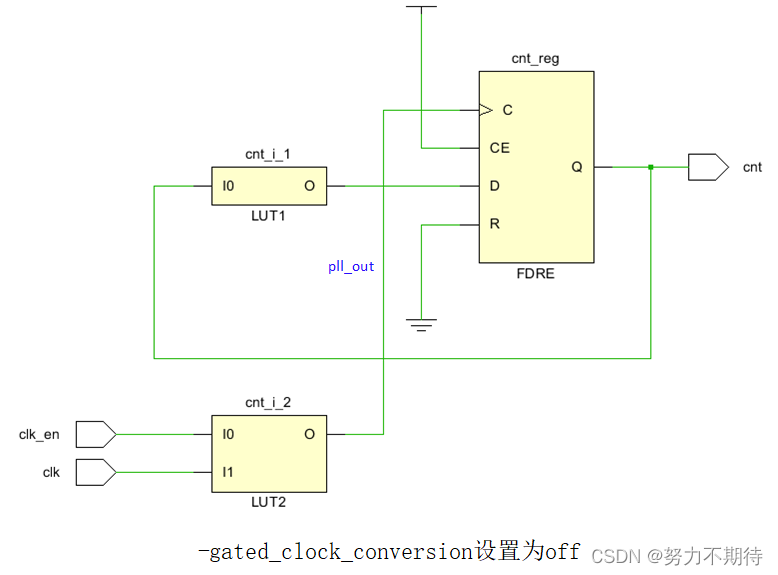

endmodule其中,assign pll_out = clk_en & clk;就是一个典型的门控时钟代码,上述代码经过综合后的原理图见下图:

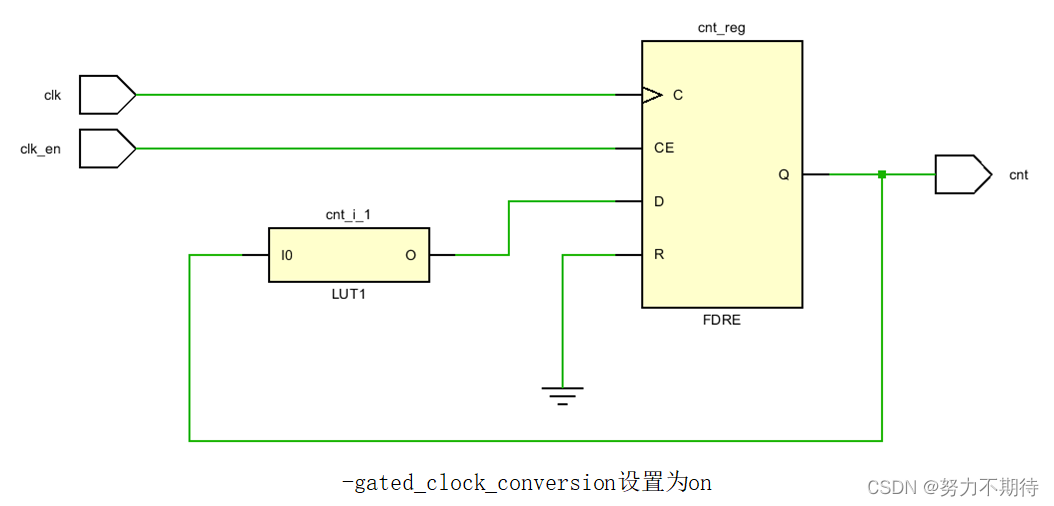

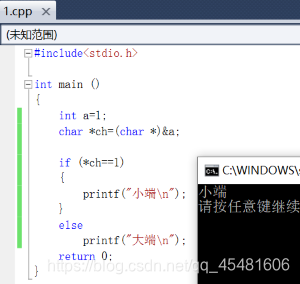

-gated_clock_conversion设置为off时的原理图1

上图中时钟pll_out是通过LUT2产生的,从硬件设计的角度看,不建议这样产生时钟,显得不够专业,这里我们将-gated_clock_conversion设置为off了,导致Vivado综合器即使看这个图不舒服,甚至还有点想笑,但也不会做什么~

-gated_clock_conversion设置为on时的原理图1

当我们将-gated_clock_conversion设置为on后,Vivado综合器看上上图不舒服,说,让开,老子来给你改改图,就改成了上图的样子,上图已经没有门控时钟了,这个图看起来也专业~

测试代码2

module top(

(* gated_clock = "true" *) input clk,

input clk_en,

input rst,

output reg [3:0] cnt

);

wire gate_clock;

reg [3:0] cnt_i;

assign gate_clock = clk_en & clk;

always @(posedge gate_clock)

begin

if(rst)

cnt_i <= 0;

else

cnt_i <= cnt_i + 1;

cnt <= cnt_i;

end

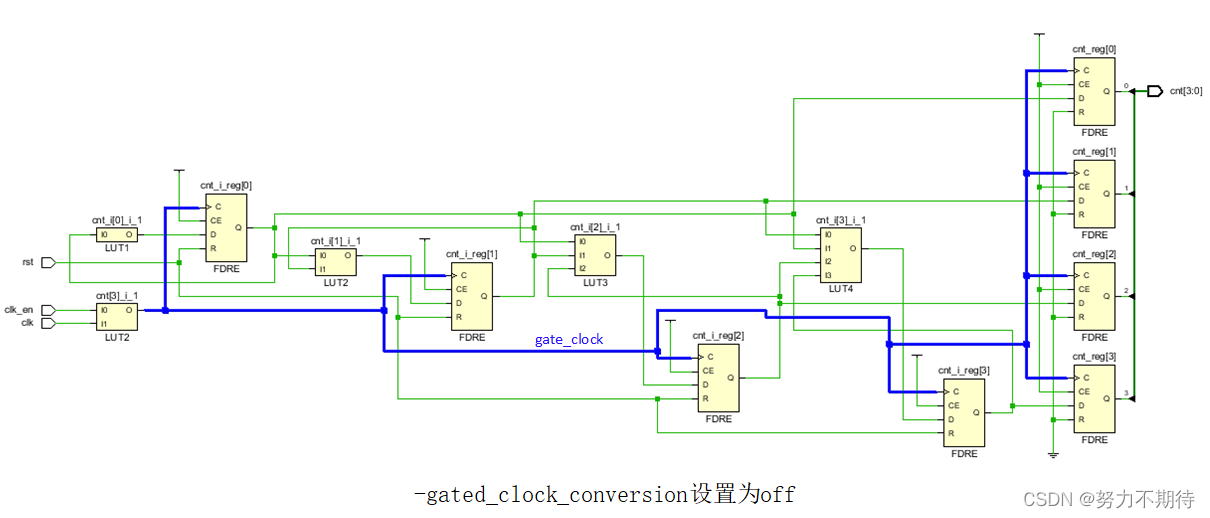

endmodule-gated_clock_conversion设置为off时的原理图2

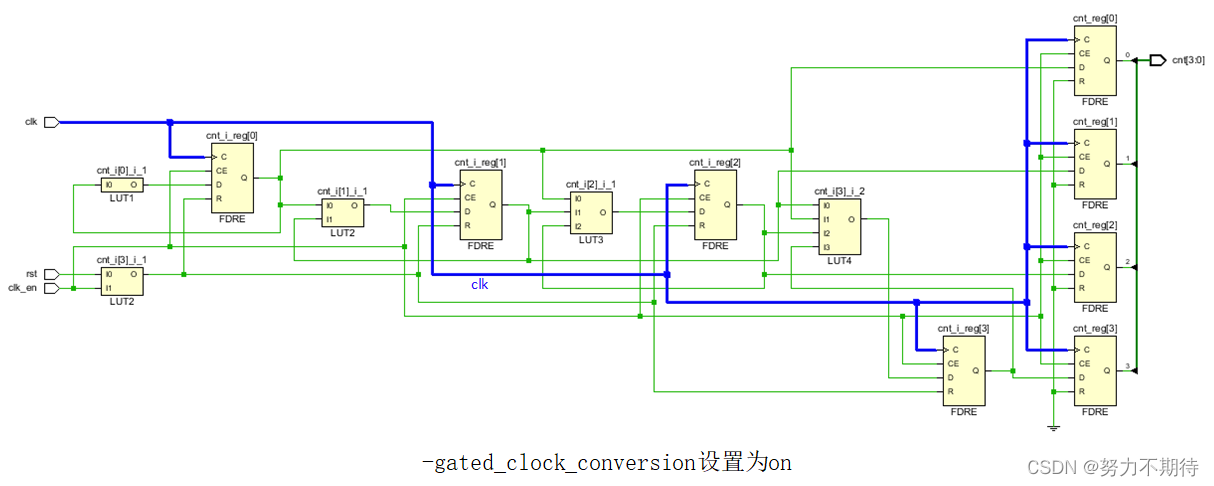

-gated_clock_conversion设置为on时的原理图2

![LeetCode[703]数据流中的第K大元素](https://img-blog.csdnimg.cn/img_convert/19af8564ccb7483cbf6fbcf42cf69c77.png)