只要信号遇到瞬时阻抗突变,就会发生反射。反射信号的量值由瞬时阻抗的变化量决定,将反射电压与入射电压的比值称为反射系数,可以用如下公式计算:

反射是造成单一线网络中所有信号质量的问题根源。为减小影响,需要做到以下几点:

- 使用可控阻抗互连;

- 传输线两端至少有一个端接匹配;

- 选择布线拓扑结构,使多分支的影响最小化;

- 让几何结构的任何突变都最小化。

阻性负载反射

阻性负载根据端接的不同反射有3种特殊的典型情况:

- 传输线的终端开路,反射系数为1,1V的信号反射后,反射电压为1V,最终电压变为2V

- 传输线的终端短路,反射系数为-1,1V的信号反射后,反射电压为-1V,最终电压变为0V

- 传输线的终端阻抗匹配,反射系数为0,1V的信号不发生反射,最终电压保持为1V.

反射波形

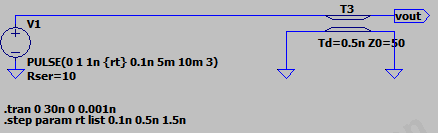

反射波形,可以使用精典的反弹图进行计算得到,一般也可以通过SPICE电路仿真得到,下面使用LTspice对反射波形的仿真情况。

仿真条件:信号电压幅度为1V,上升沿时间为0.1ns到1.5ns分别进行仿真。

一般在设计电路板时都会采用可控阻抗的互连,但是往往有在以下场景,信号仍会遇到阻抗突变:

- 传输线的两端

- 封装上的引线

- 输入门电容

- 信号层之间的转换过孔

- 信号线的拐角

- 信号线或过孔桩线

- 信号线的分支

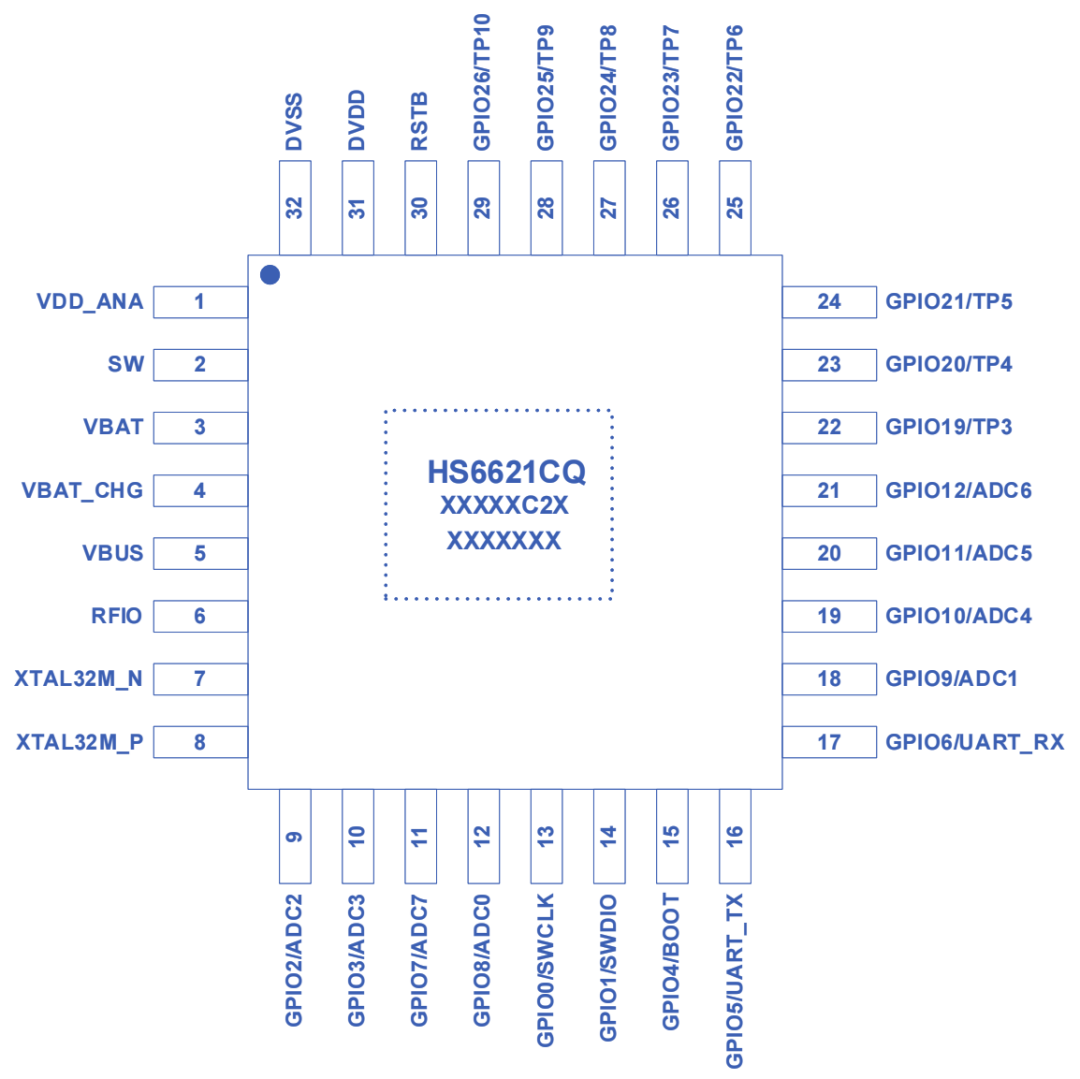

- 测试点焊盘

- 返回路径上的间隙

- 扇出区的NECK走线

- 线的交叉

多长的走线需要端接

根据经验规则,当传输线的时延超过上升沿时间的20%,振铃会引起问题,所以得到以下公式:

当线长在数值上小于上升时间时,传输线的终端可以不做端接。注意单位:in ~ ns , mil ~ ps

但是,随着信号速率越来越高,信号的上升时间越来越短。对于高速接口,几乎所有的连线都越过了上面的限制,所以都需要进行端接。

一般的端接策略

振铃是由源端到远端的阻抗突变、两端之间不断的多次反射引起,所以如果能至少在一端消除反射,就能减小振铃噪声。

一个驱动器驱动一个接收器的情况称为点到点的拓扑结构,以下是这种结构常用的端接方法:

源端串联端接:最常用的端接方法,串联电阻与驱动器内阻之和需要等于传输线阻抗。但由于PCB布局面积,仅在很少的地方使用。

远端并联端接:高速接口(如DDR SERDES)常用的端接方法,端接电阻大小需要接近传输线阻抗,但由于电阻并接到地,会有额外的功耗存在,并且会造成定程度的高电平降低。

远端戴维南端接:在DDR上较为常见,两个电阻的并联需要近接传输线的阻抗。其解决了远端并联端接会影响到电平的问题。但由于需要两个器件,它的使用受到PCB布局面积的制约,同时由于其与远端并联相对功耗较大。

远端RC端接:减决了并联端接的电流消耗问题,端接电阻需要等于传输线的阻抗。一般电容取0.1uF。但是由于RC电路会造成信号上升沿变缓,所以其实际取值要特别注意。

几种PCB上常见的反射问题

1. 短串联传输线反射

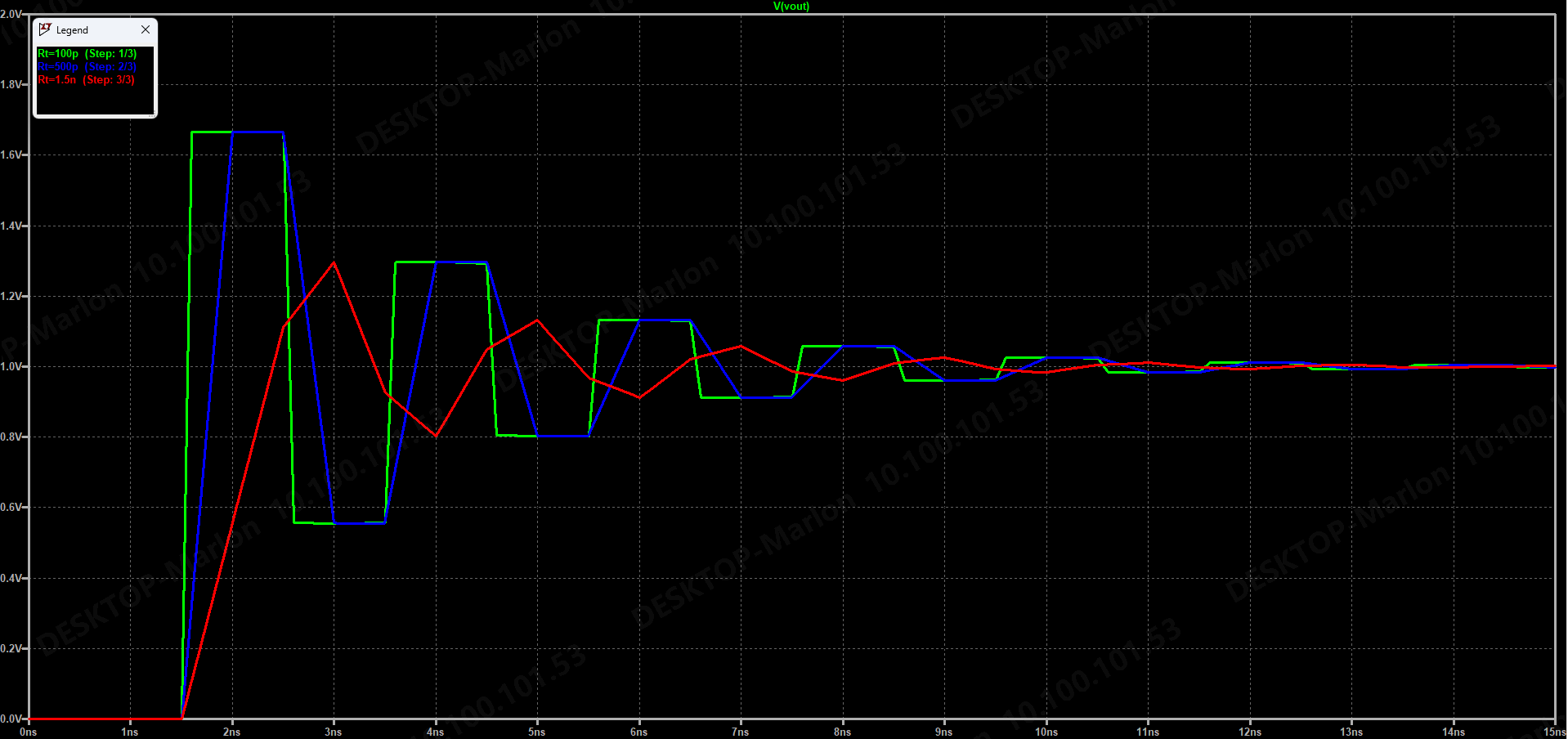

在PCB上的走线,常常会需要穿过过孔区,或元件密集区。此时线宽变窄,阻抗会变大。下面是短线阻抗不同大小的反射情况。

可以看到,两段传输线中间的传输段如果阻抗变小,波形会首先下陷;如果中间阻抗变大,波形会首先上突。突变段的前后两段会影响上突或下陷出现的延迟时间。

如果当波形的下突到达电平的90%为限制,认为不会影响信号的正常接收的话。那以阻抗中间段的阻抗突变只要满足如下条件,可以认为其无影响。

突变段的长度应小于信号上升边,要注意其对应单位(in~ns mil~ps)。

2. 短并联传输线的反射

在PCB上的走线,有时会有一些短的分支,就称其为分支,这种结构在封装设计的过程中会遇到这种问题。

从上图可以看到,中间的桩线会引起信号振铃,波形会有较大的下陷。使用以下公式可以进行初步判断其量否影响最终的信号质量。

其桩线长度应于小信号的上升边沿。

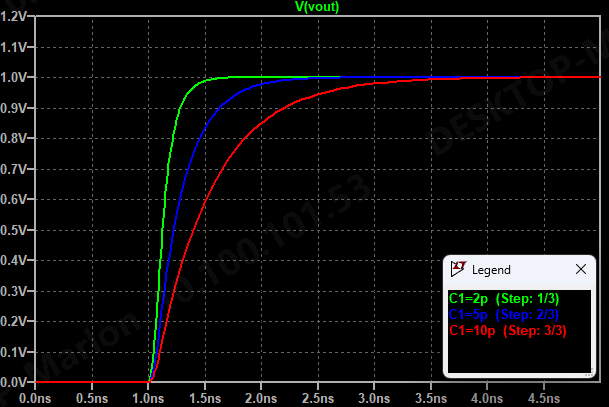

3. 容性终端的反射

在所有接收器的输入上都有门级输入电容,一般在3pF,在IBIS模型里,一般将其记为C_comp。由于电容的充电效应,会使得上升沿变缓。

4. 走线中途容性负载的反射

PCB上的测试焊盘、过孔、封装引线,互连中间的短桩线,都起着集总电容器和作用。

走线中途电容对于终端信号的第一位影响就是接收端会产生下冲噪声,而第二位的影响就是远端信号的接收时间被延迟。

5. 信号走线拐角和过孔的影响

信号走线的90度拐角,其额外增加了线宽,如同一个容性突变。其引起了信号的反射和传输信号的时延。

对于拐角处电容的可以使用如下公式进行估计:

使用阻抗线进行计算,一般常用线宽在5mil左右,可以计算得其一个拐角的电容量大约为10fF。其对于信号边的累加延时约为0.25ps。其不太可能对信号完整性产生影响。若拐角处的电容在达到pF级别的话,其信号线的宽度则需要在100mil以上了。

过孔残桩通常会引入额外的电容量,其电容的大小由孔的尺寸,反焊盘大小,表底层焊盘大小,桩线长度都有关系。由于电容效应的作用,其阻抗一般会小于,大于在。

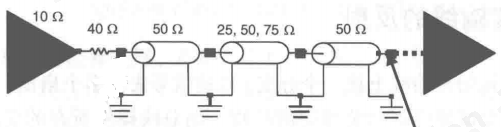

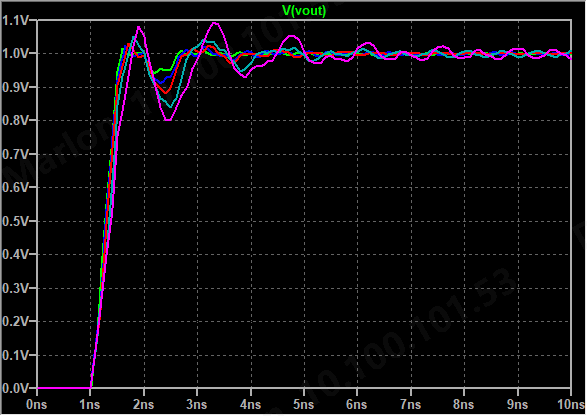

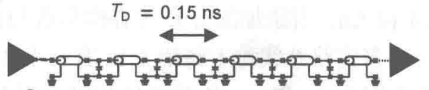

6. 有载线

当导线上分布多个容性负载(多个DDR颗粒),会引起信号失真,信号上升边会退化,将这种传输线称为有载线。若负载电容之间的间距小于信号上升边的空间延伸,那个容性反射会相互抵消。

当上升边大于电容之间的时延时,会使传输线的平均阻抗下降。

随着导线特性阻抗的降低,用于端接匹配的电阻也应随之降低。或将有分布电容的区域内,通过减小线宽,使无载阻抗变大。使最后的效果可以使有载线的阻抗比较接近于期望的阻抗值。

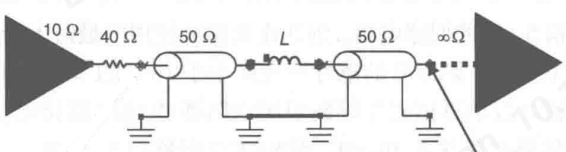

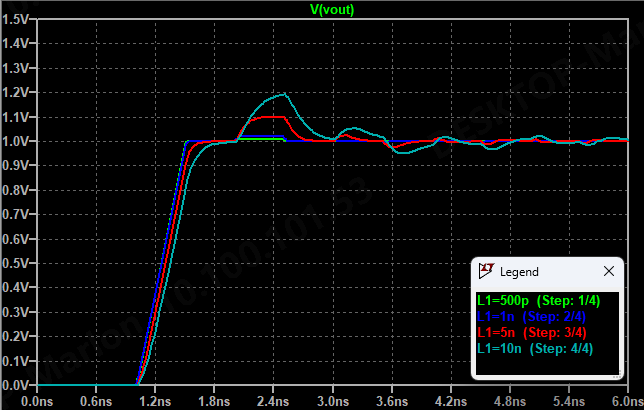

7. 感性突变的反射

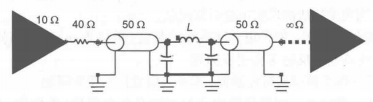

在实际的应用中,传输结构的中间不要避免的会感性器件串联(例如:连接器,换层过孔)

传输线上允许的最大电感量可以使用如下公式计算:

通过计算,有这样一个经验法则:导线上可容许的最大额外回路电感(nH)为上升边(nS)的10倍。

为了消除电感的影响,可以在电感两侧增加电容来进行补偿。

其中,大容的大小可以使用下面公式进行计算: