1、DDR2设计思路

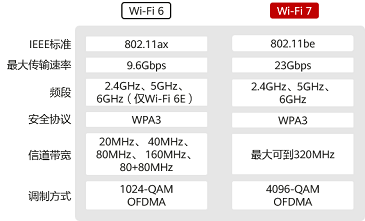

前文分别讲解了SDRAM的工作原理和SDRAM到DDR的变化,DDR采用双沿传输数据,为了提高传输数据的速率,先后推出了DDR-200、DDR-266、DDR-333、DDR-400,后面的数字表示数据传输的速率,对应的时钟频率分别为100MHz、133MHz、166MHz、200MHz,下图是DDR的内部框图。

当DDR速度提升到200MHz后,人们发现由于温度等因素的影响,导致DDR内部时钟的频率不能继续提高了。但PC的发展有需要更快读写速率的内存芯片,既然内核时钟频率不能继续提高,那就保持200MHz不动,继续提高IO端口的时钟频率,使得IO端口的时钟频率变为内核时钟频率的2倍,内核传输的数据位宽增加2倍来弥补内核时钟的差距,从而实现数据传输速率翻倍,这就是DDR2的设计思路。

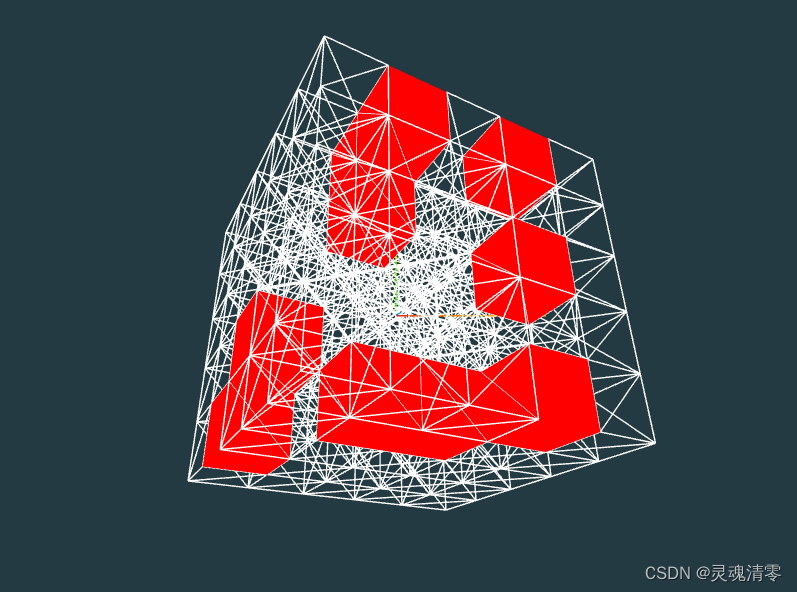

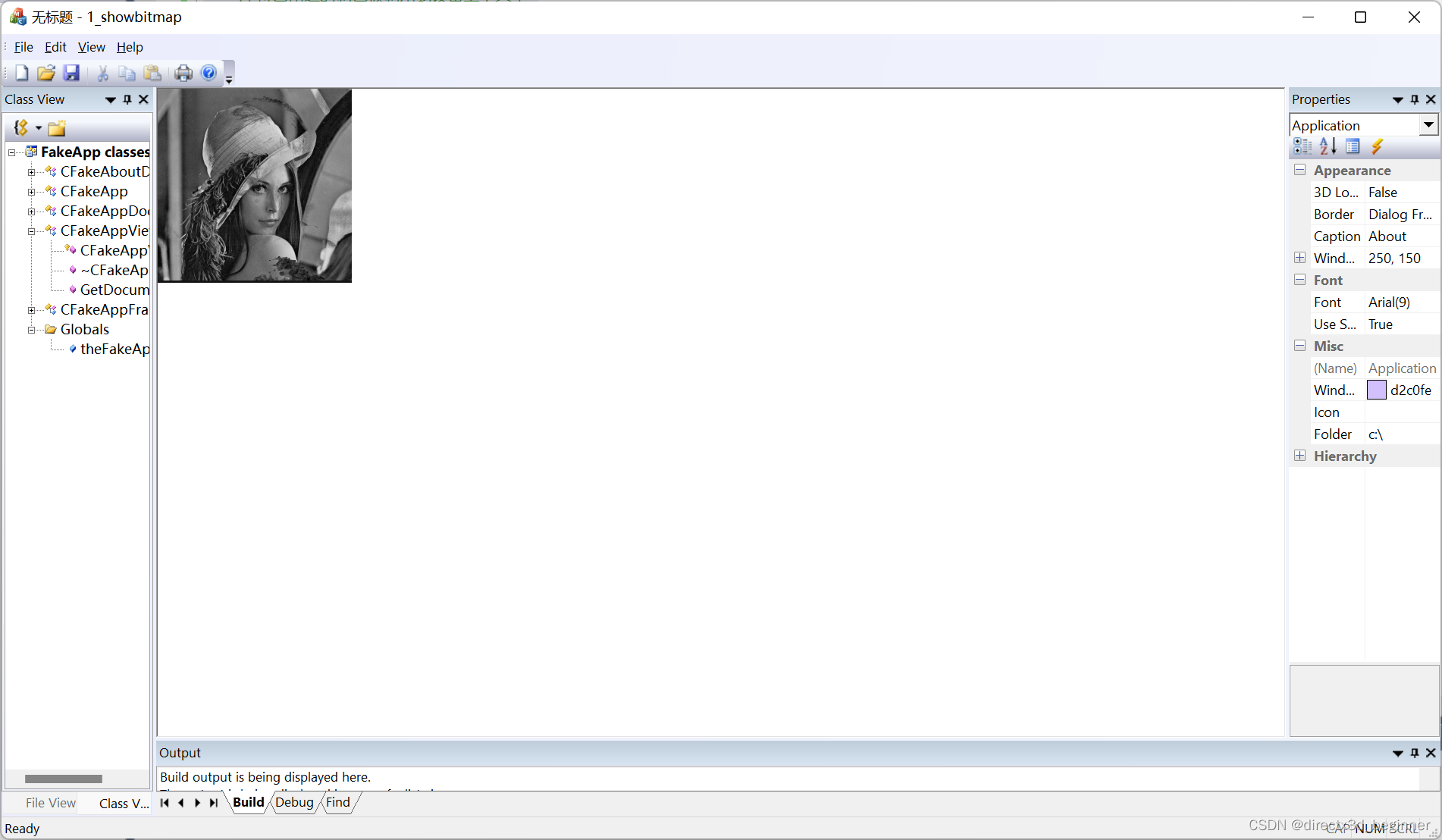

SDRAM与DDR的变化是数据变为双沿传输,DDR到DDR2的变化是IO端口时钟频率变为内核时钟频率的2倍,而内核数据位宽均变为IO端口数据位宽的2倍来弥补时钟的差异。因此DDR内部读写数据的位宽是IO端口数据位宽的2倍,DDR2内部读写数据的位宽是IO端口数据位宽的4倍。分别对应DDR的2倍预取和DDR2的4倍预取,下图是镁光的一款DDR2芯片内部框图。

图1中内部存储阵列的数据位宽为32位,图2中内部存储阵列数据位宽为64位,而两颗芯片的IO数据位宽均为16位,由此也可以看出预取的差异是2倍。

因此DDR2内核时钟为100MHz时,IO端口的时钟为200MHz,又是双沿传输数据,则DDR2的数据传输速率为400MHz。之后的DDR3的思路依旧如此,只是将IO端口的时钟频率在翻一倍而已,内核时钟频率依旧不变。

2、DDR2与DDR的不同

DDR2因为时钟频率提高了,导致一些细节也与DDR有些区别了,新增了ODT、OCD这些功能,部分时序参数也发生了变化,本小节就讲解一下这些不同的地方,对于相同的东西本文就不再赘述了。

2.1、bank数量、预取

DDR和SDRAM最多4个bank,而DDR2最多支持8个bank,bank越多意味着存储容量也越多了。

SDRAM内核时钟和外部时钟频率相同,均在上升沿传输数据,所以没有预取。而DDR的端口在双沿传输数据,所以预取为2。DDR2IO时钟变为内核时钟2倍,则预取为4。

何为预取?其实就是给读写操作准备数据,以DDR2为例,每个存储单元可以存储64位数据,而IO每次只能传输16位数据。那么IO传输4次内部才读写1次存储阵列,时钟都是为数据服务的,计算预取大小只需要用存储阵列的数据位宽除以IO端口的数据位宽即可。

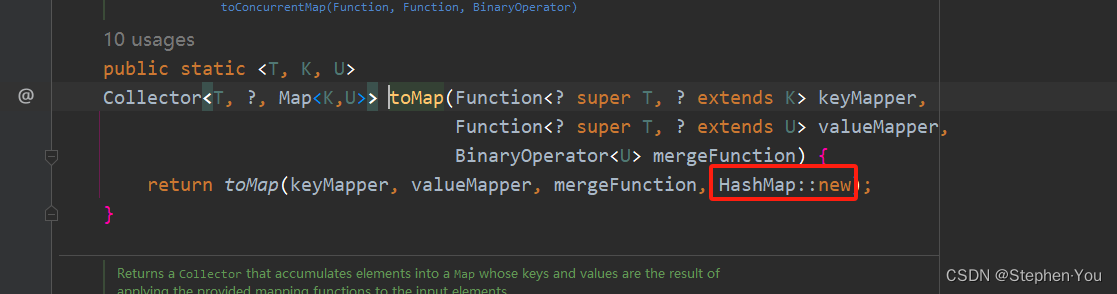

2.2、模式寄存器及初始化

SDRAM只有一个模式寄存器,DDR包含一个模式寄存器和一个扩展模式寄存器,而DDR2由于需要设置的参数增加,包括一个模式寄存器和三个扩展的模式寄存器,对应的初始化时序也有一些变化。

下图是DDR2的模式寄存器,由于预取为4,所以突发读写的长度应该为4的整数倍,由图可知DDR2只支持突发长度为4、8的读写操作。

另外CL延时的时钟个数更多,但不支持半个时钟长度的延时了。bit7用于确认DDR2工作在测试模式下还是正常模式下。bit8可以复位延时锁存回路(DLL),必须经过200个时钟周期后才能进行读操作,保证内部时钟与外部时钟同步完成。

Write Recovery是写恢复延时(写完数据后,到预充电命令前的延时),表示在一个激活的bank中完成有效的写操作以及与预充电前,必须等待多少个时钟周期。这段必须的时钟周期,用来确保在预充电发生前,写缓冲中的数据可以被写入内存单元中。较低的tWR可以提高系统性能,但可能导致数据未完全正确写入内存单元,就发生了预充电操作,导致数据的丢失和损坏。该参数对应在时序图中对应如下图所示:

扩展模式寄存器(EMR)的功能包括DLL启用/禁用、输出驱动强度、内置端接 (ODT)、AL延时设置、片外驱动器阻抗校准 (OCD)、DQS差分信号启用/禁用、RDQS差分信号启用/禁用以及输出禁用/使能,如下图所示。

DLL的功能前文已详细讲解,此处只增加了使能控制,ODT、OCD、DQS、AL延时后文讲解。RQDS是对8位IO的芯片来说的,本文这种16位的芯片可以不考虑该位。Bit12表示输出有效时,芯片的数据DQ、数据选通DQS才能工作。

扩展模式寄存器2 (EMR2) 除bit7之外的所有位均被保留,E7用于商业或高温操作。

如果温度超过85°C,bit7必须为1,以便提供更快的刷新率。

扩展模式寄存器3 (EMR3)的所有位均被保留,因此DDR2的EMR2和EMR3基本上都处于保留状态,能够使用的也只有模式寄存器(MR)和扩展模式寄存器(EMR)。

下图为DDR2的复位流程,相比DDR的复位流程需要多配置两个扩展的模式寄存器。几次配置MR和EMR的原因在于OCD和DLL的设置,所以相对较麻烦。

2.3、DQS与OCD技术

DDR相对SDRAM增加了数据选通信号DQS,DDR2数据传输的速率继续提升,为确保数据稳定性,DDR2将数据选通信号也设计成差分信号了。

DDR2在配置EMRS阶段,加入了可选的片外驱动调校(OCD,Off-Chip Driver)功能,OCD主要通过调整I/O接口端的电压来补偿上拉与下拉电阻值,让DQS与DQ数据信号之间的偏差降低到最小。这部分内容来自电脑高手的讲解。

调校期间,分别测试DQS高电平/DQ低电平,与DQS低电平/DQ高电平的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出OCD操作。

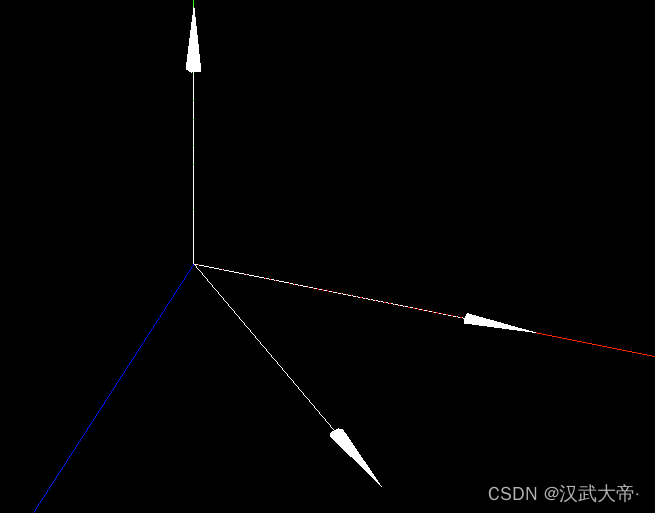

如下图所示,在OCD调校之前,DQS与DQS#交叉点位于参考电压上边,此时以DQS与DQS#交叉点采集DQ的数据就会导致错误。通过OCD调节之后,上拉电阻与下拉电阻相等,此时DQS与DQS#交叉点基本上位于参考电压上,与DQ和参考电压的交叉点基本重合,实现数据DQ与DQS边沿对齐。

OCD的作用在于调整DQS与DQ之间的同步,以确保信号的完整与可靠性。但一般情况下采用差分DQS基本就可以保证同步的准确性,且OCD的调整对其他操作有影响,因此OCD只会出现在高端产品中,如对数据完整性非常敏感的服务器等。

2.4、片内终结(ODT,On-Die Termination)

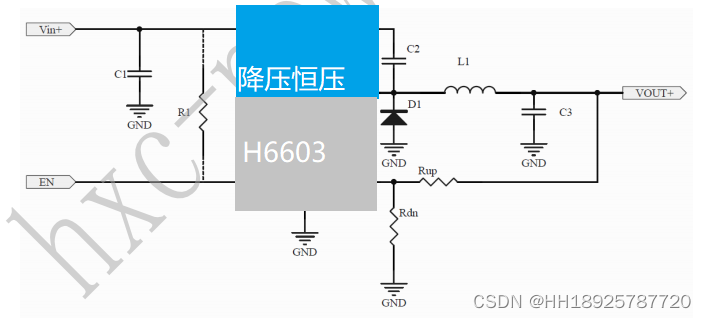

终结就是让信号被电路的终端电阻吸收掉,不在电路上形成反射,造成对后面信号的影响,下图所示框中的电阻部分就是实现ODT的电阻电路。

在DDR时代,控制与数据信号的终结电阻在PCB上完成,每块DDR PCB板上在DIMM槽的旁边都会有一个终结电压岛的设计,它主要由一排终结电阻构成。长期以来,这个电压岛一直是DDR PCB设计上的难点。

而ODT的出现,则将这个难点消灭了。ODT就是将终结电阻移植到了芯片内部,主板上不在有终结电路。ODT的功能与禁止由主控芯片控制,ODT所终结的信号包括DQS、RDQS(8位IO芯片的DQS信号)、DQ、DM等。

那么具体的终结操作如何实现呢?首先要确定系统中有几条模组,并因此来决定终结的等效电阻值,有150Ω、100Ω、75Ω三档,这一切由主控芯片在开机进行EMRS时进行设置。EMR的bit6和bit2通过控制sw1、sw2、sw3的状态来启用哪种ODT电阻,使能开关sw1使能R1值为150Ω,从而实现75Ω的等效电阻。如果sw2使能R2值为300Ω,从而实现150Ω的等效电阻。开关sw3使能R3值为100Ω,从而实现50Ω的等效电阻。

这部分的解释主要与PCB设计和PC的电脑内存有关,我们直接看电脑高手的讲解吧,芯片手册没有具体给功能介绍。

在向内存写入时,如果只有一条DIMM,那么这条DIMM就自己进行终结,终结电阻等效为150Ω。如果为两条DIMM,一条工作时,另一条负责终结,但等效电阻为75Ω,如下图所示。

在从内存读出时,终结操作也将在北桥内进行,如果有两条DIMM,不工作的那一条将会终结信号在另一方向的余波,等效电阻也因DIMM的数量而有两种设置。

两个DIMM在交错工作中的ODT情况,第一个模组工作时,第二个模组进行终结操作,等第二个模组工作时,第一个模组进行终结操作。

现在基本了解了ODT的功能,在很大程度上减少了内存芯片在读取时的I/O功率消耗,并简化了PCB的设计,降低了主板成本。而且ODT也要比PCB的终结更及时有效,从而也成为了提高信号质量的重要功能,有助于降低后续产品进一步提速的难度。但由于为确保信号的有效终结,终结操作期将会比数据传输期稍长,从而多占用一个时钟周期的时间而造成总线空闲。

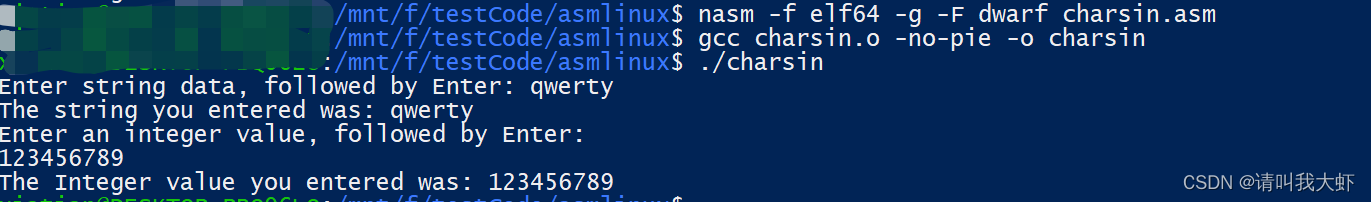

2.5、前置CAS、附加潜伏期与写入潜伏期

下图是DDR的读写时序,在发出行激活命令之后,必须经过tRCD后才能发送读、写命令。

如下图所示,DDR2在发送完行激活命令后,下个时钟就可以发出读、写命令,之后的一段时间就把地址总线空出来了,避免造成命令冲突而被迫延后的情况发生。

注意写命令只是提前发出了,tRCD的延时并没有变化,与DDR相比就是写命令提前,提前的这段时间被称为前置CAS(Posted CAS)。

上述读、写操作并没有因此而提前,仍有要保证有足够的延迟/潜伏期,为此,DDR2引入了附加潜伏期(AL,Additive Latency),与CL一样,单位为时钟周期数。AL+CL-1被定义为写入潜伏期(WL,Write Latency),表示从发出写命令到第一个数据的间隔时间。

对于读操作,也有相应的读取潜伏期(RL,Read Latency),如下图所示,RL=AL+CL,表示发送读命令后到第一个数据被读出的时间。

3、总结

DDR与DDR2的区别就上述这么多了,主要就是因为内核时钟与接口时钟频率不一样,接口时钟频率提升后,为在较高时钟频率下依旧能够稳定收发数据所做出的一些改变,相应变化总结如下:

1. 接口时钟频率变为内核时钟频率的2倍,随之预取变为4倍,突发长度是预取整数倍,只支持4和8。

2. 为稳定数据的传输,数据选通信号变为差分信号。

3. DDR2提升到8个bank容量,对应的bank地址线增加1位,容量提升1倍。

4. CL的值增加了,并且在发出行激活命令后,可以在下个时钟上升沿直接发出读、写指令,相当于将读写指令提前,早点空出地址线,避免因为总线冲突引起的延时。但激活指令之后的延时还是存在的,由附加潜伏期AL替代,所以读潜伏期等于AL+CL,写潜伏期等于AL+CL-1。

5. 增加了OCD校准技术,更加确保DQ与DQS数据传输的准确性。

6. DDR2把DDR设计中PCB上的终结电阻引入到芯片内部,从而简化PCB的设计,并且能够更有效。

DDR到DDR2的转变与DDR2到DDR3的转变原理其实类似,都是提升IO接口的时钟频率,使得数据传输速率提升,只不过当时钟频率提升到一定程度后,就需要修改或者增加一些小功能来确保数据在高速时钟下传输的正确性。

需要获取本文使用手册和文档的在公众号后台回复“DDR手册”(不包括引号),包括镁光的SDRAM到DDR4芯片手册及DDR的芯片设计规范手册。

您的支持是我更新的最大动力!将持续更新工程,如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!