VHDL对象包括:信号、变量、常量和运算符。

信号

在中声明VHDL信号:

•体系结构声明部分:在该体系结构内的任何位置使用VHDL信号。

•一个块:在该块中使用VHDL信号。

使用<=信号分配运算符分配VHDL信号。

signal sig1 : std_logic;

sig1 <= '1';

变量

VHDL变量为:

•在进程或子程序中声明。

•在该过程或子程序中使用。

•使用:=赋值运算符进行赋值。

variable var1 : std_logic_vector (7 downto 0); var1 := "01010011";

常量

您可以在任何声明性区域中声明VHDL常量。常数用于区域在声明常数值之后,不能更改它们。

signal sig1 : std_logic_vector(5 downto 0);constant init0 :

std_logic_vector (5 downto 0) := "010111";sig1 <= init0;

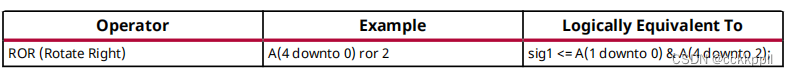

操作

Vivado合成支持VHDL运算符。

轮班操作示例

VHDL实体描述

VHDL电路描述

VHDL电路描述(设计单元)包括以下内容:

•实体声明:提供电路的外部视图。描述从中可见的对象外部,包括电路接口,如I/O端口和泛型。

•体系结构:提供电路的内部视图,并描述电路行为或结构

VHDL实体声明

电路的I/O端口在实体中声明。每个端口都有一个:

•名称

•模式(输入、输出、输出、缓冲)

•类型

受限端口和非受限端口

定义端口时,端口:

•可受约束或不受约束。

•通常受到限制。

•在实体声明中可以不受约束。

○ 如果端口不受约束,则在连接时实例化时定义其宽度在正式端口和实际信号之间进行。

○ 无约束端口允许您创建同一实体的不同实例,定义不同的端口宽度。

建议:不要使用不受约束的端口。定义通过泛型约束的端口。

在实例化时应用这些泛型的不同值。在顶级实体上不要有不受约束的端口。

不接受多个维度的数组类型作为端口。实体声明可以也声明VHDL泛型。

缓冲端口模式

建议:不要使用缓冲端口模式。

VHDL允许在内部使用信号时使用缓冲端口模式,并在以下情况下用作输出端口只有一个内部驱动程序。缓冲端口是合成期间的潜在误差源,并通过模拟使合成后结果的验证复杂化。

NOT RECOMMENDED Coding Example WITH Buffer Port Mode

entity alu is

port(

CLK : in STD_LOGIC;

A : inSTD_LOGIC_VECTOR(3 downto 0);

B : inSTD_LOGIC_VECTOR(3 downto 0);

C : buffer STD_LOGIC_VECTOR(3 downto 0));

end alu;

architecture behavioral of alu is

begin

process begin

if rising_edge(CLK) then

C <= UNSIGNED(A) + UNSIGNED(B) UNSIGNED(C);

end if;

end process;

end behavioral;

丢弃缓冲区端口模式

建议:丢弃缓冲端口模式。

在前面的编码示例中,信号C是用缓冲模式建模的,并且两者都使用内部和作为输出端口。可以连接到C的每个层次结构级别也必须声明为缓冲区。

要删除缓冲区模式:

1.插入一个伪信号。

2.将端口C声明为输出。

RECOMMENDED Coding Example WITHOUT Buffer Port Mode

entity alu is

port(

CLK : in STD_LOGIC;

A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

C : out STD_LOGIC_VECTOR(3 downto 0));

end alu;

architecture behavioral of alu is

-- dummy signal

signal C_INT : STD_LOGIC_VECTOR(3 downto 0);

begin

C <= C_INT;

process begin

if rising_edge(CLK) then

C_INT <= A and B and C_INT;

end if;

end process;

end behavioral;

VHDL Architecture Declarations

You can declare internal signals in the architecture. Each internal signal has a name and a type.

VHDL Architecture Declaration Coding Example

library IEEE;

use IEEE.std_logic_1164.all;

entity EXAMPLE is

port (

A,B,C : in std_logic;

D,E : out std_logic );

end EXAMPLE;

architecture ARCHI of EXAMPLE is

signal T : std_logic;

begin

...

end ARCHI;