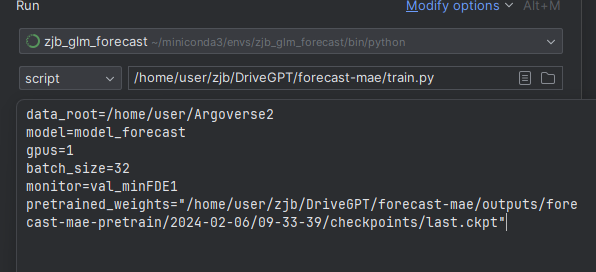

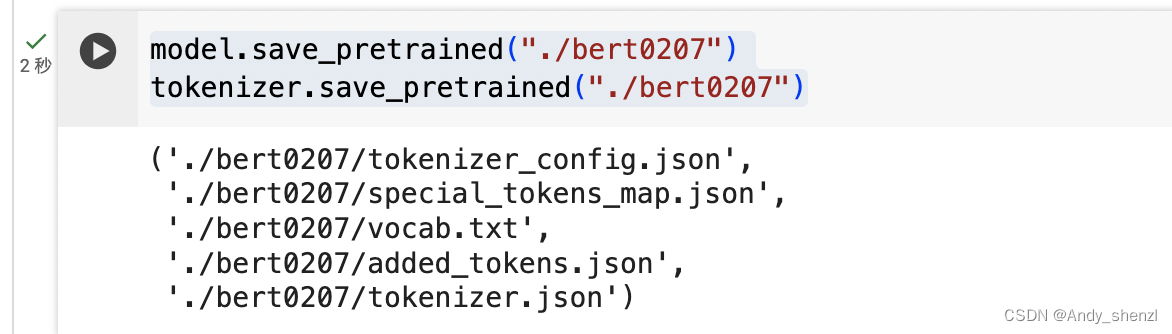

题目:

Case statements in Verilog are nearly equivalent to a sequence of if-elseif-else that compares one expression to a list of others. Its syntax and functionality differs from the switch statement in C.

解题:

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'b000: out=data0;

3'b001:out=data1;

3'b010:out=data2;

3'b011:out=data3;

3'b100:out=data4;

3'b101:out=data5;

default:out=0;

endcase

end

endmodule

或者另外一种答案:

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'd0: out <= data0; //case语句里面阻塞赋值和非阻塞赋值都可以

3'd1: out <= data1;

3'd2: out <= data2;

3'd3: out <= data3;

3'd4: out <= data4;

3'd5: out <= data5;

default: out <= 0;

endcase

end

endmodule

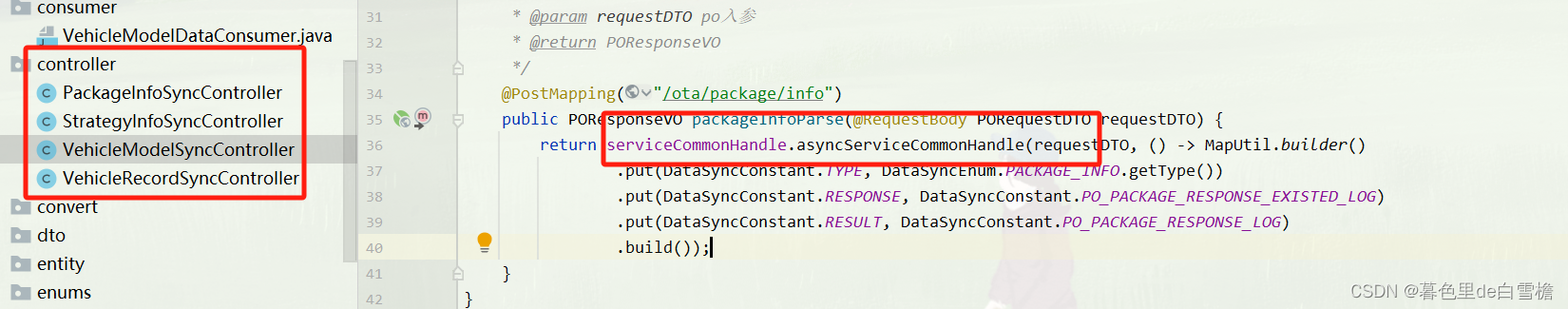

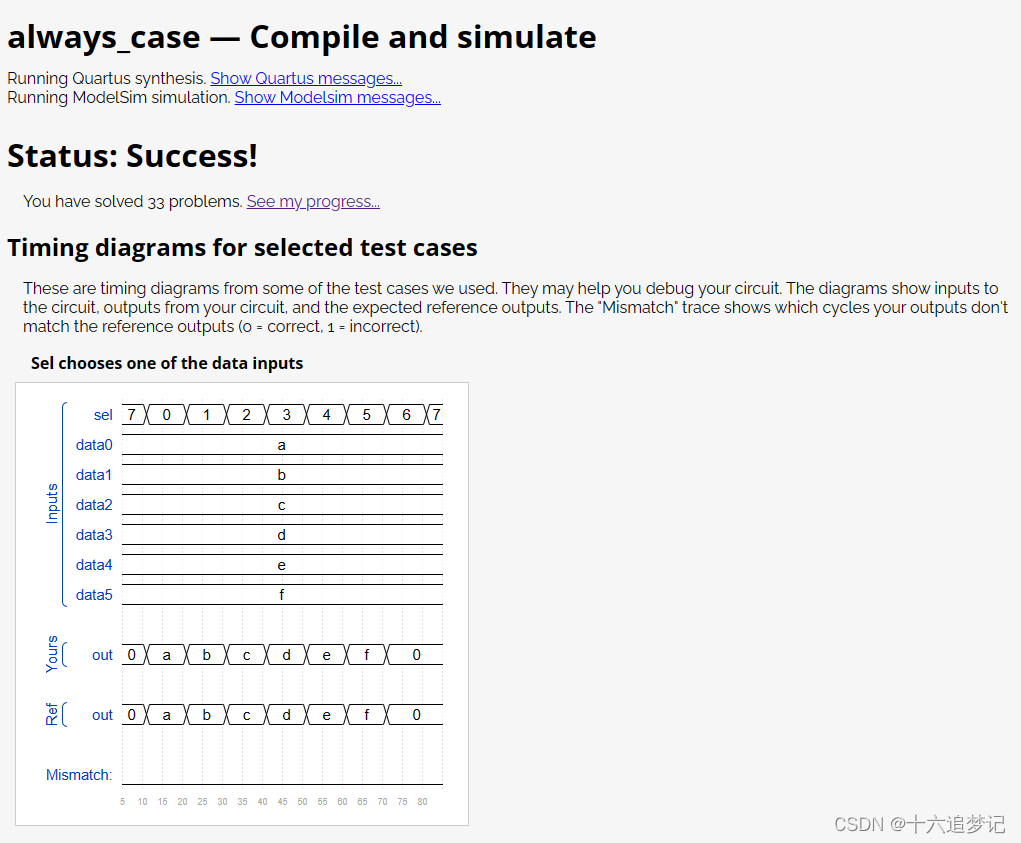

结果正确:

注意点:

两种赋值的区别:

在 Verilog 中, blocking 赋值和非阻塞赋值是不同的。在第一段代码中,采用的是阻塞赋值(=);而在第二段代码中,采用的是非阻塞赋值(<=)。

使用阻塞赋值时,赋值语句的执行是按顺序依次完成的,一个赋值语句的执行不会影响到下一个赋值语句的执行。而使用非阻塞赋值时,赋值语句相当于并行执行,即使第一个赋值语句的结果影响到了后面的赋值语句,也不会改变后面赋值语句的执行结果。

在这种情况下,由于这些赋值语句之间没有顺序相关性,因此无论你使用阻塞赋值还是非阻塞赋值,都不会对结果产生影响。所以,这两种赋值方式在这个例子中并没有明显的区别。

对于组合逻辑,一般情况下使用阻塞赋值和非阻塞赋值并不会产生实质性的区别。但是在时序逻辑中,使用非阻塞赋值是一种良好的编程风格,可以避免一些意外的逻辑错误。

![IAR报错:Error[Pa045]: function “halUartInit“ has no prototype](https://img-blog.csdnimg.cn/direct/dd80ac0e3da6430ca49ba1b50c6e1219.png)