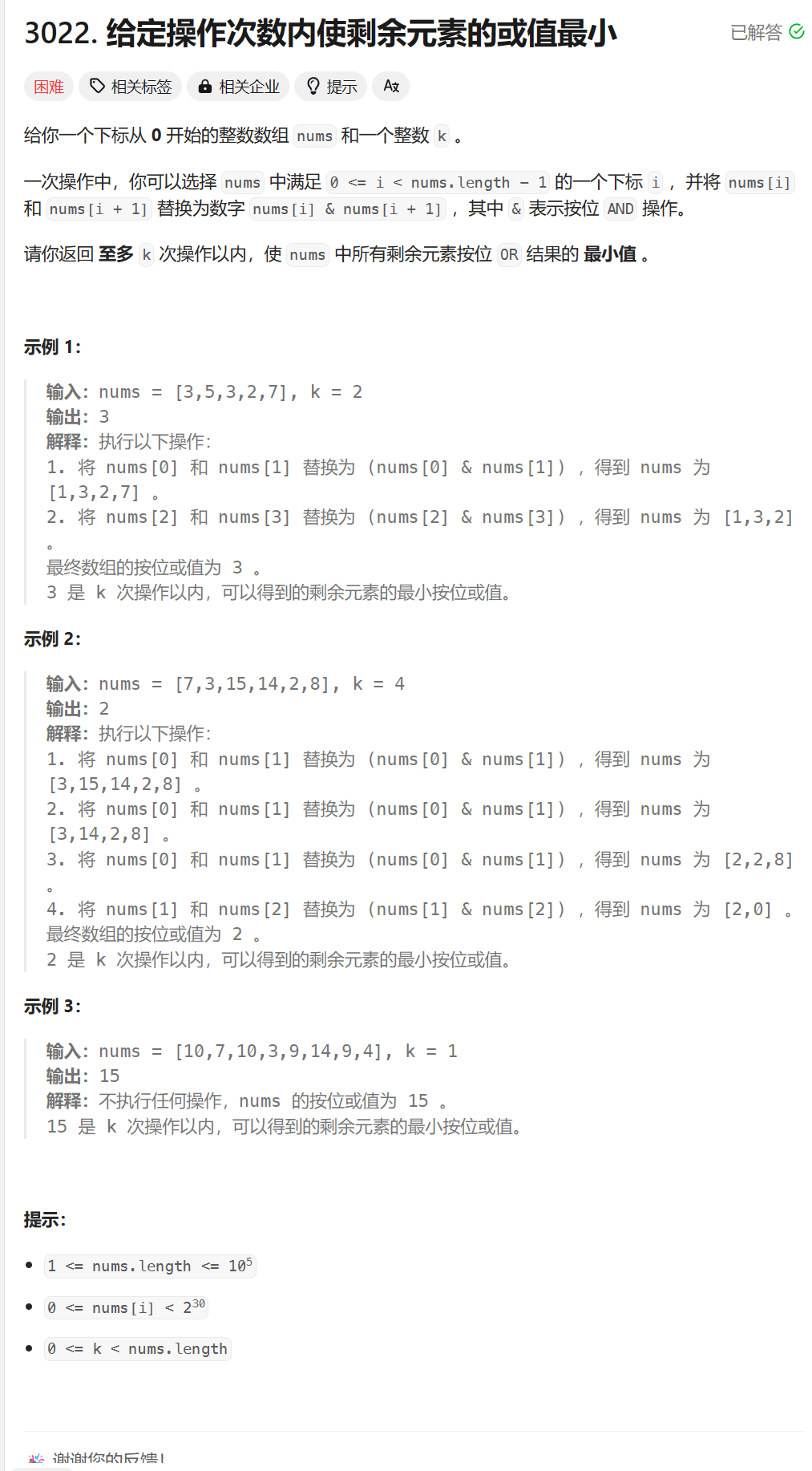

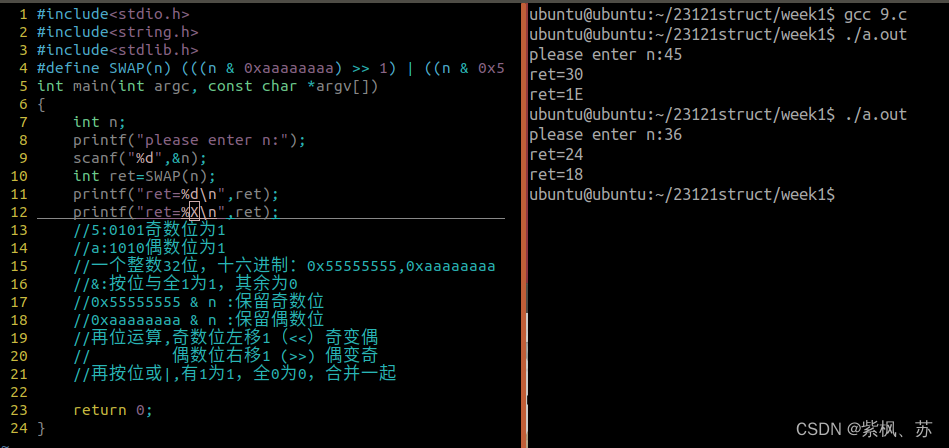

题目:

A common source of errors: How to avoid making latches

When designing circuits, you must think first in terms of circuits:

I want this logic gate

I want a combinational blob of logic that has these inputs and produces these outputs

I want a combinational blob of logic followed by a set of flip-flops

What you must not do is write the code first, then hope it generates a proper circuit.

If (cpu_overheated) then shut_off_computer = 1;

If (~arrived) then keep_driving = ~gas_tank_empty;

Syntactically-correct code does not necessarily result in a reasonable circuit (combinational logic + flip-flops). The usual reason is: “What happens in the cases other than those you specified?”. Verilog’s answer is: Keep the outputs unchanged.

This behaviour of “keep outputs unchanged” means the current state needs to be remembered, and thus produces a latch. Combinational logic (e.g., logic gates) cannot remember any state. Watch out for Warning (10240): … inferring latch(es)" messages. Unless the latch was intentional, it almost always indicates a bug. Combinational circuits must have a value assigned to all outputs under all conditions. This usually means you always need else clauses or a default value assigned to the outputs.

解题:

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer=0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving =0;

end

endmodule

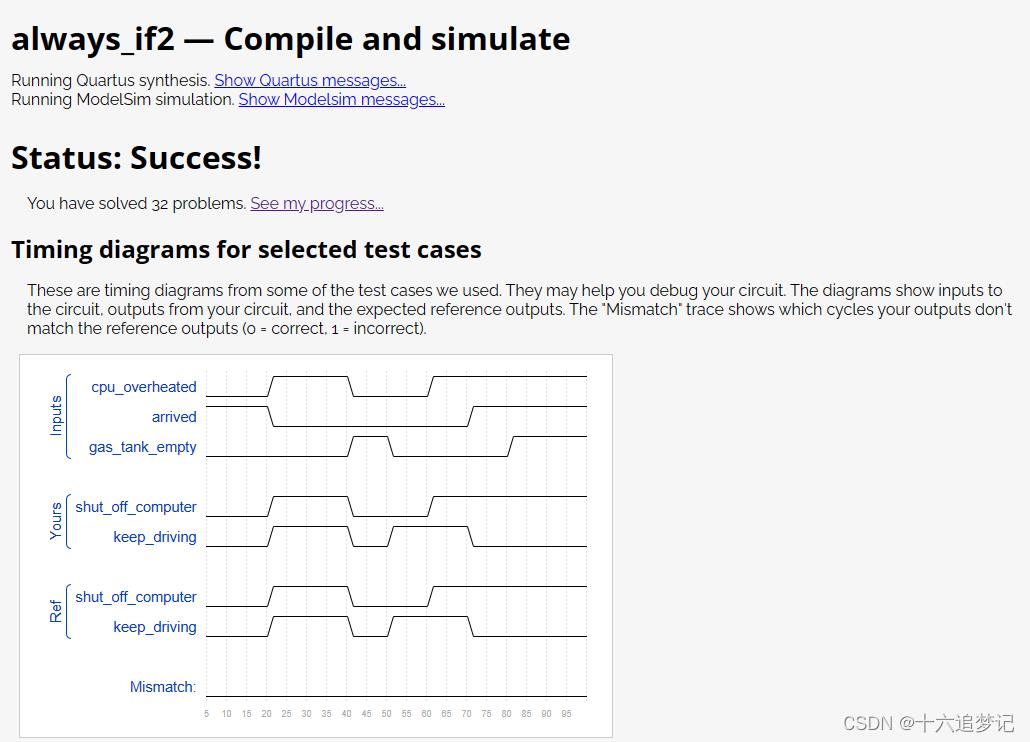

结果正确:

本题注意点:

组合逻辑中,如果if缺少else语句,或是自己赋值给自己的情况就会产生latch。为了避免latch产生,if需要加上else语句,覆盖所有可能。

![pwn旅行之[WUSTCTF 2020]getshell2(一些小知识)](https://img-blog.csdnimg.cn/direct/05311b5e2604406485f6c1fe4ac06356.png)