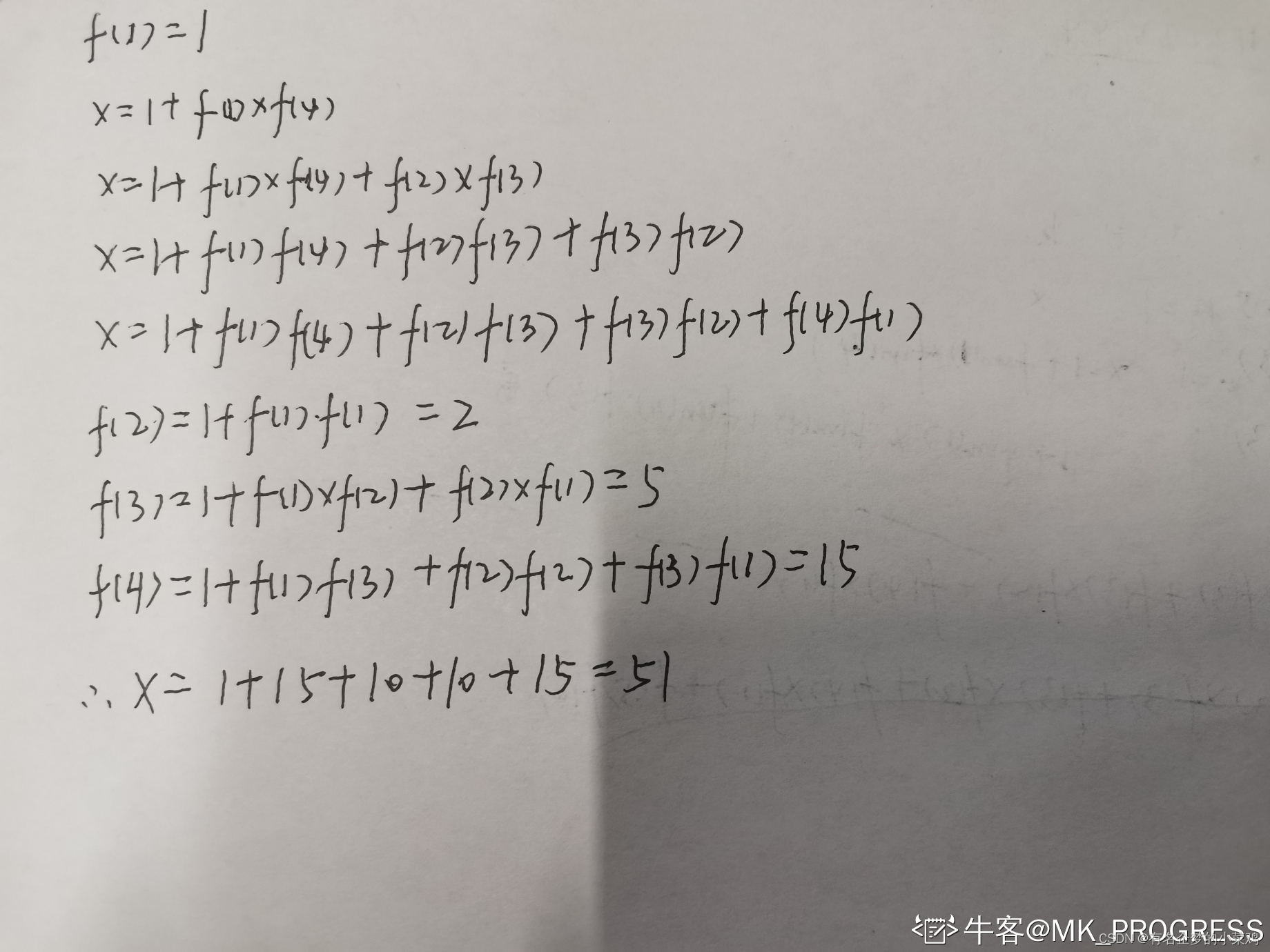

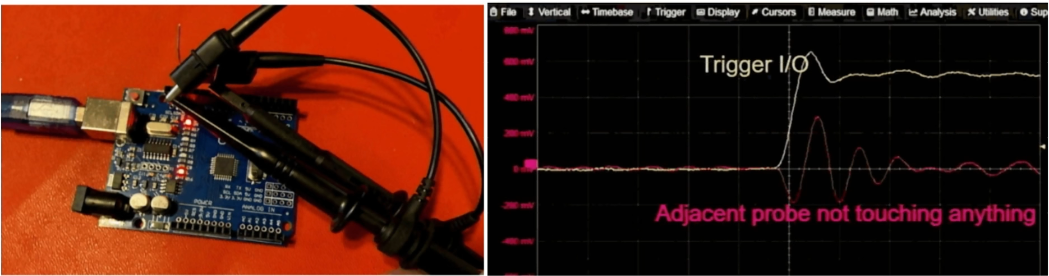

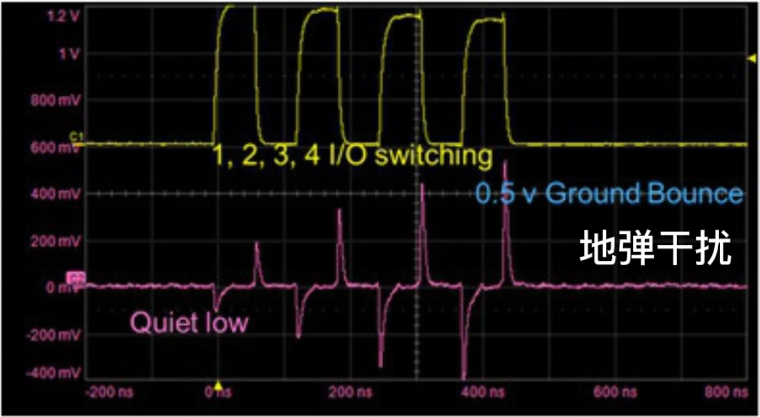

过大的分布电感导致信号地干扰也就是地弹(专业名词)

还有就是输出瞬态电流导致的地弹

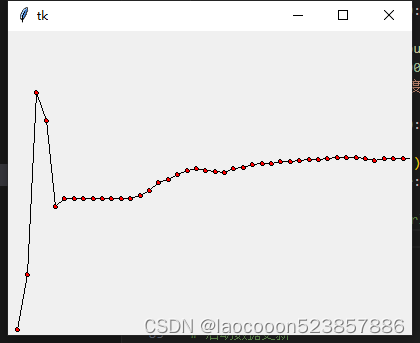

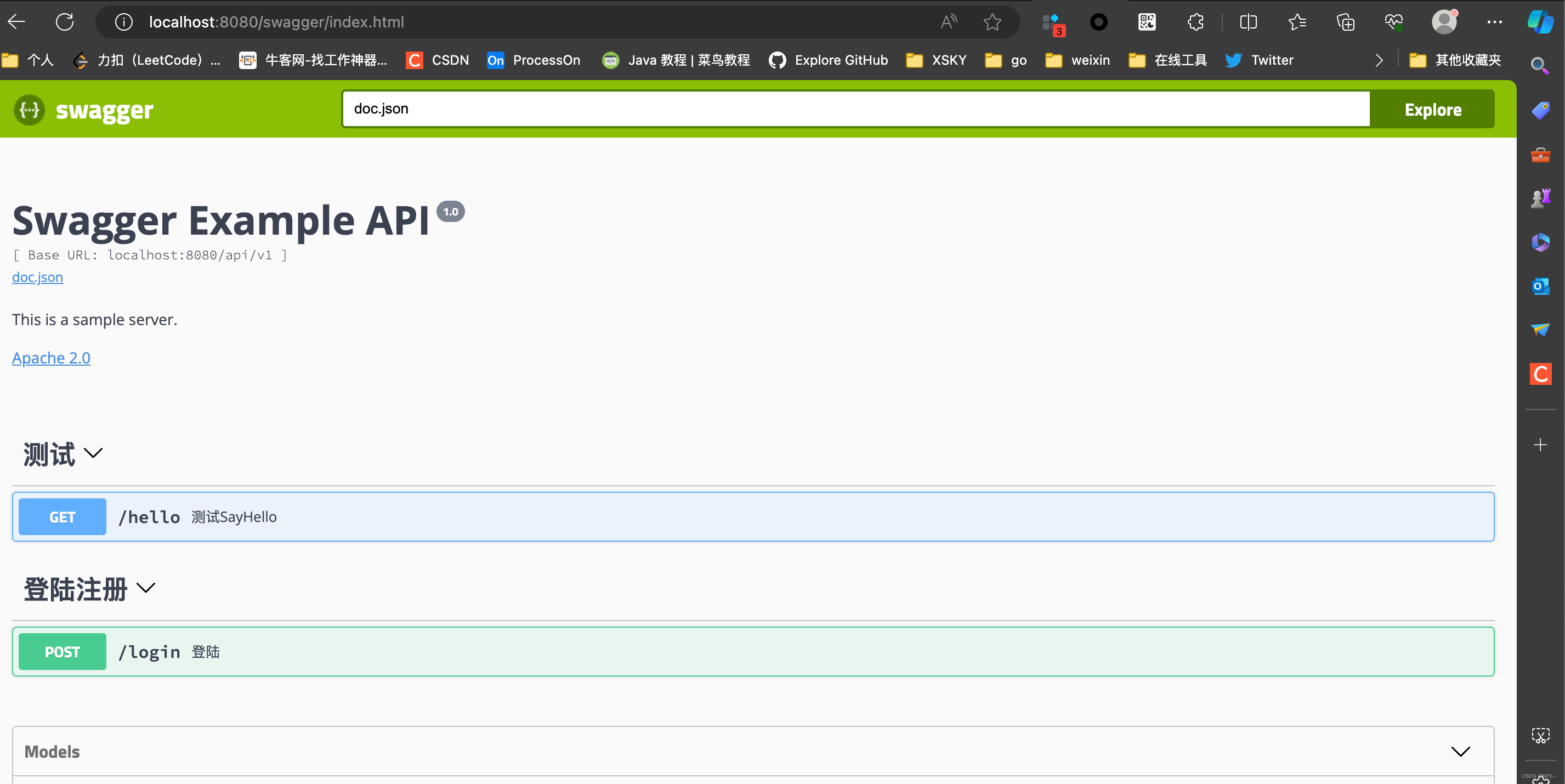

图中可以看到最高 0.5V 的信号地干扰,这只是单一块开发板的测试结果。如果接上外围电路,甚至面包板电路可以想象噪声水平可能会更高。

双面电路板 经验规则

下面来看看这几条规则是什么样的

1线宽设置

信号线 6 mil(0.15mm)

电源线 20 mil(0.5mm)

过孔钻孔直径 13 mil(0.33mm)

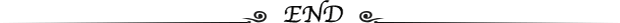

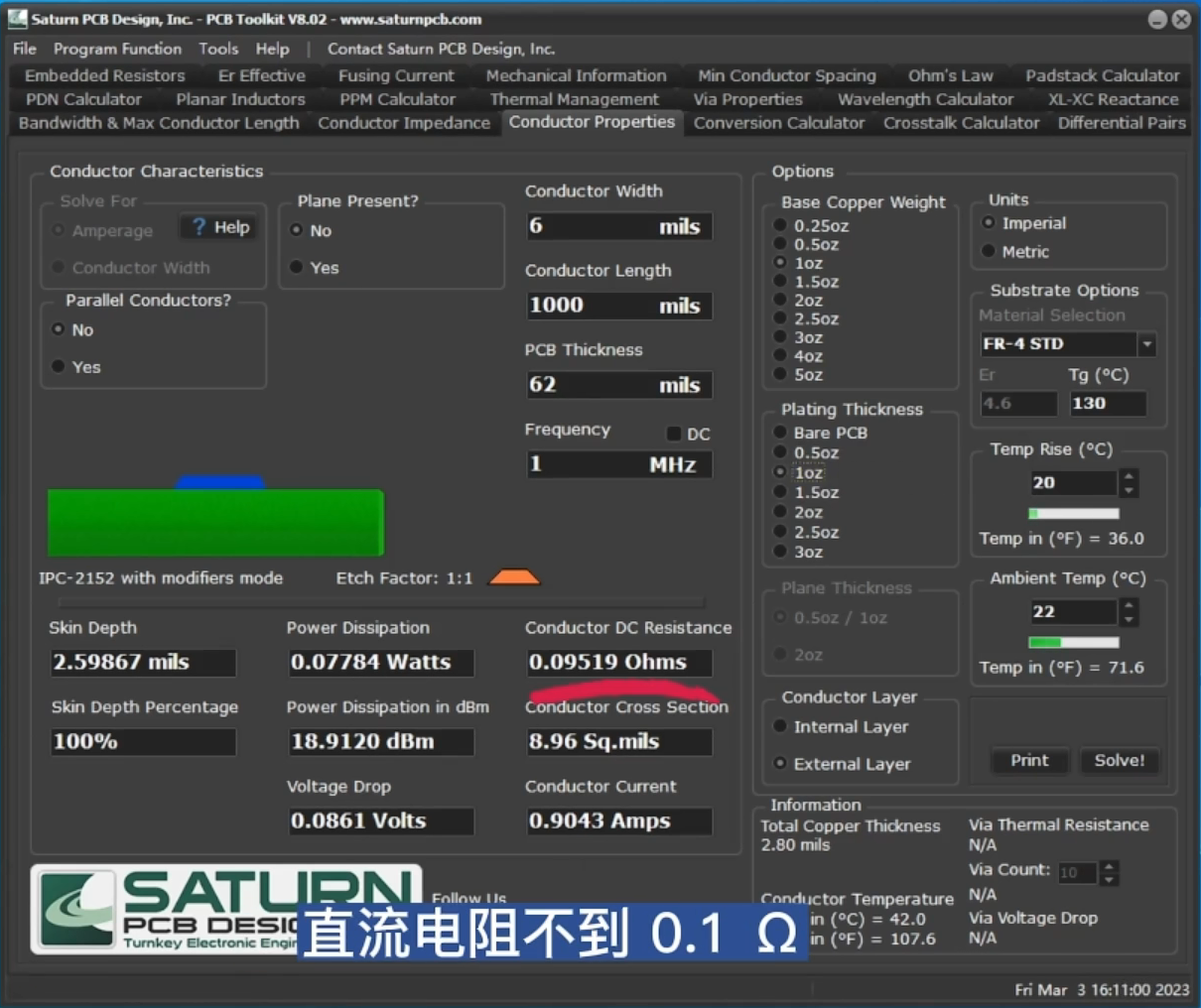

大家都会觉得走线太细了!!! 其实不然从下面工具可以看出

直流电阻不到 0.1 可承受差不多 1A 的直流 ~

一般电路板信号走线的电阻怎么也不会超过 1Ω。 1 GHz 以下的应用中,这点损耗完全可以忽略, 对于常见的 1.6 毫米(62mils) 双面板 6 mils走线的特征阻抗差不多150Ω。只要信号线不用输出到板外。

再来看电源走线的宽度1oz,20 mils宽的走线可承受 2.4A 直流。

温度从22度上升到42度 1,000 mils 长电阻才0.02 Q。

2层设置

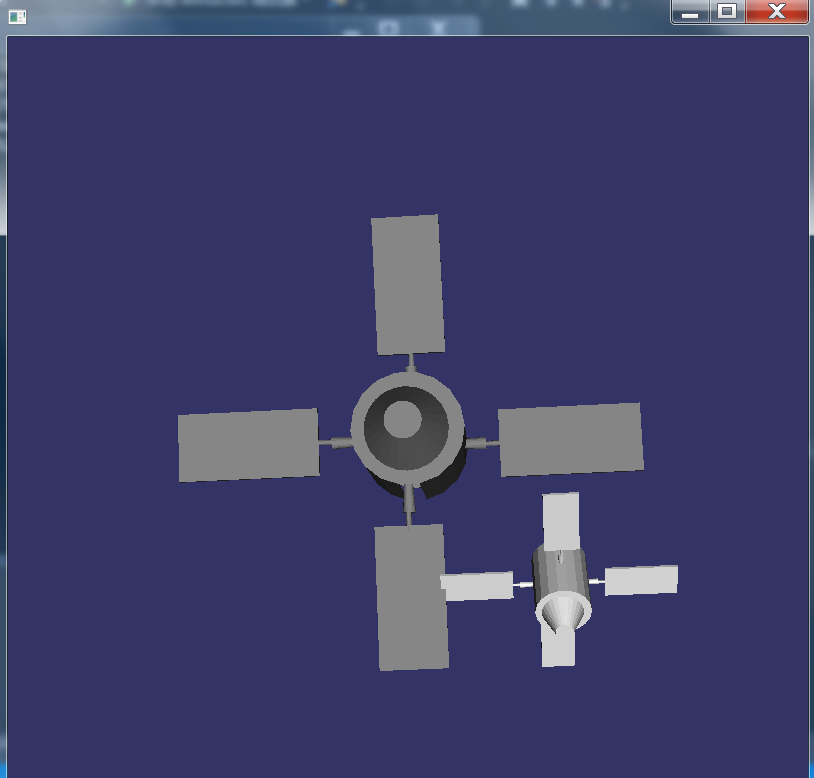

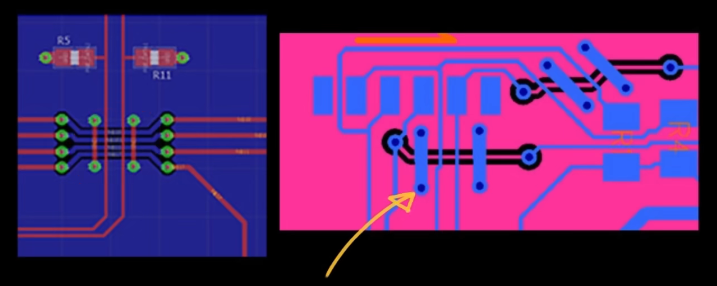

底层为完整地平面顶层放置元件、走信号和电源线。

每条信号线下方都有连续的回流路径 所以底层越完整越好。

3分散布局

避免走线集中聚在一起。

信号线间留足够空间,以减小串扰。

4 回流路径

尽量避免在地层走线,保证地平面完整性。

添加回流路径。

已需要在底层走线则必须尽量短。

PS:顶层,底层,或者说任意一层铺铜都需要考虑铺铜宽度和长度的关系。铺铜,形成信号包地是最优解,但注意平行信号线中间夹的铜皮必须良好与大平面地相连,也就是每隔一段距离打一个地过孔与其他层的地相连,以减小地阻抗,这样的铺铜才有意义,否则就别铺。

5去耦电容

靠近 IC 电源管脚放置去耦电容。通常用一个 22uF 的MLCC电容。

使连线尽量短而且宽,以减少分布电感。

比容量更重要的是要减少电源管脚与电容之间的电感,有时候需要多个电容并联。

6输入输出地

为每个IO口配备地线。

给每个数字信号线,都安排一个地的针脚。

7过时的规则

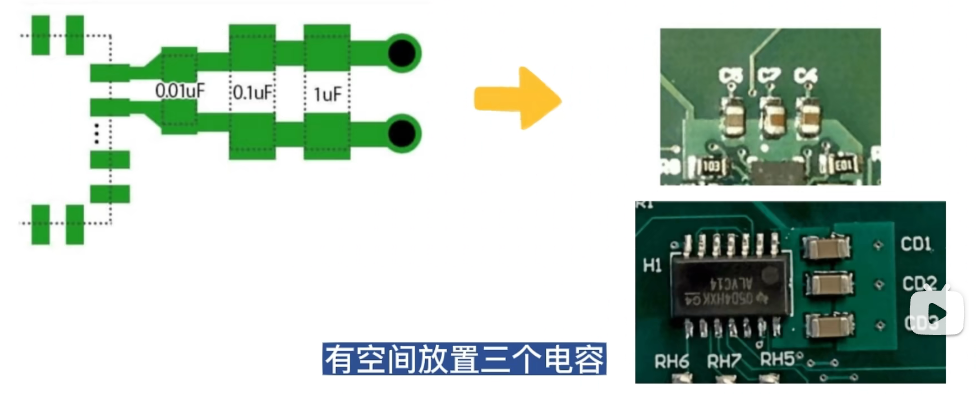

不要使用大小不同的电容并联来做去耦电容。

有空间放置三个电容,不如放置三个容量相同的MLCC 电容。

PS:对于这个建议不太认同

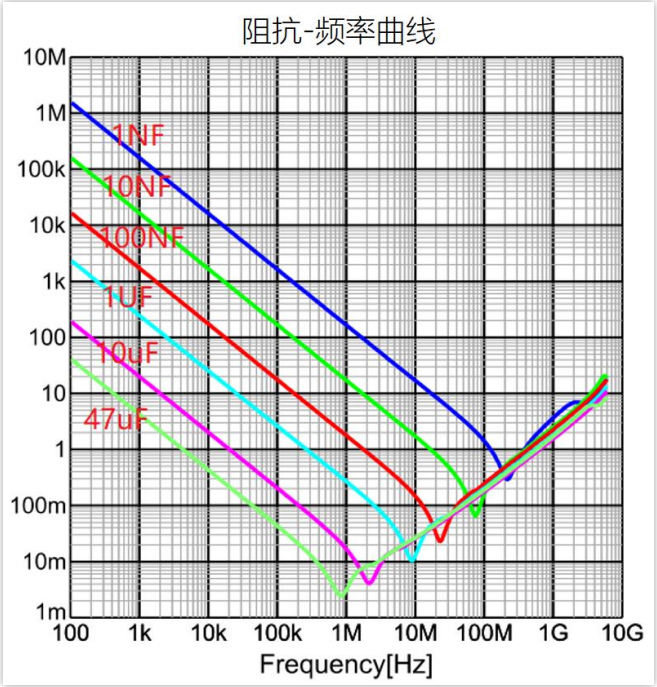

电容在不同大小封装和不同大小容值的的情况下,他的谐振频率也不一样。

3个容量一样的电容搭配,叫做“V型滤波”,因为频率特性就呈现一个V字,此时,要注意电路频率范围,必须保证你的滤波电容要时刻呈现容性。

3个容量不同的电容搭配,滤波频率响应更宽更好,但是不同容量的电容会形成反谐振,所以推荐电容之间大小要相差两个数量级。但即使这样反谐振仍然不会消失,必须防止噪声频率落在反谐振点上。

总之各有各的好处,但关键是一定对电路的噪声频率有个大致的预估。盲目的搭配电容可能反而恶化噪声。

还有关于电容封装的选择。首先,贴片的一定优于插件的,因为形成的寄生电感更小。但也不是说,选了贴片的就万事大吉了,贴片电容的引脚布线不能又细又长,应该又粗又短。其次,贴片中的封装,在布局和成本允许的情况下,能选用大封装的就选用大封装,因为损耗角和温度特性,以及等效电阻都比小封装要更好。

封装1206以上的,不赞同使用,陶瓷叠层电容,容量跟物理形状有很大的关系,电容的封装越长,在电路板中承受的相同的应力的情况下,形变就越严重,导致电容的容值就偏差的越大。

同一容量的,封装越大,ESR越大。但是同一封装的,电容越大,ESR越小。大封装中,你可以轻易的选取较大容值,ESR可以比较小,损耗角小,发热小,寿命可以更长。当然也不绝对,还要考虑成本,PCB布局空间,电源回流路径等等。

7过时的规则

1.不要使用大小电容并联2。顶层不要灌水铺铜

电源要布成线,不要大面积铺铜

信号线之间也不要铺铜

有空间铺铜 说明信号线隔开已经足够了