Vivado-IP核

主程序

`timescale 1ns / 1ps

//

//

module ip_clk_wiz(

input sys_clk,

input sys_rst_n,

output clk_out1,

output clk_out2,

output clk_out3,

output clk_out4,

output locked

);

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

.clk_out4(clk_out4), // output clk_out4

// Status and control signals

.reset(sys_rst_n), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk)); // input clk_in1

endmodule

仿真代码

`timescale 1ns / 1ps

//

//

module tb_ip_clk_wiz();

reg sys_clk ;

reg sys_rst_n ;

wire clk_100M ;

wire clk_100M_180de ;

wire clk_50M ;

wire clk_25M ;

wire locked;

initial begin

sys_clk=1'b0;

sys_rst_n=1'b1;

#200

sys_rst_n=1'b0;

end

always #10 sys_clk=~sys_clk;

ip_clk_wiz ip_clk_wiz_u(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.clk_out1(clk_100M),

.clk_out2(clk_100M_180de),

.clk_out3(clk_50M),

.clk_out4(clk_25M),

.locked(locked)

);

endmodule

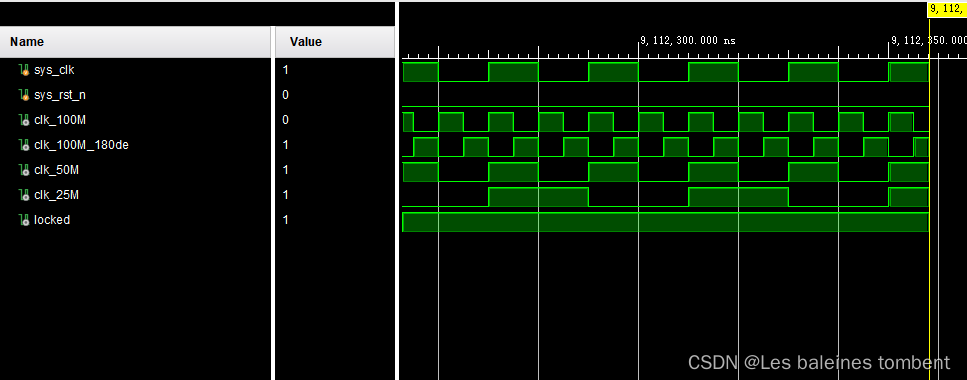

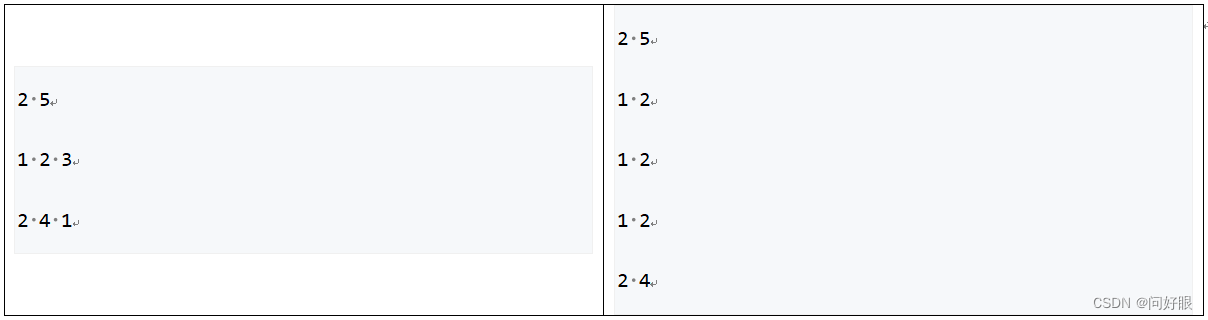

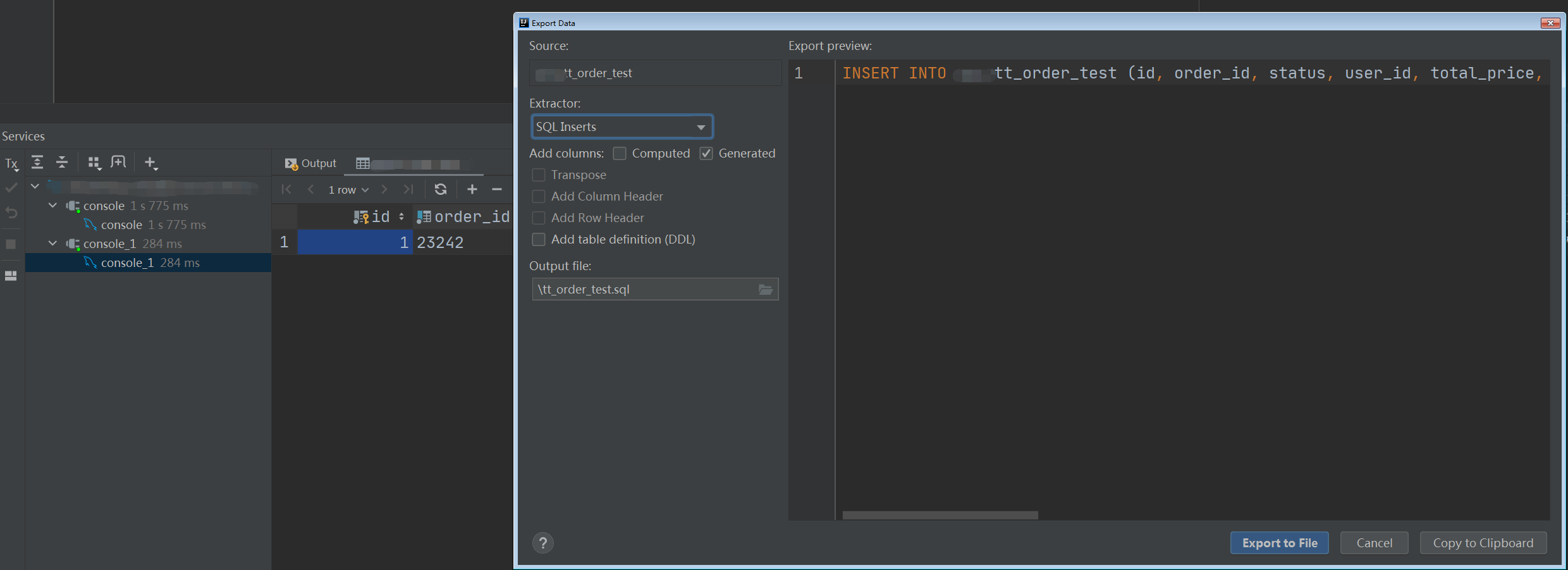

结果