配置I/O端口

AMD设备支持可配置的SelectIO™ 接口驱动程序和接收器,支持各种标准接口。这些标准接口包括输出的可编程控制强度和转换速率,使用DCI的片上终端,以及内部VREF的生成。你可以配置一个或多个I/O端口以定义I/O标准、驱动器强度、转换类型、拉动类型,以及在任期内。这对于配置从CSV或XDC文件导入的端口非常有用适当的特性。配置这些端口以支持所需的标准系统级设计。例如,您可以在一个I/O组中组合一些I/O标准但其他人不行。有关I/O组的标准和要求的信息,请参阅以下内容,具体取决于您的设备:

•7系列FPGA SelectIO资源用户指南(UG471)

•UltraScale体系结构SelectIO资源用户指南(UG571)

有关包装和引脚规格的信息,请参阅以下内容,具体取决于您的装置

•7系列FPGA封装和引脚输出产品规范(UG475)

•UltraScale和UltraScale+FPGA封装和引脚产品规范(UG575)

•Zynq-7000 SoC封装和引脚输出产品规范(UG865)有关AMD Zynq的详细信息™ 7000引脚,包括MIO引脚,参见Zynq-7000 SoC技术参考手册(UG585)。有关Zynq UltraScale+MPSoC引脚(包括MIO引脚)的详细信息,请参阅ZynqUltraScale+设备技术参考手册(UG1085)。要配置一个端口或一组端口,请执行以下操作:

1.在I/O端口窗口中,选择端口。

2.右键单击,然后选择“配置I/O端口”。

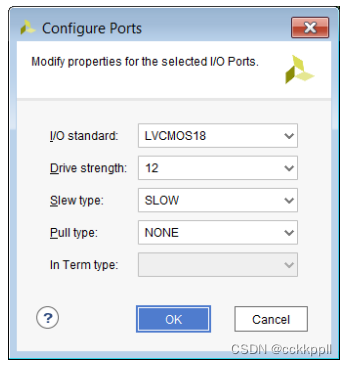

3.在“配置端口”对话框(请参阅下图)中,编辑以下选项,然后单击“确定”。

注意:配置端口对话框选项因目标设备而异。

•I/O标准:选择I/O标准约束。该工具不检查I/O标准当它被分配时。您可以将任何I/O标准分配给任何端口,但这可能会导致运行DRC时出错。

•驱动强度:选择驱动强度值。

•回转类型:选择回转类型值。

•拉动类型:选择拉动类型值。

•PULLUP:在3态输出或双向端口上应用弱逻辑高电平以防止其在未被驱动时浮动。

•下拉:在3态输出或双向输出上应用弱逻辑低电平端口,以防止其在未被驱动时浮动。

•KEEPER:在3态输出或双向端口上应用弱驱动程序在不被驱动的情况下保持其价值。

•无:不应用驱动程序。

注意:或者,可以通过单击的“拉动类型”列来设置拉动类型约束I/O端口窗口。

•术语内类型:(仅限7个串联设备)定义输入的并联端接特性信号有关更多信息,请参阅《7系列FPGA SelectIO资源用户指南》(UG471)。

•ODT:(仅限于基于UltraScale体系结构的设备)定义片上的价值标准的DCI和非DCI版本的输入端终止(ODT)支持。有关更多信息,请参阅UltraScale体系结构SelectIO资源用户指南(UG571)。

•已修复:表示逻辑端口由用户分配。端口必须固定,以确保比特流在没有错误的情况下生成。在“配置端口”对话框中,“固定”选项为只读。要修复端口,请选择端口在“I/O端口”窗口中,右键单击,然后选择“修复端口”,或者输入以下Tcl命令在Tcl控制台中:

设置I/O端口方向

要设置I/O端口方向,请使用以下任意方法:

•仅适用于I/O规划项目:

○ 在“I/O端口”窗口的“方向”列中,单击端口并更改方向使用下拉菜单。

○ 单击I/O端口窗口中的端口,然后在I/O端口属性中更改方向窗

○ 在I/O端口窗口中选择要配置的I/O端口、总线或接口,右键单击,然后选择Set Direction。

•仅针对RTL项目,定义RTL源中的端口方向。

重要!只能在I/O规划项目中设置端口方向特性。如果您尝试在I/O规划项目之外修改此属性,则会发出严重警告。

创建I/O端口接口

要将多个端口或总线分组在一起,可以创建一个接口。这有助于固定通过将所有接口端口视为一组来进行分配。指定所有接点同时有助于压缩和隔离用于时钟区域或PCB布线的接口。这也是使得更容易可视化和管理与特定逻辑接口相关联的信号。要创建接口,请执行以下操作:

1.在I/O端口窗口中,选择要组合在一起的信号。

2.右键单击,然后选择“创建I/O端口接口”。

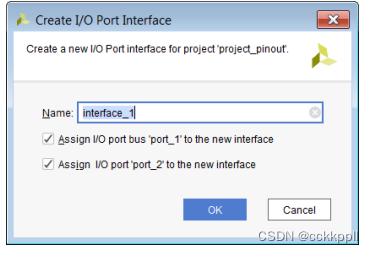

3.在“创建I/O端口接口”对话框(请参见下图)中,输入界面,调整分配选择,然后单击“确定”。

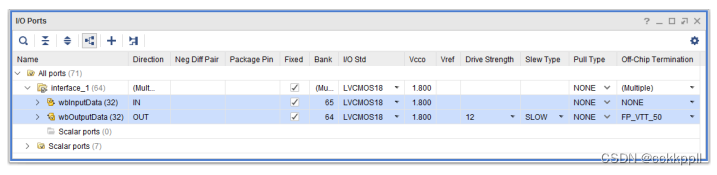

接口在I/O端口窗口中显示为可扩展文件夹,如中所示如下图所示。

向接口添加I/O端口

要将I/O端口添加到接口,请在I/O端口窗口中执行以下任一操作:

•选择I/O端口,并将它们拖到接口文件夹中。

•右键单击端口或总线,然后选择“分配给接口”。在“选择I/O端口接口”对话框中框中,选择目标界面。

从接口中删除I/O端口

要删除I/O端口,请在I/O端口窗口中右键单击端口,然后选择取消分配界面使用I/O端口接口的Tcl命令示例

•创建I/O端口接口:

自动推断I/O端口接口

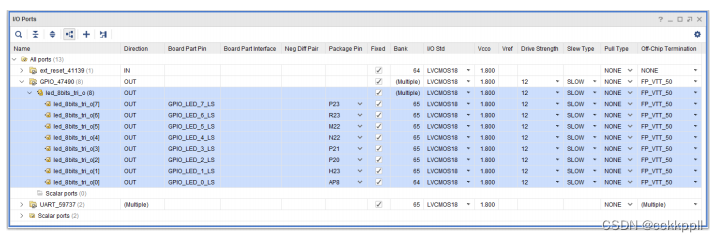

建议:如果您的项目针对的是平台板而不是零件,AMD建议使用Vivado Design Suite平台板流来配置和应用板引出线约束,使用“自定义IP”对话框中的“板”选项卡,或Vivado IP集成程序中的板窗口。了解更多有关平台板流程的信息,请参阅《Vivado Design Suite用户指南:系统级》中的此链接设计条目(UG895)。您可以查看从IP连接到设计的顶级端口的接口。对于这些IP接口,Vivado工具会自动推断出分组的引脚规划接口相关的顶级I/O端口。这提供了一种符号化的方式来引用中的接口顶层设计的背景。例如,在下图中,led_8bits_tri_o总线是根据GPIO_9847引脚规划分组的通用I/O(GPIO)接口界面

您可以从中的“板部件引脚”列查看与I/O端口关联的板部件引脚I/O端口窗口。在下图中,与引脚规划接口关联的端口GPIO_9847被限制到板部件引脚led_8bits_tri_o[7:0]。

注:GPIO_9847中的数字9847用于GPIO接口的唯一标识在设计中有多个GPIO接口。这个数字没有具体的含义。

使用平台板流的Tcl命令示例

•获取板部件接口:

禁止I/O引脚和I/O组

I/O规划视图布局提供了一个接口,可以选择性地禁止端口放置到单个I/O引脚、I/O引脚组或I/O组。可以在中选择和禁止接点设备、封装和封装引脚窗口。要禁止I/O引脚或I/O组:

1.在设备、封装或封装引脚窗口中选择I/O引脚或I/O组。

2.右键单击,然后选择“设置禁止”。

禁止使用的引脚表示为:

•设备窗口和包装窗口中的斜线圆圈(见下图)

•检查Package Pins窗口的Prohibit列中的标记