21 基于端口名称的实例化

题目描述

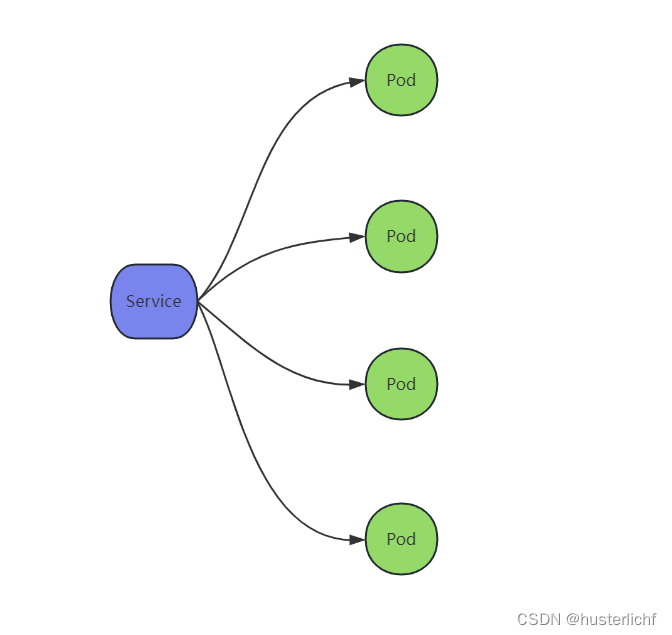

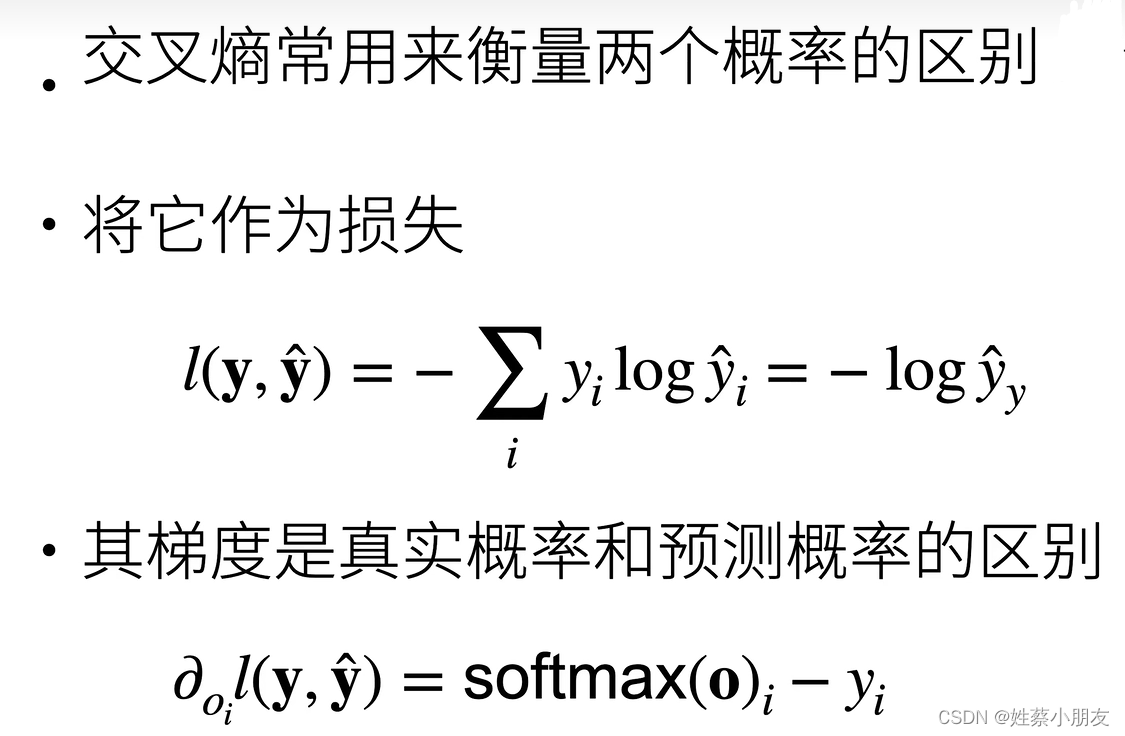

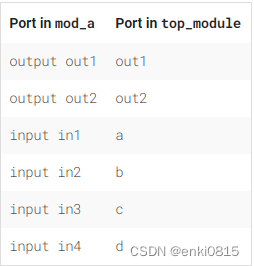

创建一 verilog 电路,实现对模块 mod_a 基于端口名称的实例化,如下图所示:

其中mod_a模块的代码为:

module mod_a (

output out1,

output out2,

input in1,

input in2,

input in3,

input in4

);

assign out1 = in1 & in2 & in3 & in4; //这只是一个简单的示例

assign out2 = in1 | in2 | in3 | in4; //这只是一个简单的示例

endmodule

输入格式

输入信号 a, b, c, d,位宽 1bit。

输出格式

输出信号 out1, out2,位宽 1bit。

module mod_a (

output out1 ,

output out2 ,

input in1 ,

input in2 ,

input in3 ,

input in4

);

assign out1 = in1 & in2 & in3 & in4; //这只是一个简单的示例

assign out2 = in1 | in2 | in3 | in4; //这只是一个简单的示例

endmodule

module top_module (

input a ,

input b ,

input c ,

input d ,

output out1,

output out2

);

mod_a inst_name(

.out1 (out1),

.out2 (out2),

.in1 (a),

.in2 (b),

.in3 (c),

.in4 (d)

);

endmodule22 多个模块的例化

题目描述

对于给定模块my_dff,包含两个输入信号和一个输出信号(D触发器模块),其代码如下:

module my_dff(input clk,input d,output reg q);

always@(posedge clk)

q <= d;

endmodule

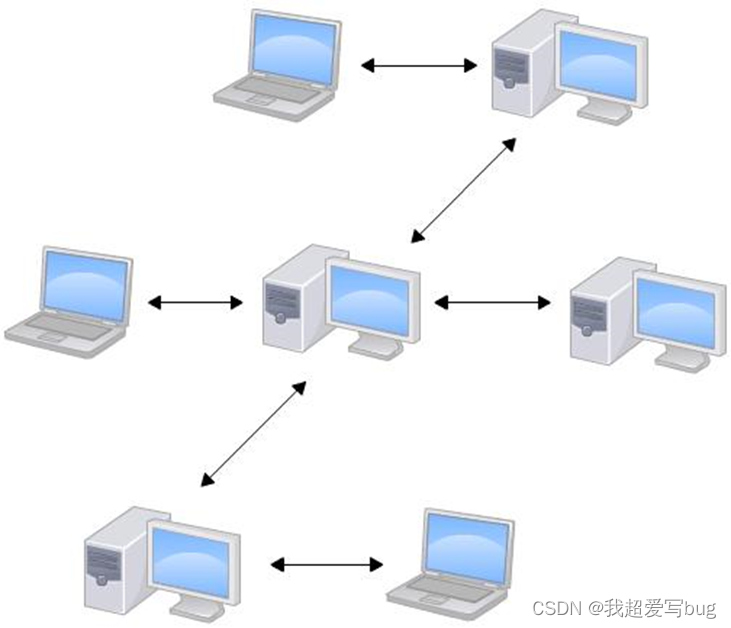

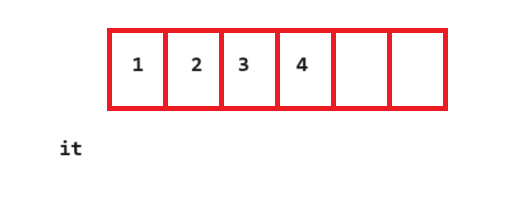

请创建一verilog模块,在该模块中将my_dff模块例化3次,并串行连接,使其构成一个长度为3的移位寄存器,其中3个模块公用一个clk信号,如下图所示:

为实现电路功能,用户需要在顶层模块定义一些内部信号,从而能够将3个例化的模块进行连接。

输入格式

2个 1bit 位宽信号 clk、d

输出格式

1个 1bit 位宽信号 q

module my_dff(input clk,input d,output reg q);

always@(posedge clk)

q <= d;

endmodule

module top_module ( input clk, input d, output q);

wire out1,out2;

my_dff inst1(.clk(clk),.d(d),.q(out1));

my_dff inst2(.clk(clk),.d(out1),.q(out2));

my_dff inst3(.clk(clk),.d(out2),.q(q));

endmodule23 模块与向量信号

题目描述

对于给定模块 my_dff8,其代码如下所示:

module my_dff8(

input clk,

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk)

q <= d;

endmodule

试创建一 Verilog 模块,对 my_dff8 模块例化 3 次,并串行连接,构成一个 8bit 位宽长度为 3 的移位寄存器,同时可以通过选择信号选择输出结果,如下图所示:

输入格式

8bit 的任意有效输入

输出格式

根据 sel 信号,选择一个模块或者原输入作为输出信号

注意:创建一个4选1多路复用选择器(没有提供),它根据sel[1:0]选择输出什么:在输入d处的值,在第一个D触发器之后、第二个D触发器之后或第三个D触发器之后。(本质上,sel选择多少周期来延迟输入,从0到3个时钟周期。

module my_dff8(

input clk,

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk)

q <= d;

endmodule

module top_module(

input clk,

input [7:0] d,

input [1:0] sel,

output reg [7:0] q

);

// Write your code here

wire[7:0] out1,out2,out3;

my_dff8 inst1(.clk(clk),.d(d),.q(out1));

my_dff8 inst2(.clk(clk),.d(out1),.q(out2));

my_dff8 inst3(.clk(clk),.d(out2),.q(out3));

always @(*)

case(sel)

2'h0: q=d;

2'h1: q=out1;

2'h2: q=out2;

2'h3: q=out3;

endcase

endmodule24 加法器

题目描述

对于给定的16bit加法器电路,其代码如下:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

assign {cout,sum} = a + b + cin;

endmodule

试创建一verilog模块,在该模块中实例化两个16bit的加法器,并进行适当的连接,最终构成一个32bit的加法器,该加法器输入进位位为0,如下图所示:

输入格式

32'b0 32'b0

输出格式

32'b0

注意:

给定一个执行16位加法的模块add16。实例化两次来创建一个32位加法器。一个add16模块计算加法结果的低16位,在接收到第一个加法器的执行之后,第二个add16模块计算结果的高16位。设计的32位加法器不需要处理低位的进位(假设为0)或向高位的进位(忽略),但是内部模块需要正确连接才能正确地工作。(换句话说,add16模块执行16位a + b + cin,而设计的模块执行32位a + b)。

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

assign {cout,sum} = a + b + cin;

endmodule

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire in,out1,out2;

assign in = 0;

wire[15:0] sum1,sum2;

add16 add1(.a(a[15:0]),.b(b[15:0]), .cin(in), .sum(sum1), .cout(out1));

add16 add2(a[31:16], b[31:16], out1, sum2, out2);

assign sum = {sum2, sum1};

endmodule25 多层次例化加法器

题目描述

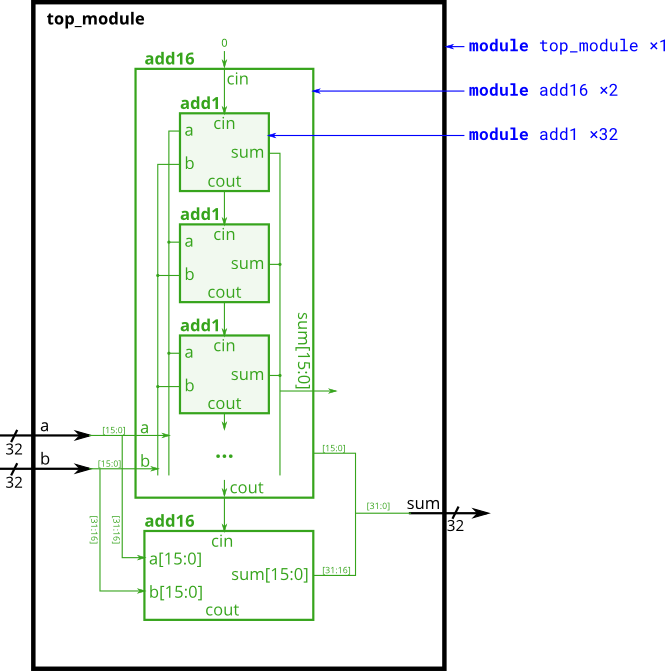

在此练习中,用户需要创建一个包含两层调用的电路,在顶层模块中,实例化两个16bit位宽的加法器add16,而add16模块又是通过例化16个1bit全加器实现的,如下图所示:

在本设计中,一共涉及到3个模块,分别是:顶层模块、add16模块、add1模块,其中add16模块源代码如下:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout);

wire c1,c2,c3,c4,c5,c6,c7,c8,c9,c10,c11,c12,c13,c14,c15;

add1 inst_0(.a(a[0]),.b(b[0]),.cin(cin),.sum(sum[0]),.cout(c1));

add1 inst_1(.a(a[1]),.b(b[1]),.cin(c1),.sum(sum[1]),.cout(c2));

add1 inst_2(.a(a[2]),.b(b[2]),.cin(c2),.sum(sum[2]),.cout(c3));

add1 inst_3(.a(a[3]),.b(b[3]),.cin(c3),.sum(sum[3]),.cout(c4));

add1 inst_4(.a(a[4]),.b(b[4]),.cin(c4),.sum(sum[4]),.cout(c5));

add1 inst_5(.a(a[5]),.b(b[5]),.cin(c5),.sum(sum[5]),.cout(c6));

add1 inst_6(.a(a[6]),.b(b[6]),.cin(c6),.sum(sum[6]),.cout(c7));

add1 inst_7(.a(a[7]),.b(b[7]),.cin(c7),.sum(sum[7]),.cout(c8));

add1 inst_8(.a(a[8]),.b(b[8]),.cin(c8),.sum(sum[8]),.cout(c9));

add1 inst_9(.a(a[9]),.b(b[9]),.cin(c9),.sum(sum[9]),.cout(c10));

add1 inst_10(.a(a[10]),.b(b[10]),.cin(c10),.sum(sum[10]),.cout(c11));

add1 inst_11(.a(a[11]),.b(b[11]),.cin(c11),.sum(sum[11]),.cout(c12));

add1 inst_12(.a(a[12]),.b(b[12]),.cin(c12),.sum(sum[12]),.cout(c13));

add1 inst_13(.a(a[13]),.b(b[13]),.cin(c13),.sum(sum[13]),.cout(c14));

add1 inst_14(.a(a[14]),.b(b[14]),.cin(c14),.sum(sum[14]),.cout(c15));

add1 inst_15(.a(a[15]),.b(b[15]),.cin(c15),.sum(sum[15]),.cout(cout));

endmodule

现在,你需要完成顶层模块和add1模块的verilog代码。

输入格式

两个32位宽的加数a,b

输出格式

32位宽的和sum

注意:

本次设计共有三个模块:

top_module — 顶层模块包括两个add16模块

add16, provided — 一个16位加法器包括16个一位加法器

add1 — 一个一位全加器模块

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum);

// add code

wire in1,out1,out2;

wire [15:0] sum1,sum2;

assign in1=0;

add16 add1 (a[15:0], b[15:0], in1, sum1[15:0], out1);

add16 add2 (a[31:16], b[31:16], out1, sum2[15:0], out2);

assign sum = {sum2, sum1};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

assign sum = a^b^cin;

assign cout = a&b | a&cin | b&cin;

endmodule