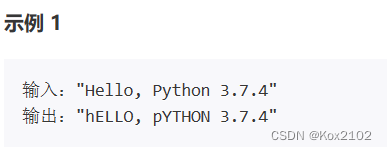

OCC With Capture Enable

有一个OCC具有capture_enable输入,可以与自由运行的慢速时钟一起使用。当OCC指定为启用捕获(capture_trigger:capture_en)时,在输入自由运行的慢时钟上添加时钟门控器,以从自由运行的时钟输入中生成适当的时钟脉冲。该时钟门控器的使能信号是OR门输出,其输入是scan_en和capture_en。这允许分别在移位和捕获周期期间产生slow_clock脉冲。

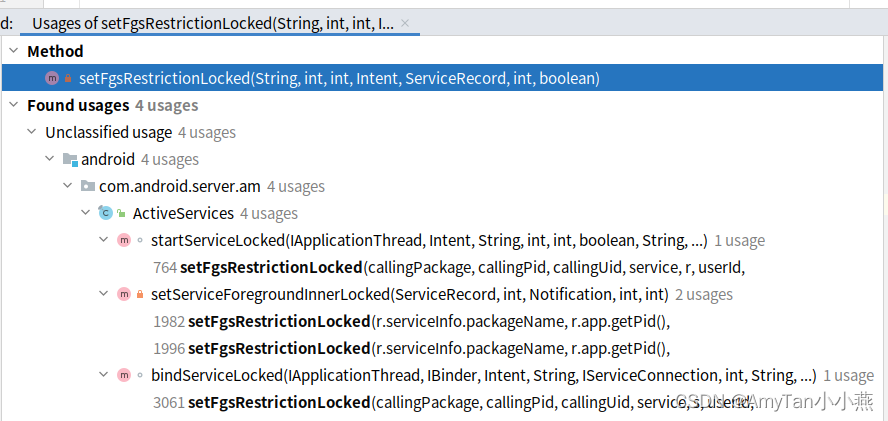

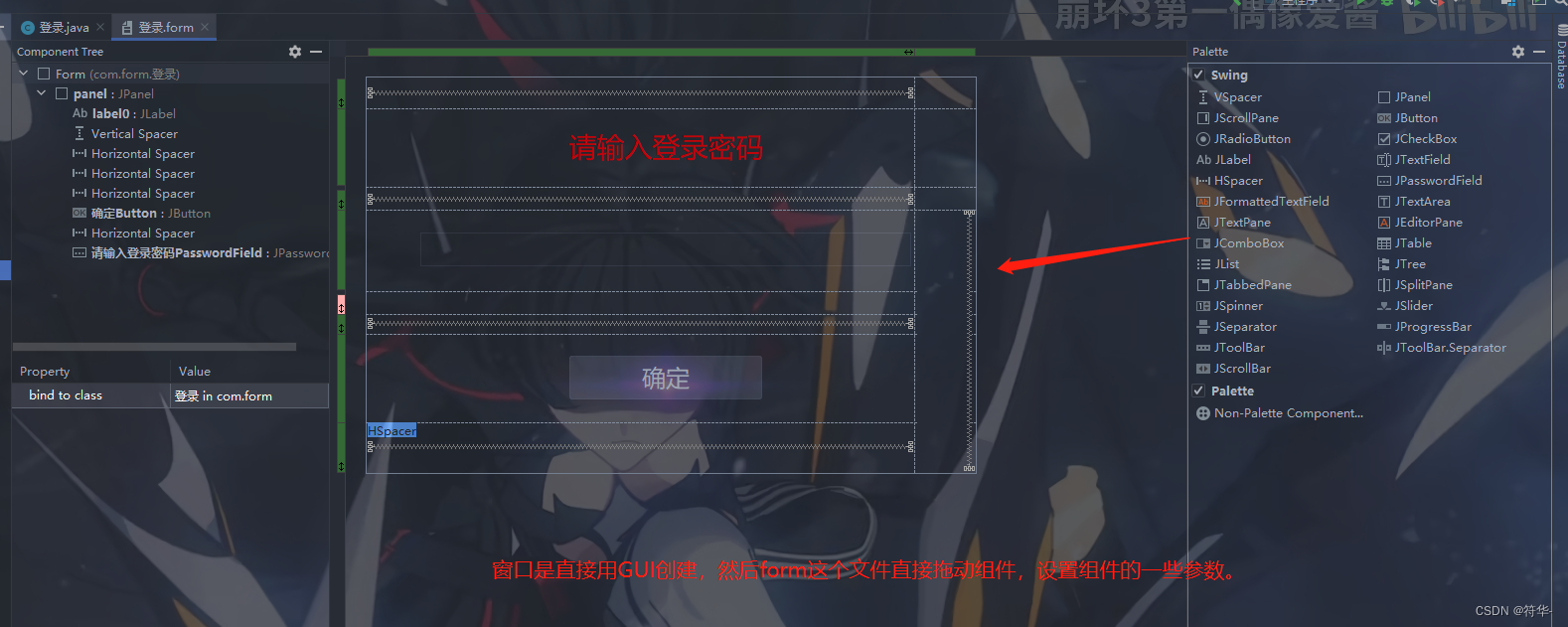

Figure 17-8 shows the OCC schematic with the clock gater at the lower left

此版本的OCC也可与测试仪提供的慢速时钟(非自由运行)一起使用。在这种情况下,新的时钟门控器简单地让受控的慢时钟在移位和捕获期间通过。对于LBIST和LPCT应用程序,需要使用自由运行的慢速时钟的OCC。该自由运行时钟连接到LBIST控制器的shift_clock或LPCT输入时钟。

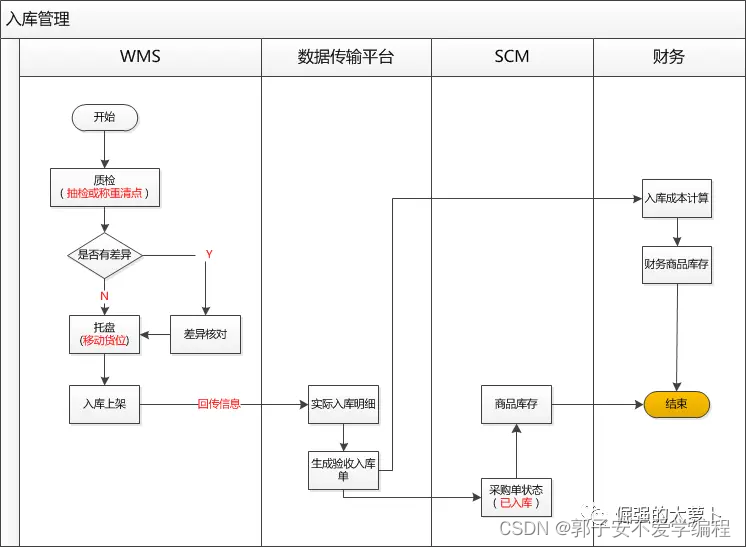

Clock Control Operation Modes

There are four modes as follows.

Functional Mode

在功能模式(test_mode=0)下运行时,启用快速时钟门控器以向设计提供快速时钟。慢速时钟和内部时钟门控器被禁用以降低功率。

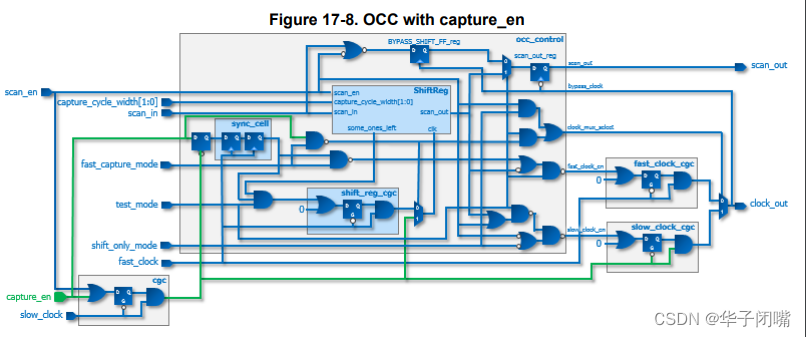

Shift Mode

在shift mode(scan_en=1)中,slow_clock用于加载/卸载包括ShiftReg中的条件位的扫描链。

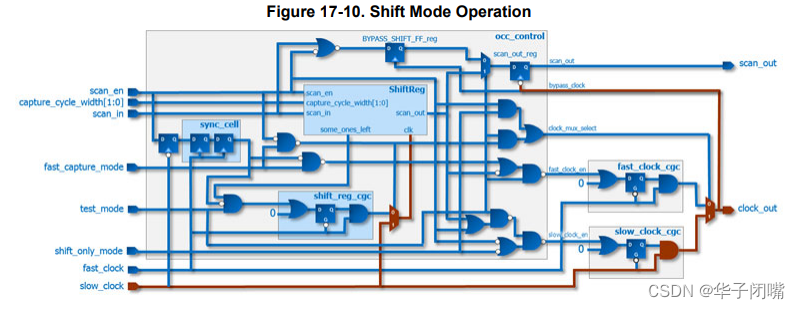

Shift-Only Mode

在shift-only模式下,OCC被禁用(test_mode=0),但换档被启用(scan_en=1)。在此模式下,启用慢时钟门控器以确保慢时钟路径始终用于移位。此外,启用旁路切换。

图17-11显示了非活动(test_mode=0)和活动OCC都使用slow_clock进行移位。默认情况下,标准和父OCC将在scan_en为1时启用移位时钟路径,即使OCC处于非活动状态;这确保了内部和外部模式下的一致shift timing。

要更改默认值并使用功能时钟而不是测试时钟,请将shift_only_mode OCC包wrapper property 设置为off。

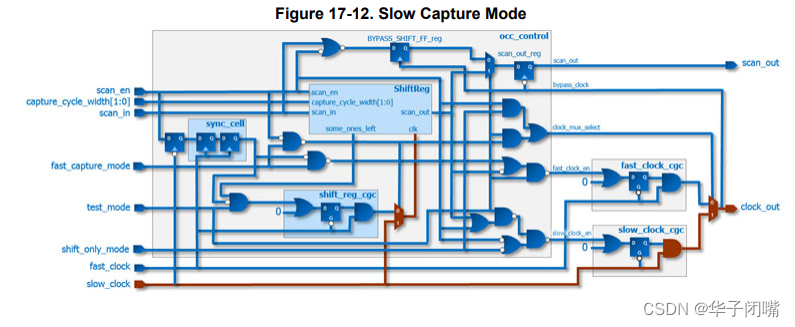

Slow Capture Mode

在慢速捕获模式(fast_capture_mode=0)中,slow_clock用于将数据捕获到扫描单元中,并移动ShiftReg中的条件bit。

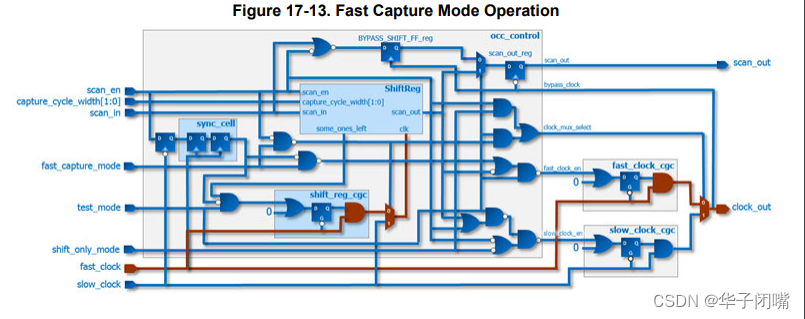

Fast Capture Mode

在快速捕获模式(fast_capture_mode=1)中,fast_clock用于将数据捕获到扫描单元中并移位ShiftReg中的条件位。

Timing Diagrams

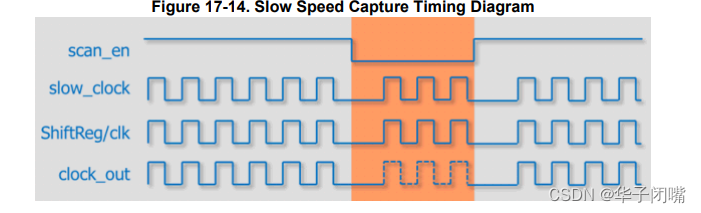

慢速捕获(fast_capture_mode=0)的时序图如下图所示

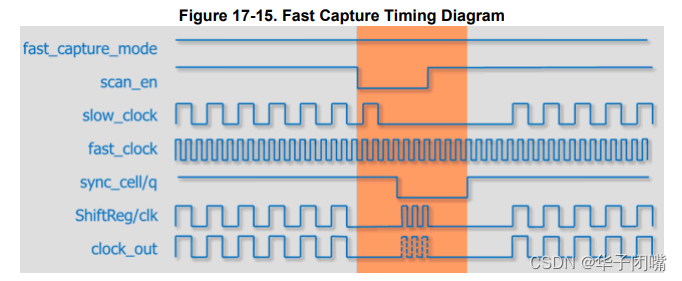

对于本例,capture_cycle_width设置为“10”,导致最大连续深度为3。在此模式下,慢速时钟用于移位和捕获。基于加载到移位寄存器中的条件位,clock_out端口将生成适当数量的慢时钟脉冲。在快速捕获模式(fast_capture_mode=1)下,生成图17-15中的波形。与前面的示例类似,capture_cycle_width在此处设置为“10”,导致最大连续深度为3。在此模式下,slow_clock仍用于移位,但clock_out上的快速捕获脉冲基于fast_clock。

如图所示,已与快速时钟(sync_cell/q)同步的扫描使能信号用于触发ShiftReg/clk上的快速时钟脉冲。ShiftReg/clk信号是包含条件位的移位寄存器的时钟源。根据移位期间加载的条件位,clock_out上将出现正确数量的快速时钟脉冲。

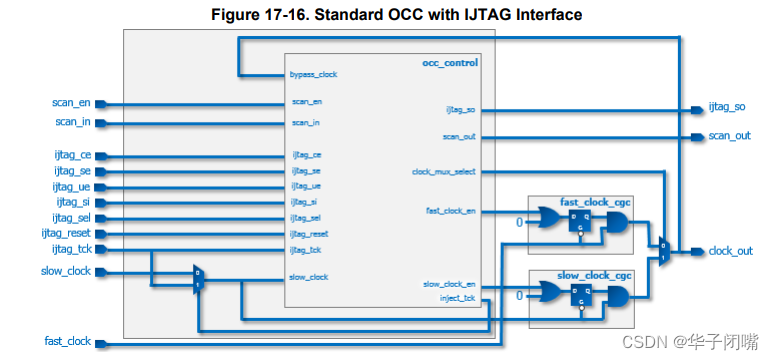

Standard OCC With IJTAG Interface

使用IJTAG接口创建的OCC有一个额外的多路复用器,在没有IJTAG的OCC中不存在。如图17-16所示,当使用ijtag接口创建OCC时(当ijtag_host_interface设置为非none时),将多路复用器添加到slow_clock路径以注入ijtag_tck。

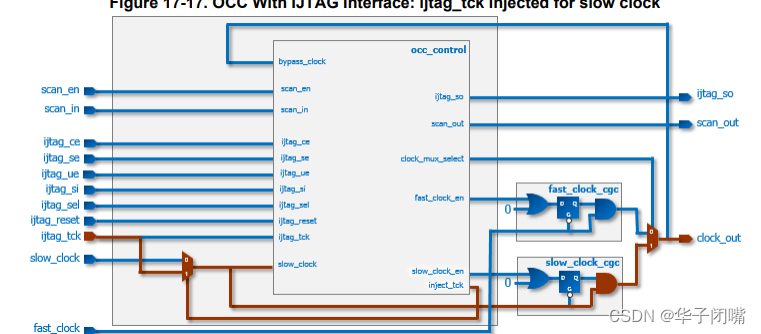

图17-17强调了添加到OCC慢锁输入的多路复用器的功能。当inject_tck为1时,多路复用器选择ijtag_tck,其通过慢时钟门控器和输出多路复用器驱动clock_out。

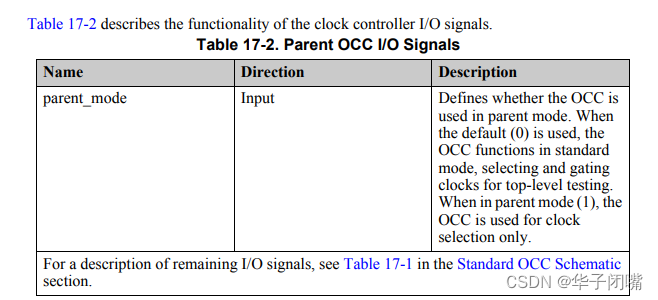

The Parent OCC

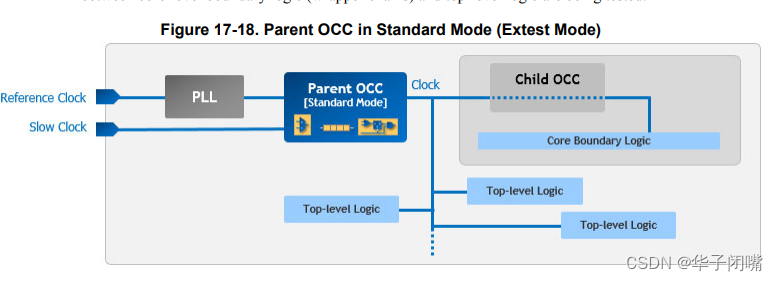

作为三种OCC类型之一,主OCC有两种模式:标准模式和parent模式。在标准模式下,它选择和选通时钟以测试顶级逻辑。在parent模式下,此OCC仅用于时钟选择。标准模式下的主OCC示意图图17-18显示了标准模式下使用的parent OCC。当测试核心级边界逻辑(包装链)和顶层逻辑之间的交互时,该模式的一个典型用途是在Extest模式下进行模式重定目标。

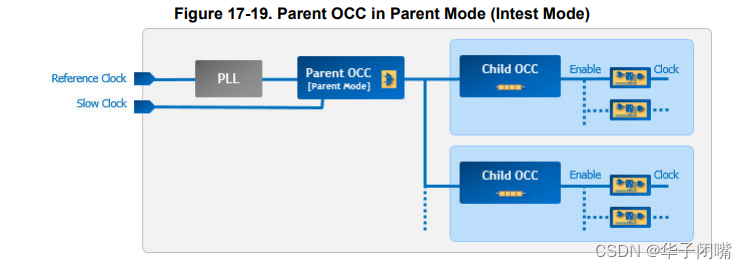

在父模式下,OCC仅用于时钟选择。父OCC通常向子OCC的时钟输入feed clock。图17-19显示了处于父模式的父OCC。此模式的一个示例是在Intest模式下进行模式重定目标。

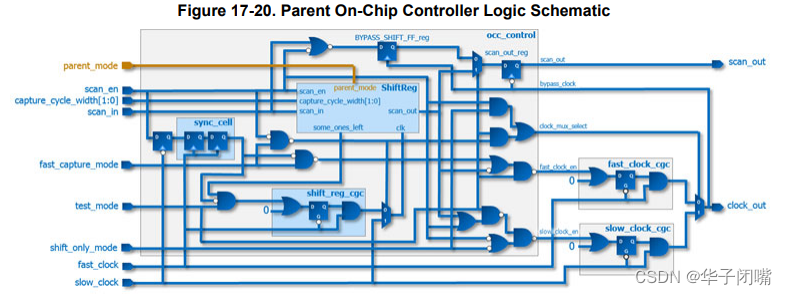

图17-20显示了父片上控制器逻辑。换档时钟不需要到最低级别的子OCC,因为父OCC在换档模式下将换档时钟注入base时钟。当scan_en为低时,它允许一组可编程的恒定时钟脉冲通过。父OCC通常向子OCC的时钟输入反馈时钟,子OCC反过来使基于扫描的测试模式生成工具能够控制哪些时钟脉冲通过或不通过。

所示的示意图表示在没有IJTAG接口的情况下生成的OCC。 标准OCC是推荐用于分层核心的OCC。

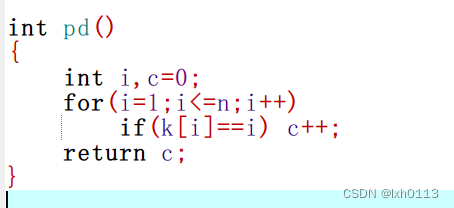

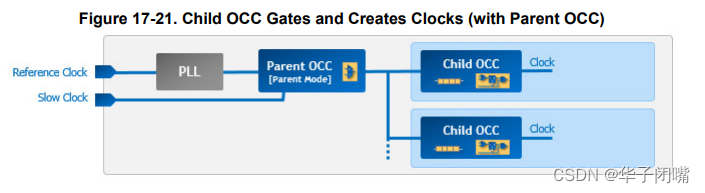

The Child OCC

子OCC是三种OCC类型之一。它执行OCC的chopping control 功能,并可选地选通时钟。默认情况下,子OCC根据加载到扫描可编程移位寄存器中的值创建时钟启用信号。该启用信号用于控制OCC内的(可选)时钟门控器,如图17-21所示。

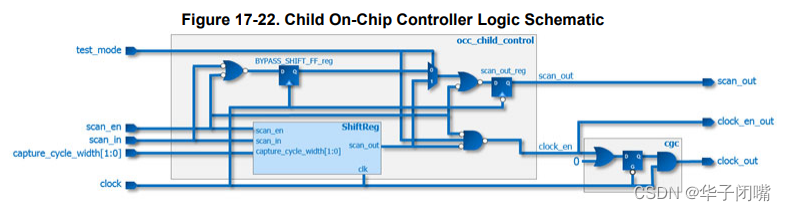

图17-22显示了带有时钟门控器的子芯片控制器的详细示例示意图

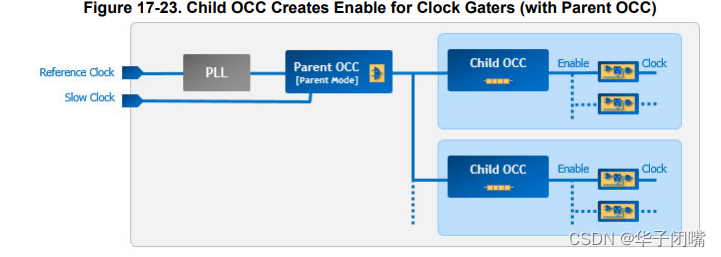

在某些情况下,将子OCC与内部时钟门控器一起使用是不实际的。可选地,可以在没有内部时钟门控器的情况下创建子OCC。创建的信号使布局工具能够复制和控制设计的时钟门控器,以实现诸如时钟网格之类的功能。用户提供的时钟门控单元的处理对用户是透明的。如图17-23所示。

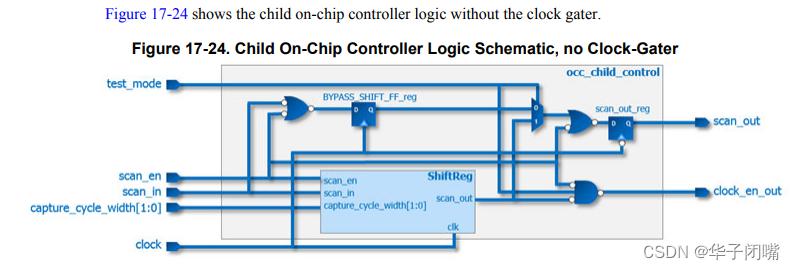

Figure 17-24 shows the child on-chip controller logic without the clock gater

为了在捕获期间正确操作时钟门控器,OCC的时钟启用端口和时钟门控器之间必须存在敏感路径。该工具验证与OCC有结构连接的所有时钟门控器的可控性。如果任何结构连接的时钟门控器没有来自OCC的敏感路径,则必须在捕获期间禁用时钟门控器。在这种情况下,该工具将验证时钟门控器的测试和功能启用是否关闭,或其时钟源是否关闭。所示示意图表示在没有IJTAG接口的情况下生成的OCC。

Tessent OCC Insertion

Tessent Shell用于插入OCC。

使用DftSpecification configuration syntax定义Tessent OCC。OCC Dft规范定义了慢速时钟、扫描启用和静态OCC信号的连接。为了实现压缩ATPG的最佳配置,需要将OCC子链缝合到扫描链中。插入Tessent OCC的基本步骤如下所述。有关在流中插入OCC并将其用于模式生成的更详细示例。

Inserting the OCC

This procedure uses Tessent Shell to insert an instance of the OCC logic for each internal clock. Procedure

1.从Shell提示符调用Tessent Shell。

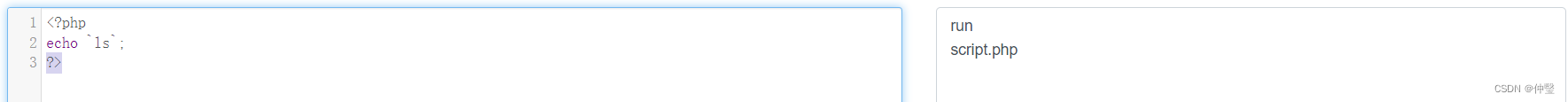

% tessent -shell

2. Set the Tessent Shell context to ‘dft’.#设置到dft

SETUP> set_context dft -no_rtl -design_identifier occ

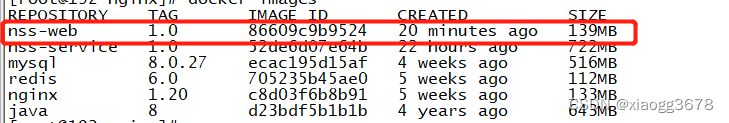

3. Read in the design netlist. For example:w#读网表

SETUP> read_verilog cpu_core.vg.gz

4. Read cell library to allow creation of some instances such as muxes. For example:

#读cell库

SETUP> read_cell_library adk.tcelllib

5. Set the current design. For example:#设置design

SETUP> set_current_design cpu

SETUP> set_design_level sub_block

6. Read the configuration file to specify OCC insertion parameters. For example:

#读取配置文件以指定OCC插入参数

SETUP> read_config_data occ.dft_spec

7.可选地定义端口列表和程序,以插入时钟的片上控制,并在处理DFT规范后将OCC的条件位连接到新的扫描链中。

8.验证并处理DftSpecification包装器中定义的内容。

SETUP> process_dft_specification

9.合成生成的RTL。例如:

SETUP> run_synthesis

此步骤仅适用于将OCC RTL插入门级网表时。当插入RTL设计时,OCC与设计的其余部分一起合成。run_synthesis命令还将更新的网表写入TSDB目录。

10. If needed, optionally write out the updated netlist. For example:

SETUP> set_current_design SETUP> write_design -output_file cpu_core_post_occ_insertion.vg.gz -replace

11. Exit the tool. SETUP> exit