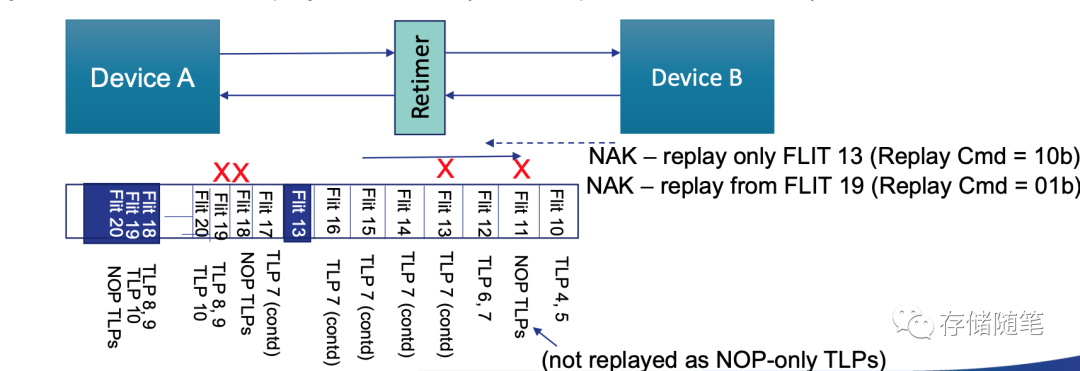

确保TX重试缓冲区的准确性也非常重要,因为在接收到确认或否定信号之前,所有FLIT都需要存储在缓冲区中。由于一个FLIT可能包含多个TLP,或者一个大TLP可以被分割成多个FLIT,因此必须保证重传的FLIT不会跳过或额外添加原始FLIT中的TLP,这对于Posted TLP尤为重要,因为它没有完成通知,丢失的TLP将导致无法纠正的错误。如下图,可以通过Replay Cmd不同的赋值来决定哪些FLIT需要回放。

FLIT通过减少数据Header的复杂性和传输数据overhead,能够帮助降低传输延迟,这对于高性能计算、数据中心和AI应用等领域至关重要。

同时,针对FLIT模式设计了新的完成规则。对于non-posted TLPs的完成机制也进行了重大更新:比如采用14位标签(Tag)来提升跟踪能力,使用OHC-A5区域进行错误报告等。这样改进后的完成机制可以更准确地报告传输过程中的错误情况,并且能够更高效地处理非posted事务,从而降低延迟并提高整体系统性能与可靠性。

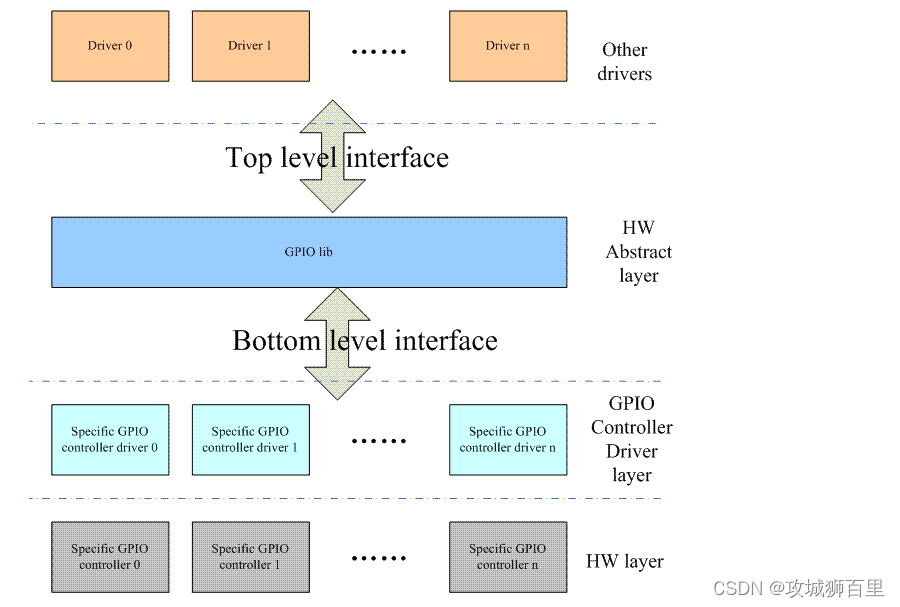

在PCIe总线规范中,标签(Tag)是用来标识和管理并行传输的数据流的机制。随着数据速率和带宽需求的增长,尤其是在PCIe 6.0标准下,对多路复用、低延迟以及高效的数据包处理能力的要求也随之提高。

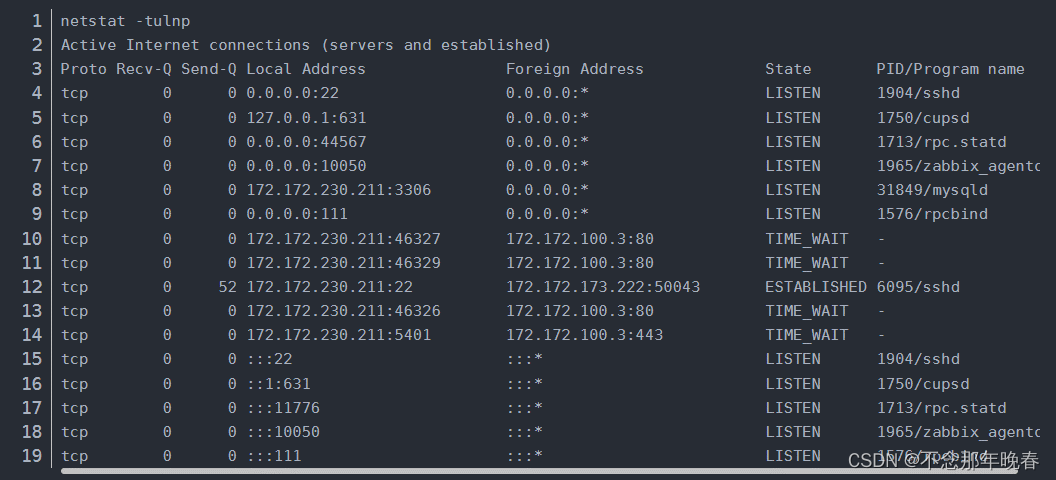

在PCIe 5.0规范中,标签是10位格式,最大支持768个不同的标签,这意味着系统最多可以同时处理768个未完成的事务请求或数据包传输。然而,在更高性能的应用场景,如数据中心、AI计算、高速存储等,这样的标签数量可能不足以满足日益增长的并发事务需求,尤其是在长RTT(Round-Trip Time)环境下,系统的效率可能会因为标签不足而降低。下图是PCIE4.0/5.0/6.0保持高性能而针对Tag标签数量的要求。

PCIe 6.0规范将标签的数量扩展到了14位,从而支持多达15,360个独立标签。这种显著的增加意味着系统能够更好地应对大规模并发任务,增强并行处理能力和整体带宽利用率,即使在链路延迟较高的情况下也能保持高性能和低延迟的数据传输。通过增加标签容量,PCIe 6.0有效地解决了高并发环境下的流量管理和调度问题,提高了数据密集型应用的效率和吞吐量。