案例分析

在一些设计中,某些信号在特定模式下具有恒定值。例如,在功能模式下,测试信号不切换,因此与VDD或VSS相连这取决于它们的活动水平。这也适用于在设计完成后不切换的信号已通电。同样,今天的设计有多种功能模式在某些功能模式中活动的信号在其他模式中可能是不活动的。为了帮助减少分析空间、运行时和内存消耗,让静态正时发动机了解具有恒定值的信号。这对于确保不报告非功能路径和无关路径。使用set_case_analysis命令向正时发动机宣布信号为无效。该命令适用于引脚和/或端口。

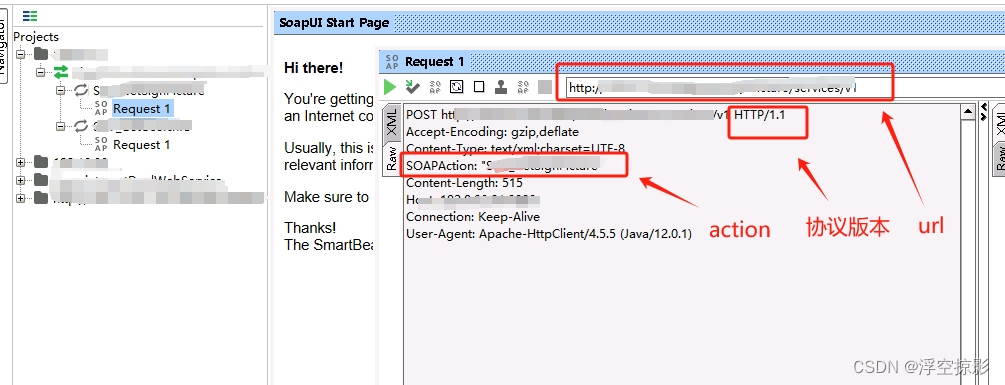

set_case_analysis命令的语法为:

参数<value>可以是以下任意一个:

0、1、零、1、上升、上升、下降或下降

当指定值上升、上升、下降或下降时,这意味着给定的引脚或端口应仅考虑用于具有指定转换的时序分析。另一个转变是残废大小写值可以设置在端口、叶单元的引脚或层次模块的引脚上。

在下面的例子中,在多路复用器clock_sel的输入引脚上创建了两个时钟但在设置上的常数值后,只有clk_2通过输出引脚传播选择引脚S。

在下面的例子中,BUFG_GT有一个动态时钟分频作为其DIV[2:0]引脚,由一些逻辑而不是连接到VCC/GND。

在这种情况下,该工具假设输出时钟可能出现的最坏情况(除以1),并且将输入时钟传播到缓冲器输出。最坏的情况可能是如果从不执行时钟分频1,则悲观和过度约束设计。这是可能的通过设置DIV[2:0]总线来控制BUFG_GT输出引脚上的自动生成时钟具有set_case_analysis约束。例如,如果最坏情况下的时钟分频器为3,则以下情况分析应为应用于BUFG_GT: