目录

一. 中断概念与分类

1.1 中断分类

1.2 中断事件的处理流程

1.3 中断号(IRQ number)

1.4 中断源(Interrupt Source)

1.5 中断触发方式

二. 中断子系统架构

2.1 GIC

2.2 中断子系统架构

2.3 GIC与IP

2.3.1 典型GIC IP

PLC390

GIC 400

GIC 500

REF

一. 中断概念与分类

中断是指 CPU 在执行程序的过程中,出现了某些突发事件急待处理,CPU 必须暂停当前程序的执 行,转去处理突发事件,处理完毕后又返回原程序被中断的位置继续执行。

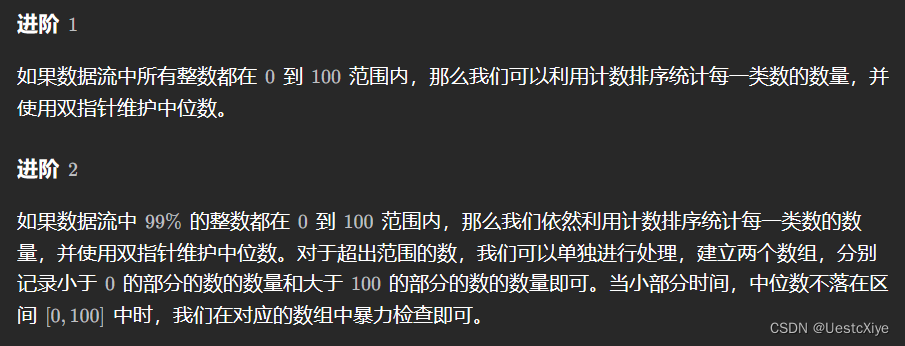

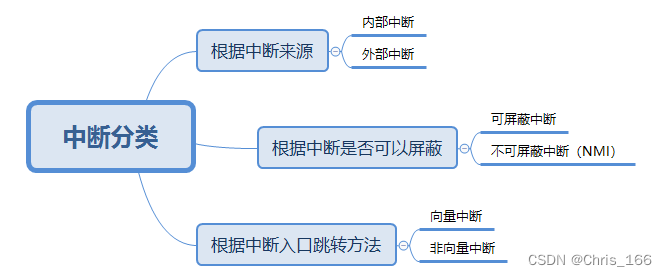

1.1 中断分类

有的地方也把内部中断和外部中断统称为硬中断。

中断处理:中断类型 | 东芝半导体&存储产品中国官网

1. 软中断是执行中断指令产生的,而硬中断是由外设引发的。硬中断的中断号是由中断控制器提供的,软中断的中断号由指令直接指出,无需使用中断控制器。

2. 内部中断的中断源来自 CPU 内部(软件中断指令、溢出、除法错误等,例如,操作系统从用户态切换到内核态需借助 CPU 内部的软件中断),外部中断 的中断源来自 CPU 外部,由外设提出请求。

3. 可屏蔽中断可以通过设置 中断控制器寄存器等方法被屏蔽,屏蔽后,该中断不再得到响应,而不可屏蔽中断不能被屏蔽。

4. 根据中断入口跳转方法的不同,中断可分为向量中断和非向量中断。采用向量中断的 CPU 通常为不同的中断分配不同的中断号,当检测到某中断号的中断到来后,就自动跳转到与该中断号对应的地址执行。不同中断号的中断有不同的入口地址。非向量中断的多个中断共享一个入口地址,进入该入口地址后,再通过软件判断中断标志来识别具体是哪个中断。也就是说,向量中断由硬件提供中断服务程序入口地址,非向量中断由软件提供中断服务程序入口地址。

1.2 中断事件的处理流程

收到中断事件后的处理流程:

1. 抢占当前任务:内核必须暂停正在执行的进程;

2. 执行中断处理函数(ISR):找到对应的中断处理函数,将 CPU 交给它(执行),ISR 位于 Interrupt Vector table,这个 table 位于内存中的固定地址;

3. 中断处理完成之后:第 1 步被抢占的进程恢复执行,在中断处理完成之后,处理器恢复执行被中断的进程(resume the interrupted process)。

1.3 中断号(IRQ number)

1. IRQ number:软中断号,在Linux系统中是唯一的,也是编程的时候需要用到的中断号。

2. HW interrupt ID:也称之为硬件中断号,是中断控制器用来标识外设中断的。

3. IRQ domain:负责实现硬件中断号与软件中断号的映射,通常是由芯片原厂的工程师来映射的,然后他们再将映射后的软中断号告诉我们编程人员。

1.4 中断源(Interrupt Source)

| 中断源类型 | 中断号ID范围 | 用途 |

| SGI (Software Generated Interrupt) 软件触发中断 | 0~15 | 用于多核之间的相互通信,SGI通常在Linux内核中被用作 IPI 中断(inter-processor interrupts),并会送达到系统指定的CPU上。 |

| PPI (Private Peripheral Interrupt) 私有外设中断 | 16~31 | 每个CPU私有的中断,通常会送达到指定的CPU上,应用场景有CPU本地时钟。 |

| SPI (Shared Peripheral Interrupt) 公用外设中断/共享外设中断 | 32~1019 | 此类中段是由外设触发的中断信号,比如按键、手机触摸屏触发的、串口等中断。 |

| LIP (Locality-specific Peripheral Interrupt)基于消息的边沿中断 | 8192 - MAX | GICv3/v4中支持,它们在很多方面与其他类型的中断不同。LPI始终是基于消息的中断,它们的配置保存在表中而不是寄存器。像按键/触摸等这些传统的中断都是需要管脚的,而LPI是基于消息的,直接操作寄存器,就不需要占用管脚了。比如PCIe的MSI/MSI-x中断。 |

1.5 中断触发方式

中断的触发方式可分为边沿触发(上升沿、下降沿)和电平触发(高电平、低电平),两种触发方式的行为有所不同。

| 触发方式 | 特点 |

| 边沿触发 | 在检测到上升沿或下降沿后触发中断,此后中断会一直处于触发状态,直到软件应答该中断为止 |

| 电平触发 | 在检测到特定电平后触发中断,电平变化或软件应答都能deassert该中断 |

二. 中断子系统架构

2.1 GIC

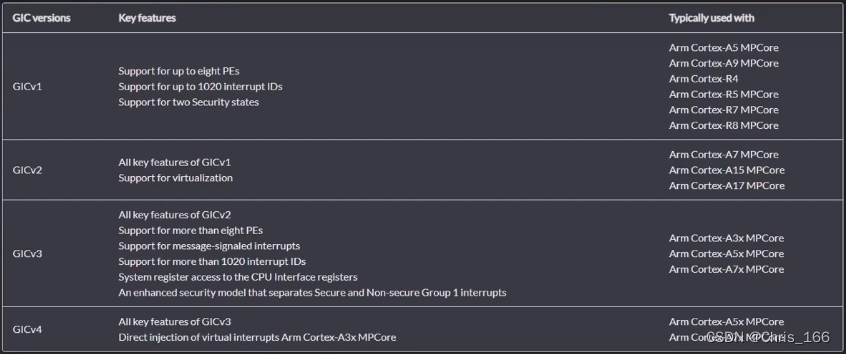

GIC(Generic Interrupt Controller)是ARM公司提供的一个通用的中断控制器,其Architecture Specification目前有V1~V4四个版本,V1很古老了,基本被废弃,V2最多支持8个ARM core,V3/V4支持更多的ARM core。中断控制器就是用来控制中断的,可以通过中断控制器来控制中断的开关和优先级等。

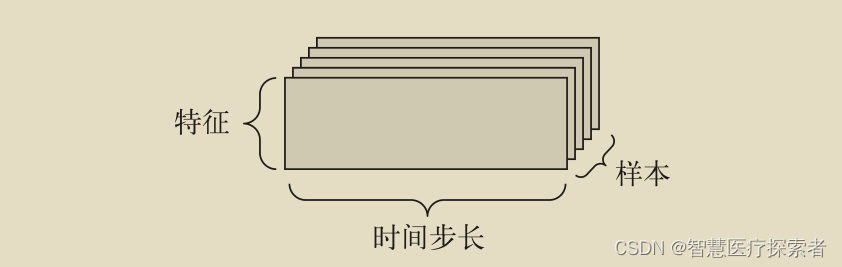

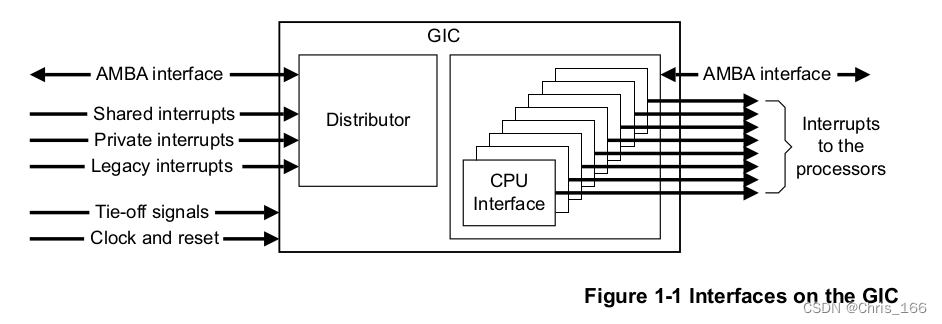

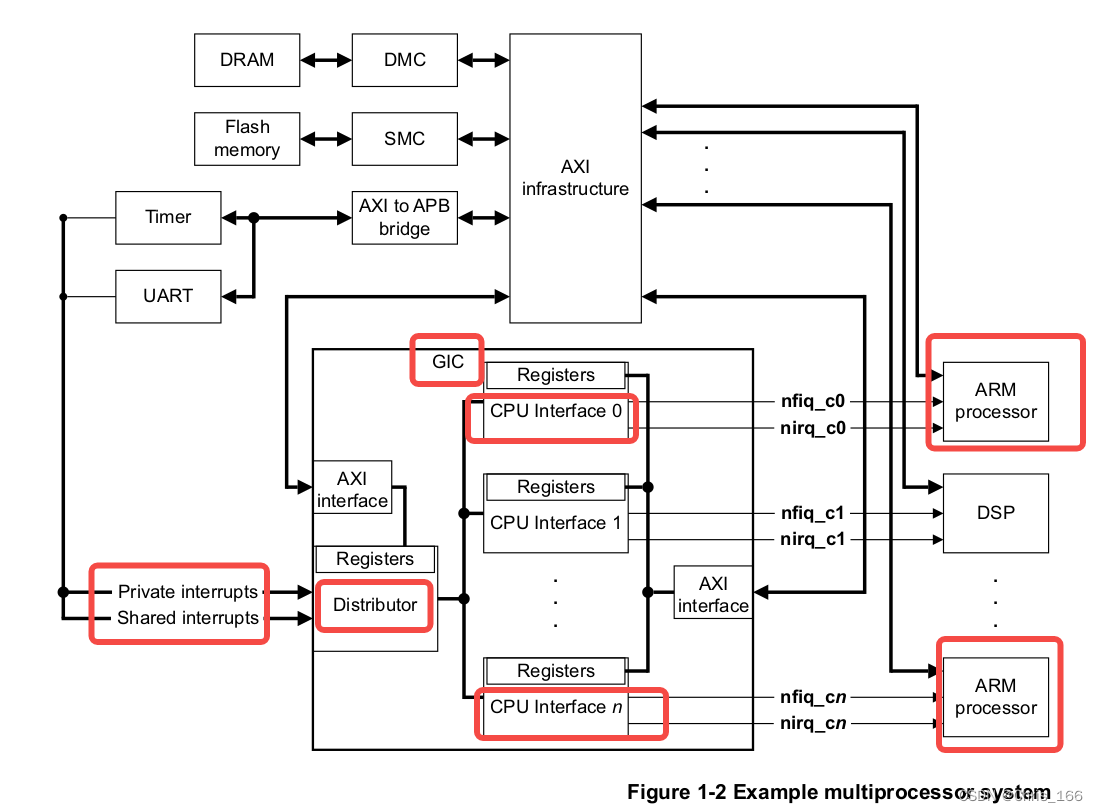

GIC 主要由两部分组成,分别是仲裁单元(Distributor)和CPU接口(Interface)模块。

(1) Distributor 检测各个中断源的状态,使能/屏蔽中断,设置中断优先级,分发各个中断源产生的中断事件分发到指定的一个或者多个 CPU interface 上等。

(2) CPU interface 连接 GIC 和 CPU 处理器。多个CPU interface 就可以连接到多核 CPU 了。

中断控制器是可以级联的,如下图所示。

由后面的 “GIC 400” 小节可知,即使是多核 CPU 也只提供了“4种窗口”,即 IRQ(普通中断模式)、FIQ (快速中断模式)、Virtual IRQ、Virtual FIQ。

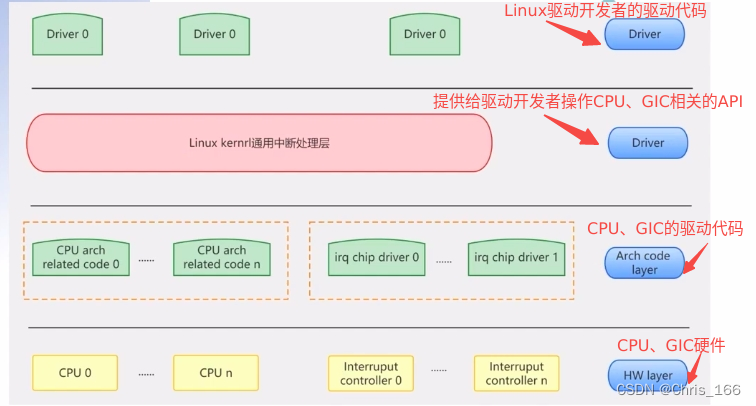

2.2 中断子系统架构

如下为中断子系统的架构图,也大概说明了CPU/GIC与Linux驱动开发者的关系。

2.3 GIC与IP

新的版本都是兼容旧版本的。

SoC(System on Chip) 是一种集成了多个功能组件和外设的芯片,它通常包含一个或多个 CPU 核心,以及其他系统组件,如内存控制器、图形处理器、输入输出接口、中断控制器、外设控制器等。这些组件都集成在同一芯片上,共享同一个物理封装和电源供应。在 ARM 体系结构中,GIC通常与其他外设集成在 SoC 中,用于处理和分发各种中断。

IP(Intellectual Property)也称为 IP 核(Intellectual Property Core),是指芯片中具有独立功能的电路模块的成熟设计。该电路模块设计可以应用在包含该电路模块的其他芯片设计项目中,从而减少设计工作量,缩短设计周期,提高芯片设计的成功率。该电路模块的成熟设计凝聚着设计者的智慧,体现了设计者的知识产权,因此,芯片行业就用 IP 核(Intellectual Property Core)来表示这种电路模块的成熟设计。IP 核也可以理解为芯片设计的中间构件。一般说来,一个复杂的芯片是由芯片设计者自主设计的电路部分和多个外购的 IP 核连接构成的。绝大多数 SOC 厂商都依赖 IP 来设计和生产一款 SOC 芯片,做 SOC 的过程其本质就是寻找,验证及整合 IP 的过程。

在这里可以通俗的理解为 GICv1~v4 都是规范,IP 是对应 GIC 规范实现的一些GIC模块,然后这些 IP 会卖给半导体厂家用来做 SoC。

2.3.1 典型GIC IP

| GIC version | 典型IP |

| GIC-v2 架构 | GIC 400 |

| GIC-v3 架构 | GIC 500 |

| GIC-4 架构 | GIC 600 |

PLC390

整体框图如下

1. 单核PLC390

2. 多核PLC

GIC 400

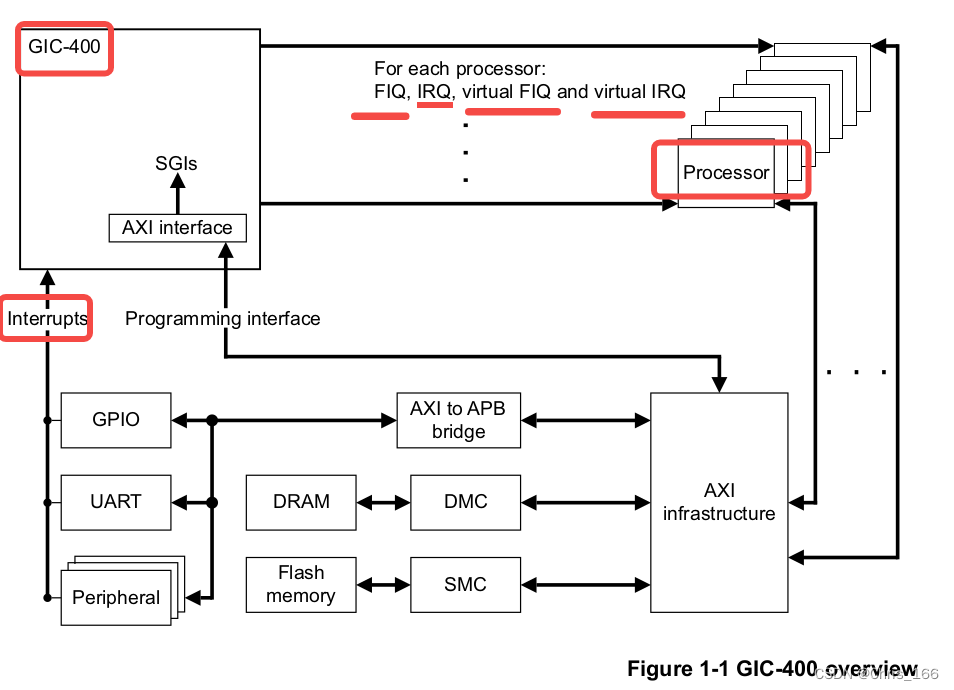

多核 GIC 400

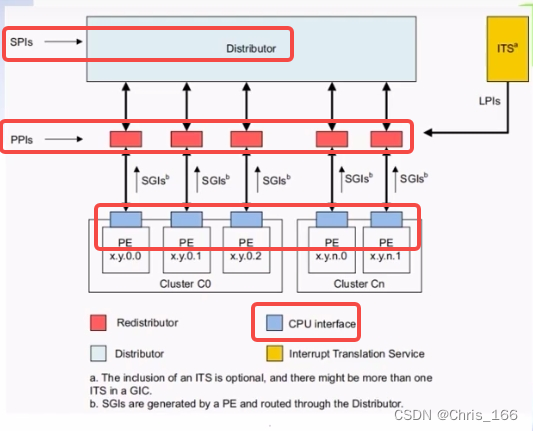

GIC 500

GIC v3 支持了更多核这里的 CPU 直接称为 PE 了,SPI 和 PPI 接在了不同的 Distributor 上。

PE(Processing Element):指处理器系统中的一个实体,代表一个可执行指令的核心或线程。在多核处理器系统中,每个核心被视为一个独立的处理元素。每个处理元素都具有自己的寄存器集、执行单元和控制逻辑,能够独立执行指令和处理数据。

REF

Documentation – Arm Developer

《PrimeCell Generic Interrupt Controller(PL390)》

《CoreLink GIC-400 Generic Interrupt Controller》

《ARM CoreLink GIC-500 Generic Interrupt Controller》

![[Toolschain cpp ros cmakelist python vscode] 记录写每次项目重复的设置和配置 不断更新](https://img-blog.csdnimg.cn/direct/f339114c83bb4e2fb9e0d28f2d1e5add.png)