概述:

计数器是FPGA开发中最常用的电路,列如通讯中记录时钟个数,跑马灯中时间记录,存储器中地址的控制等等。本节给出向上计数器,上下计数器以及双向计数器案例。

内容

1. 向上计数器

2.向下计数器

3.向上向下计数器

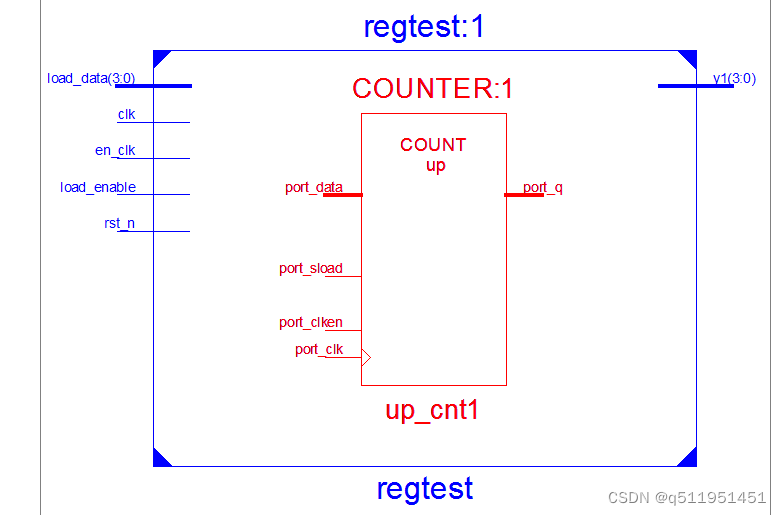

1. 向上计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

output [3:0] y1 // output signal

);

reg [3:0] up_cnt;

assign y1 = up_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

up_cnt <= 0;

else if (en_clk)

if (load_enable)

up_cnt <= load_data;

else

up_cnt <= up_cnt + 1;

endmoduleRTL结构图

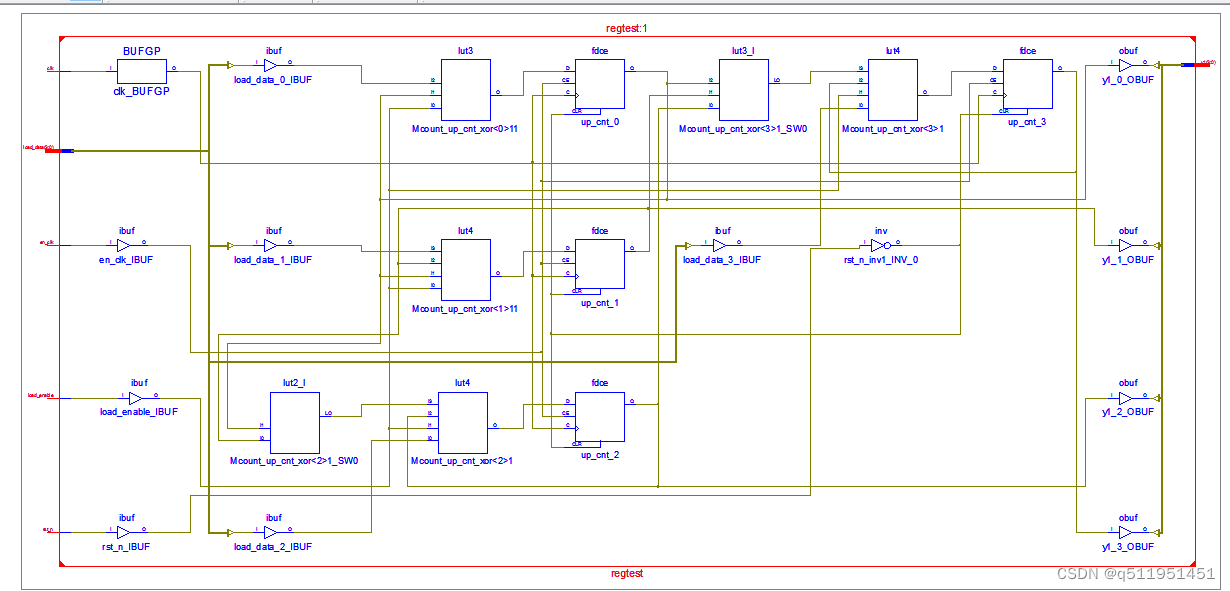

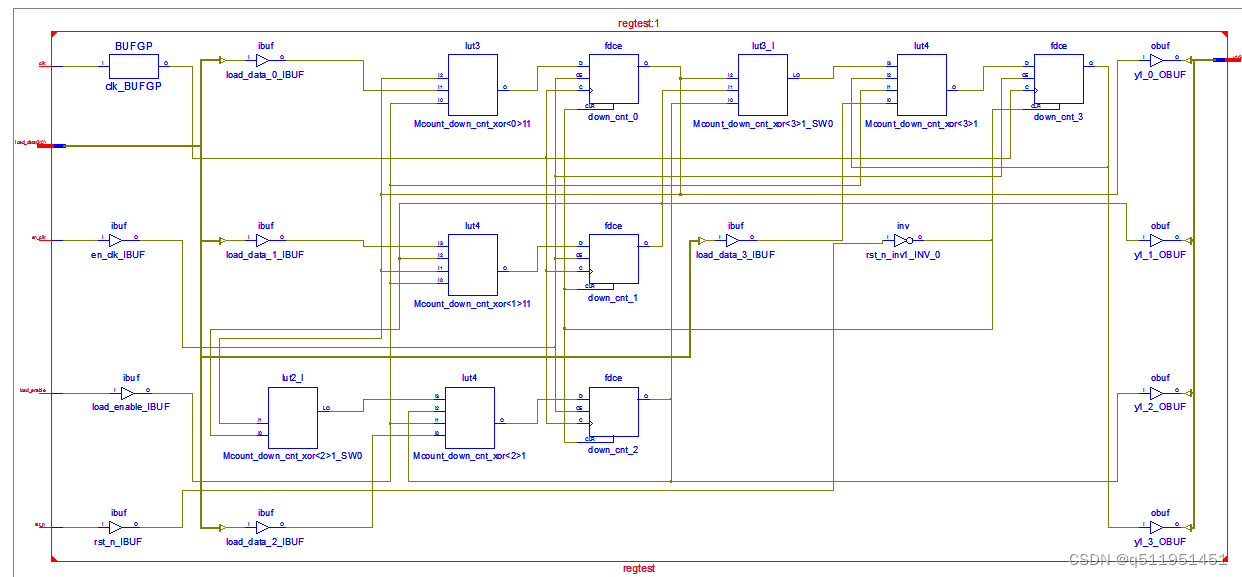

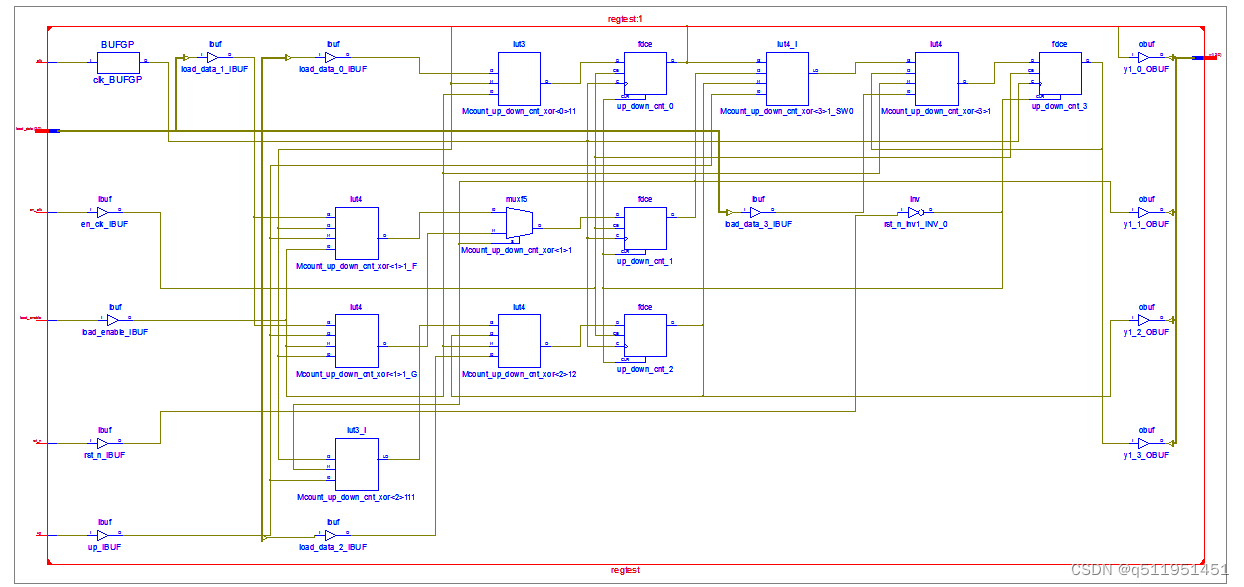

技术原理图,基本的计数器结构是由触发器与组合逻辑来设计的,在FPGA中触发器有fdc来实现,组合逻辑使用lut查找表来实现,

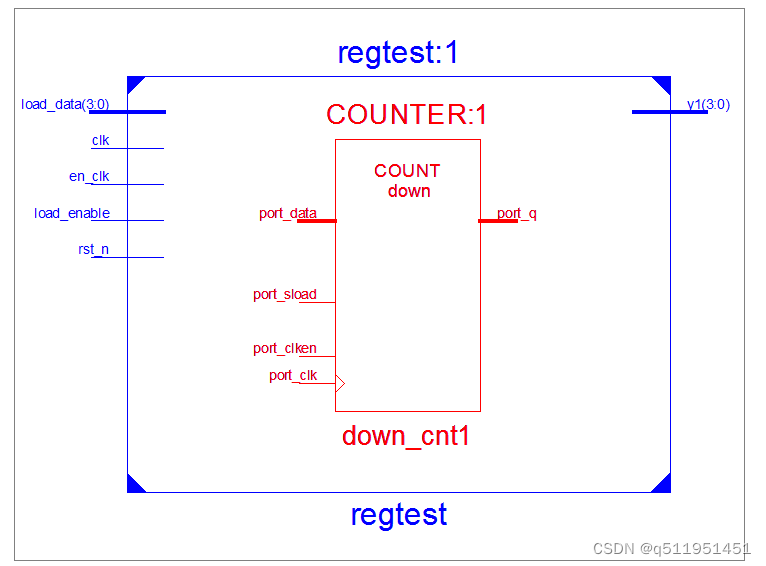

2.向下计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

output [3:0] y1 // output signal

);

reg [3:0] down_cnt;

assign y1 = down_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

down_cnt <= 0;

else if (en_clk)

if (load_enable)

down_cnt <= load_data;

else

down_cnt <=down_cnt- 1;

endmoduleRTL结构图

技术原理图

3.向上向下计数器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input en_clk,

input load_enable,

input [3:0] load_data,

input up,

output [3:0] y1 // output signal

);

reg [3:0] up_down_cnt;

assign y1 = up_down_cnt;

always @(posedge clk or negedge rst_n)

if (rst_n==0)

up_down_cnt <= 0;

else if (en_clk)

if (load_enable)

up_down_cnt <= load_data;

else if (up)

up_down_cnt <=up_down_cnt+ 1;

else

up_down_cnt <=up_down_cnt- 1;

endmodule

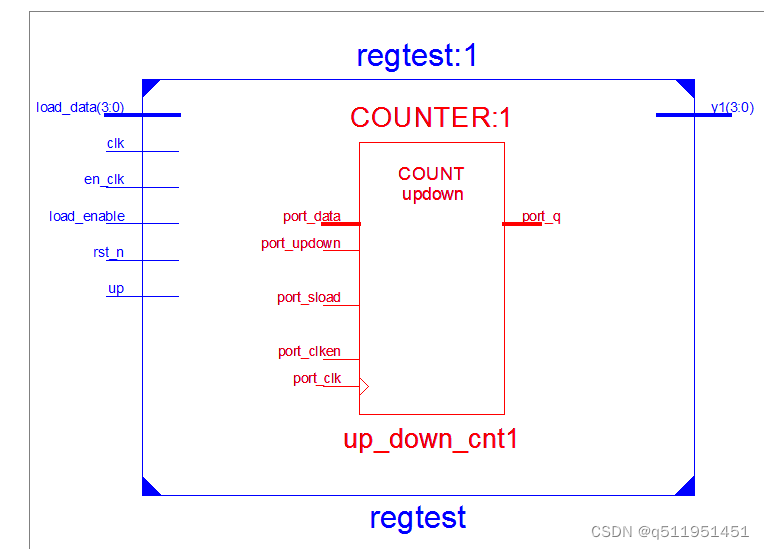

RTL结构图

技术原理图

总结:

计数器是基础,要理解它的设计电路图。

![[足式机器人]Part4 南科大高等机器人控制课 Ch08 Rigid Body Dynamics](https://img-blog.csdnimg.cn/direct/1677268e1f9f4a919827801b77b5c093.png)