*余度(Redundancy):一种确保安全的设计手段,使得出现两个及以上故障时,才会引起既定不希望发生的工作状态。

飞行控制软件主要完成飞行传感器数据处理、飞行姿态控制和余度管理任务,对保证飞机安全性和可靠性起着关键作用,但是现实中与飞行控制软件相关的研发测试过程依旧举步维艰。其主要原因是硬件设备研发成本高且周期长,并且软件程序研发和测试过程严重依赖于实体硬件,同时也缺乏有效的调试手段,无法快速、高效、准确地定位问题,导致软件研发陷入冗长的周期循环中。

当前,国内对飞控系统的测试方法大部分还是采用实物测试、半实物仿真或者虚实结合的方式,这些开发手段虽然能在一定程度上缓和硬件资源受限的窘境,但依旧受限于实体设备,无法进一步提升软件研发和测试效率。因此,本文尝试通过搭建全数字仿真平台来摆脱实体硬件带来的困境。

在全数字仿真平台中,处理器的仿真是重中之重。除了相关寄存器和逻辑操作的仿真外,处理器仿真性能也是一大指标,尤其是在飞控领域,对仿真硬件的实时性控制和性能都有一定的要求。如果处理器仿真性能无法接近真实处理器的效率,那么全数字仿真平台也无法在实际应用中体现价值。而影响处理器仿真性能的最主要的因素则是指令集仿真方式。以往对于指令集仿真一般有2种方式,一种是采用解释执行,将处理器对应的指令集中的每条指令用函数解释对应的功能,执行一条指令就解释一条,该方式能保证指令翻译的正确性,但通常运行速率较慢,面对高性能处理器无法满足仿真性能要求;另一种则是动态二进制翻译,即将机器代码通过转换成中间码后再转换成本地X86的代码,该方式的优点是代码在翻译后执行速度较快,缺点是指令在初次翻译时会有额外的时间开销,效率较低,这往往会影响整体仿真性能。

本文基于SkyEye平台搭建了多余度飞控仿真系统,重点对处理器指令集翻译进行了改良,采用混合模式的方式,即结合解释执行和动态翻译2种方式,结合两者的优点,从整体上提升仿真系统的仿真性能。经过测试,该方案能在全数字仿真平台下运行真实硬件二进制程序,实时性和处理器性能与真实硬件相差无几,满足了实际软件开发、调试和测试的性能需求。

01.多余度飞控仿真系统架构

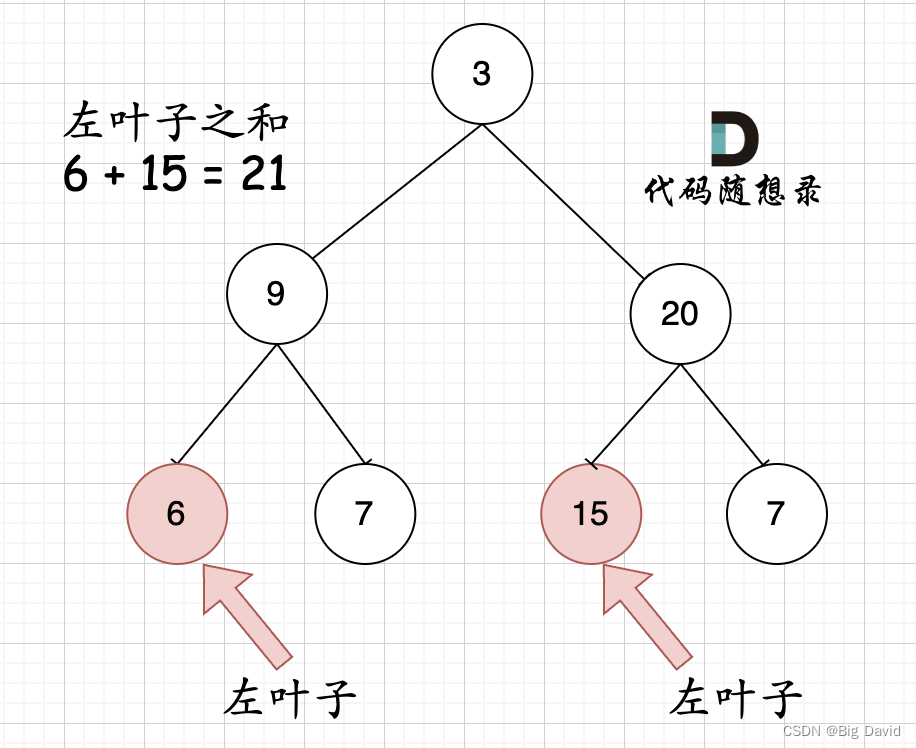

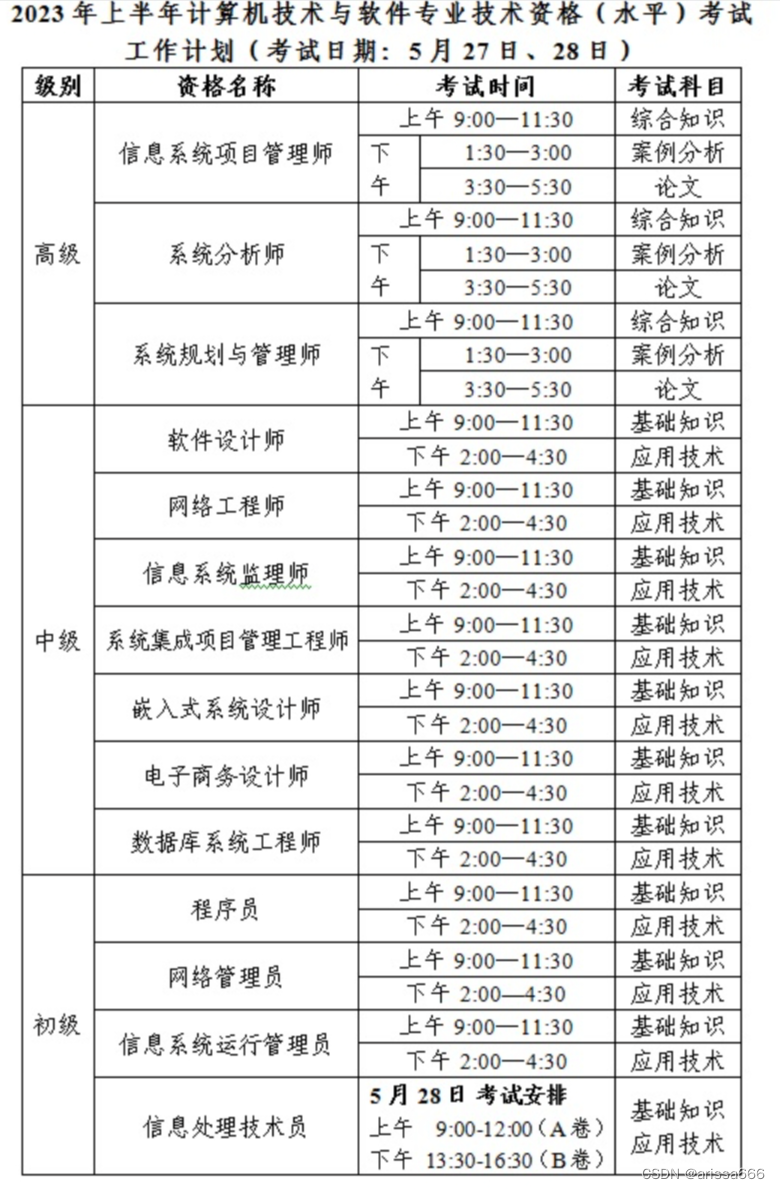

多余度飞控仿真系统架构如图1所示,主要分为四余度飞控计算机(分别以A、B、C、D表示)和数据上位机

每个控制系统以DSP F28335为核心,通过交叉通道数据链路(Cross Channel Data Link,CCDL)和RS422总线来实现余度计算机之间数据通信的功能。为了保证计算节拍一致,用GPIO接口来控制余度计算机时序同步。同时,为了能直观地检查余度计算机状态信息,通过1394总线将各自余度计算机数据发送给数据上位机显示。

▲图1 多余度飞控全数字仿真系统架构图

02.虚拟目标机建模

2.1 处理器建模

处理器模型在工作时主要是完成取指、解码和执行的过程,然后通过内存访问相关地址或者操作各类寄存器以完成程序命令。对于处理器的建模,需要根据真实硬件的结构来分别模拟取指单元、指令分配单元、指令译码单元、通用寄存器、控制寄存器和中断控制逻辑部分。

2.1.1 指令集翻译

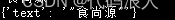

对于指令集翻译,采用混合模式的方式,即结合解释执行和动态二进制翻译的方式,可以在2种执行方法之间进行选择,同时最小化每种方法的缺点。

图2给出了混合模式的基本流程。在混合解释执行和动态二进制翻译的组合中,如果单条指令未被动态翻译过,则先采用解释执行来翻译,这可以使程序快速启动和执行,从而最大限度地减少不必要的延迟。在程序运行时,当单个指令解释执行的次数达到动态翻译命令中所设置的阈值时,往往这时候便意味着处理器要大量重复执行某条指令,而处理器便会由解释执行模式切换到动态翻译模式。通过动态二进制翻译介入,将原本需要解释执行的指令动态转换为目标平台的机器语言指令并予以执行。

▲图2 混合模式执行流程

2.1.2 处理器实时性

在虚拟仿真平台中,保证处理器的实时性是关键因素之一。为了保证处理器与外设模型时序统一,仿真平台采用指令周期作为整个系统统一的时钟周期。通过统计处理器模型执行的指令数,结合处理器的主频即可得到仿真时间。

该时间区别于真实的物理时间,在处理器仿真性能与真实性能一致的状态下,真实时间的1s对应仿真时间的1s。如果处理器仿真性能比真实硬件慢1倍,可理解为真实的2s对应仿真时间的1s。而整个系统运行中有关的定时中断、时间片轮转等涉及时钟的概念都是基于仿真时间而言的,在仿真时间中,处理器和其他仿真设备均处于同一时序中,因此能够满足系统仿真的实时性要求。

2.2 外设建模

在真实DSP芯片中存在各种各样的外设,例如GPIO、Timer、DMA等。一般情况下,只有驱动程序负责与片内外设进行交互,上层应用只能看到一个抽象的接口,驱动程序负责完成与真实硬件的交互。而在仿真领域,只需针对外设的逻辑功能进行建模,无须对电气电路进行模拟。

另外,关于1394总线与上位机的通信,则使用Socket通信方式来模拟。除了实现基本设备寄存器功能和数据收发处理外,还要借助UDP/TCP协议与上位机软件进行数据通信。

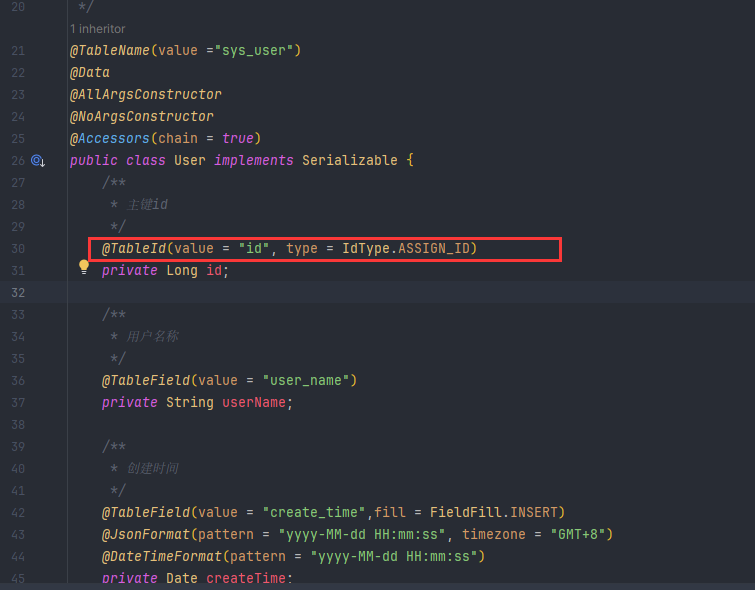

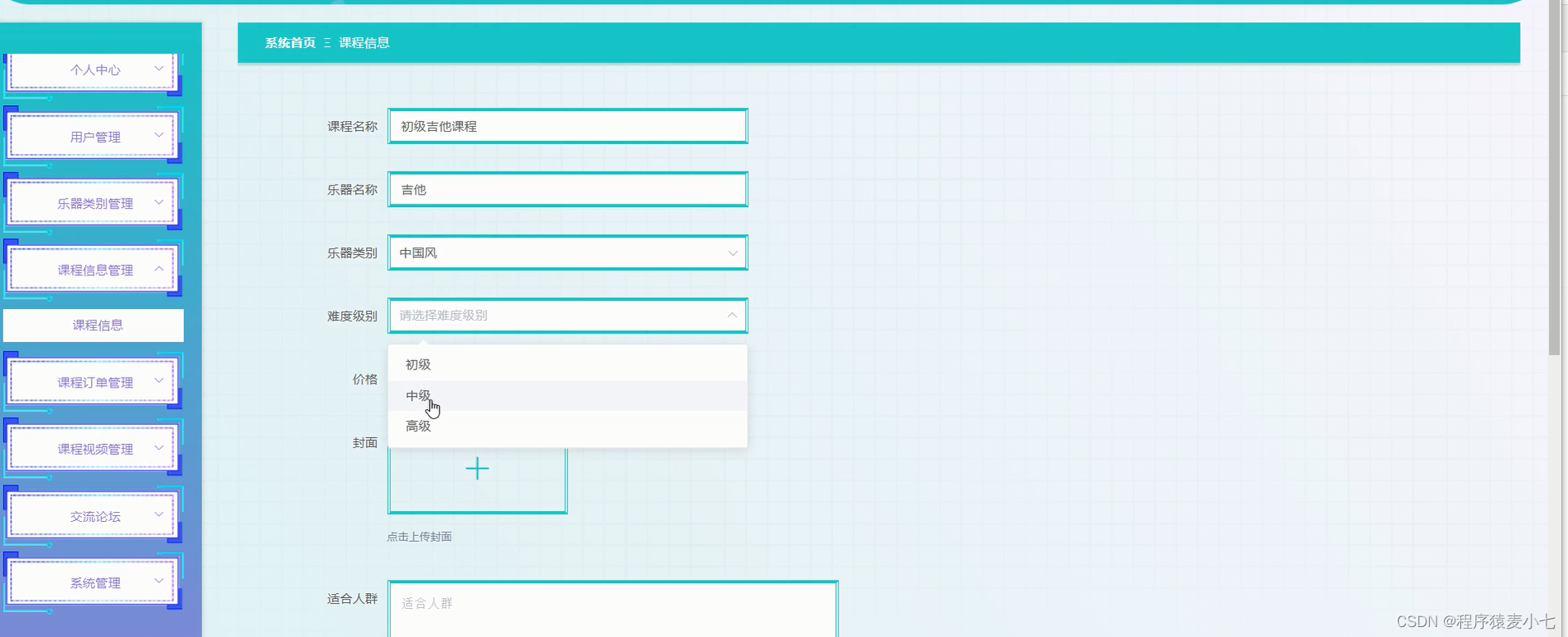

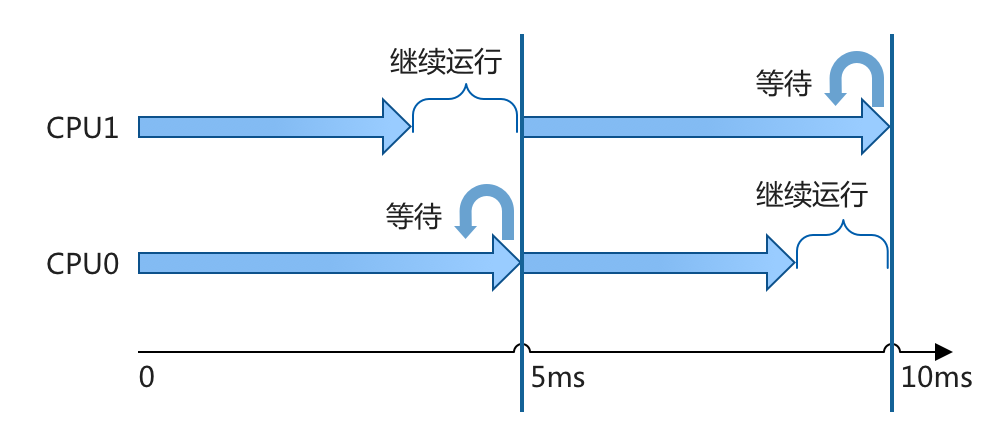

2.3 时间同步

在真实硬件环境下,多板同步依赖于时序信号,但是在数字环境下无法模拟电气信号。为此设计了一套CPU同步机制,基本原理如图3所示。

▲图3 CPU时序同步原理图

设仿真同步时间步长为5ms,CPU0经过虚拟时间的5ms,此时CPU1只运行了虚拟时间的3ms,仿真系统调度器就让CPU0陷入空闲任务等待中直到CPU1运行完剩余的2ms,从而保证2个CPU都经历了虚拟时间的5ms。在第1个仿真步长同步后,让CPU0、CPU1继续运行。同理,假如CPU1运行了虚拟的5ms时间后CPU0只运行了虚拟时间的3ms,则CPU1继续等待直到CPU0运行完剩余的2ms。

03.故障注入

SkyEye模拟的故障注入是针对仿真设备实现的注入故障功能,可以通过改变设备或寄存器中某一位或几位的值来实现注入故障,模拟硬件设备因为某种因素(如收到高电平或者低电平触发)导致的意外故障,以此来检测软件的健壮性。

在多余度飞控仿真平台中,也可以测试模拟余度管理功能。余度管理是指保证余度系统正确协调地工作、监控系统运行并完成故障检测和处理工作的功能的总称。在SkyEye界面中可通过控制单个飞控计算机的暂停、停止和运行来模拟设备的故障损坏、设备下线等异常情况,同时测试验证其余飞控计算机的实际运行表现是否符合预期,其原理图如图4所示。

▲图4 飞控系统故障注入原理图

04.测试验证

4.1 功能性验证

在完成飞控仿真平台后,便可以在该平台上测试和调试飞控程序。测试的主要内容包括飞控系统的驱动控制功能验证、多余度管理功能验证、上位机通信功能验证。

其中,驱动控制功能验证是通过串口输出信息和设备寄存器状态来判断是否符合预期。而多余度管理功能则是搭建逆向测试用例,在保证多板时序同步的情况下,通过故障注入接口来测试验证在飞控计算机异常的情况下能否实现余度管理功能。上位机通信功能用于判断能否接收到1394数据包,并成功解析显示。

搭建集成测试用例,经过大量测试,上述功能均得到验证,仿真效果与真实硬件平台一致。

4.2 处理器性能验证

此仿真系统中使用的F28335处理器的主频设置为150MHz,官方性能参数为150MIPS(Million Instructions Per Second)。经过测试,仿真处理器实际在运行过程中平均性能能够达到150MIPS甚至更高,接近真实硬件情况。

另外,统计解释执行、动态翻译和混合模式3种模式的处理器性能,结果如图5所示。可以发现,解释执行的运行效率稳定但速率最低;动态翻译在前期翻译耗费了较长的时间,但在翻译完成后运行速度较快;而混合模式则能在动态翻译的基础上快速启动,并且程序稳定后运行性能与动态翻译速率相似,符合预期效果,满足了实际使用需求。

▲图5 F28335处理器指令集翻译模式性能对比

4.3 实时性验证

为了校验仿真系统的实时性,程序内部设置定时中断任务,通过SkyEye平台提供的Python脚本接口,统计定时任务开始到任务结束中间仿真时间的消耗,多次采样避免个别异常。定时任务触发时间对比如表1所示,通过对比可知,混合模式下程序定时任务仿真时间与真实时间基本相差无几,验证了周期任务的实时性。

▲表1 定时任务触发时间对比

05.结束语

本案例所设计的多余度飞控全数字仿真系统结合了解释执行和动态翻译的优点,能在保证仿真实时性的同时,提高处理器运行效率,满足日常软件研发的基本要求。该仿真系统在实际应用中可大幅缩短多余度飞控嵌入式软件研发所需时间,同时可保证软件研发的质量。

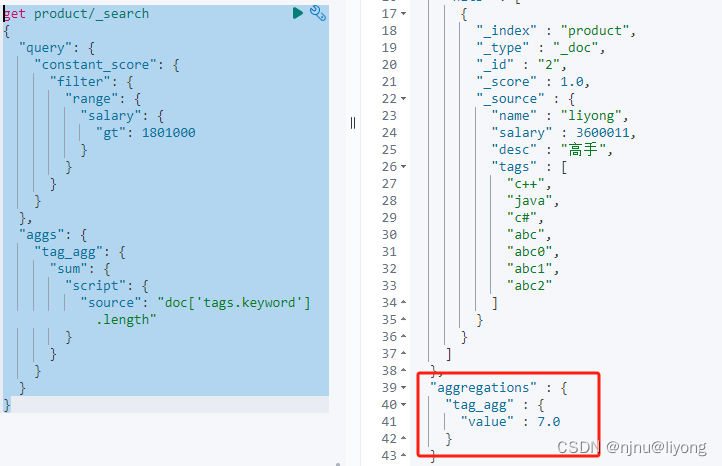

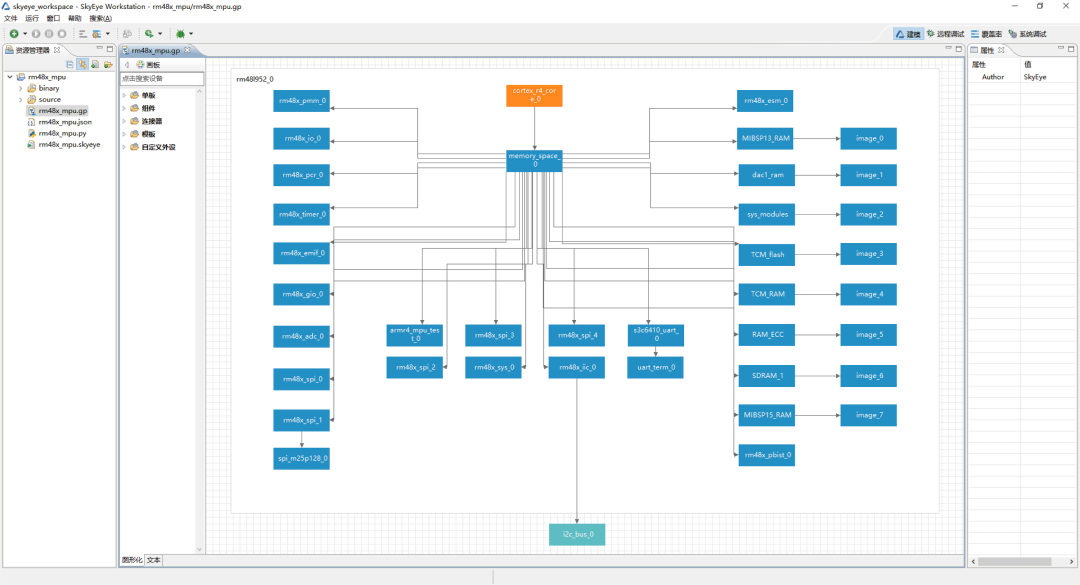

天目全数字实时仿真软件SkyEye是基于可视化建模的硬件行为级仿真平台,支持用户通过拖拽的方式对硬件进行行为级别的仿真和建模。

基于SkyEye搭建的嵌入式系统虚拟化运行环境,工程师可不受物理硬件限制,随时访问目标系统,快速搭建虚拟硬件模型并提前进行开发、测试和验证工作,实现高效率、高质量的软件交付。SkyEye支持主流的嵌入式硬件平台,可运行国内外主流的操作系统,对国产生态的支持尤为出色。通过利用基于LLVM的动态二进制翻译技术,SkyEye可使虚拟处理器在典型的桌面计算机上运行速度达到2000MIPS以上。

SkyEye有效解决了嵌入式软件研发时过分依赖硬件资源的问题,填补了国内嵌入式虚拟仿真领域的空白,为嵌入式软件研发模式带来了革新式的变化。

▲SkyEye界面图:基于可视化图形的硬件建模

参考文献

[1]张琦,康烁,刘永毅,赵立蒙,曾子强.(2023).基于混合模式的多余度飞控全数字仿真系统研究.(eds.)2023年中国航空工业技术装备工程协会年会论文集(pp.110-113).航空工业沈阳飞机设计研究所;浙江迪捷软件科技有限公司;doi:10.26914/c.cnkihy.2023.047223.

![[论文笔记] chatgpt系列 SparseMOE—GPT4的MOE结构](https://img-blog.csdnimg.cn/direct/d340aaa05f8647e89b5604ab3a333816.png)

![[Vulnhub靶机] DC-1](https://img-blog.csdnimg.cn/direct/4f68c8fa81654f699b12466cde86dfd4.png)