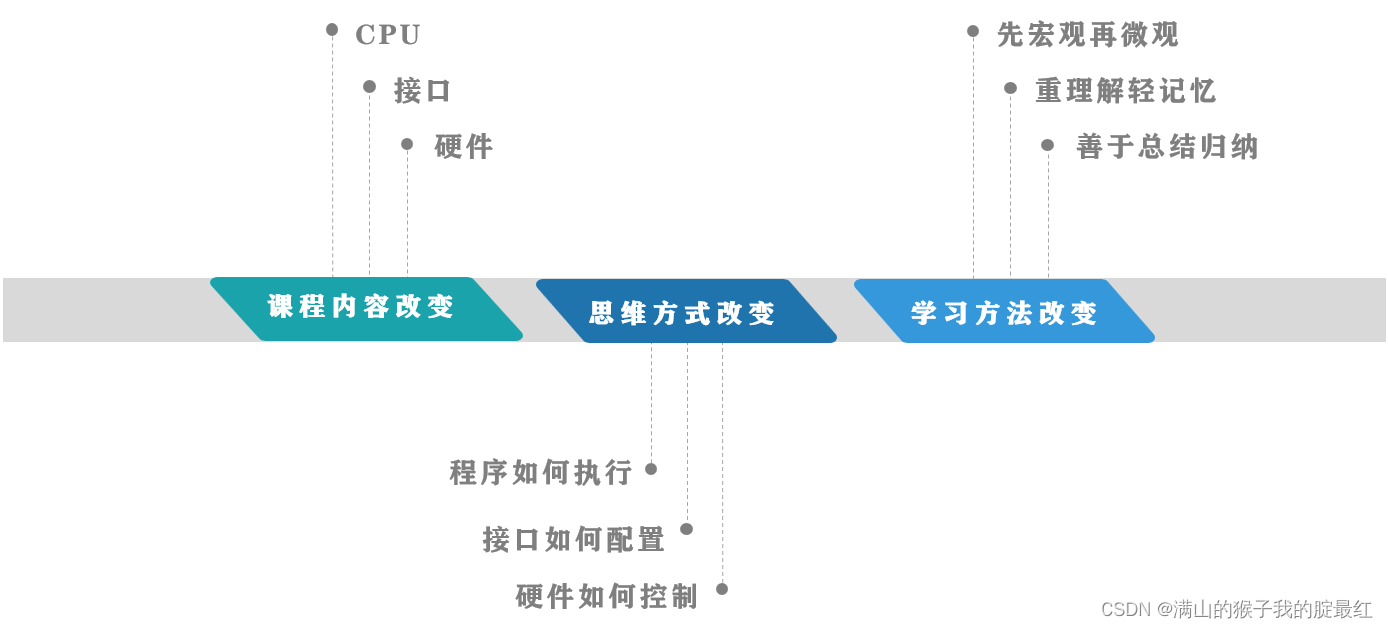

ARM课程介绍

课程特点

ARM开发 --> Linux移植 --> 驱动开发

前后联系:ARM和系统移植为驱动开发学习做准备工作

所需知识:C语言基础及STM32需要的硬件知识

课程要求

目标:学习程序运行原理、硬件的控制原理

会看原理图、芯片手册、学习解决问题的方法(不要死记硬背)

要求:操作过程中一定要大胆动手、大胆操作,有问题及时询问

提醒:耐心、耐心、耐心、多敲、多敲、多敲、多练、多练、多练

课程内容

底层课程导学

Linux层次架构、计算机基础知识、总线、存储结构

ARM体系结构

ARM基础概念、ARM寄存器、工作模式、运行原理、指令流水线、异常处理

工程搭建

环境安装、工程搭建

汇编指令

数据处理、跳转、load/store、状态寄存器、异常中断、协处理器

CPU控制硬件原理

原理、实验(汇编语言、C语言)

学习方法

- 底层课程导学

接口技术

GPIO:通用输入输出;使能、配置模式(输出)、输出类型(推挽/开漏)、输出速度、输出数据

串口:UART、232、485、SPI、I2C、单总线、CAN、USB、

无线通信:WIFI、LoRA、Zigbee、NB-IoT、蓝牙、4G、5G

PWM:脉冲宽度调制(调节平均电压、屏幕、电机)

ADC:模数转换

嵌入式系统

嵌入式系统(了解)

Linux层次结构

进程管理:进程的创建、调度、销毁、通信。。。。

内存管理:内存的申请、释放、映射。。。。

文件管理:访问硬盘的文件

设备管理:硬件设备的驱动文件

网络管理:协议栈(TCP/IP、UDP/IP)进行通信

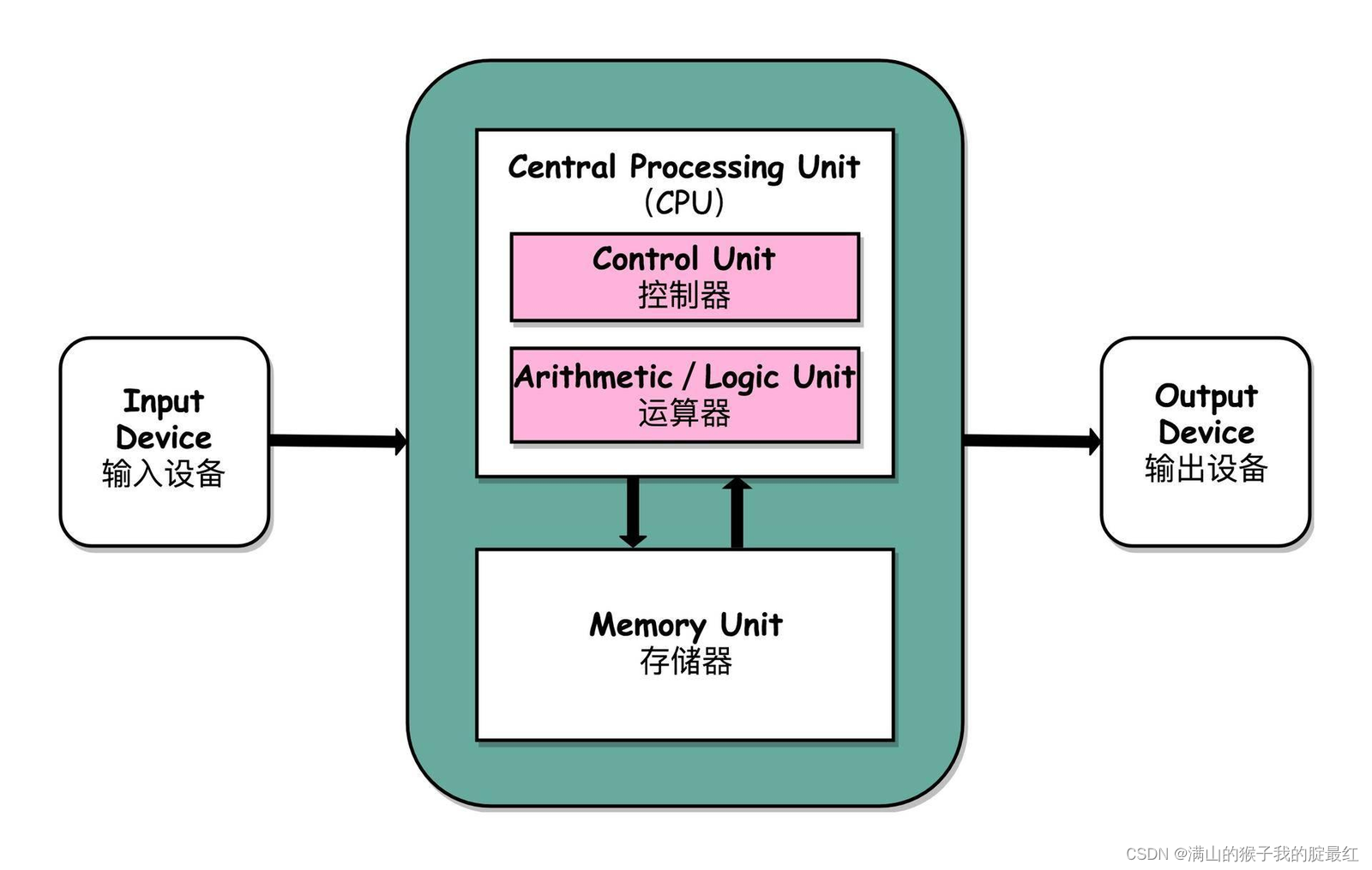

计算机的组成

控制器、运算器、存储器、输入、输出

- 输入设备:将其他信号转换为计算机可以识别的信号(电信号)。

- 输出设备:将电信号(0、1)转为人或其他设备能理解的信号。

- 运算器:CPU对信息处理和运算的部件,常进行算术运算和逻辑运算,其核心是算术逻辑单元ALU,CPU中用各种各样的数字电路搭配成各种各样的运算电路,如:加、减法等。

- 控制器:整个计算机的控制中心

- 存储器:存放程序和数据的部件,也是计算机能够实现“存储程序控制”的基础。

程序:指令的有序集合

ROM: flash (EMMC)、磁盘空间 、掉电不丢失数据

只读存储器_百度百科

RAM: 内存、掉电丢失数据

随机存取存储器_百度百科

计算机的进制

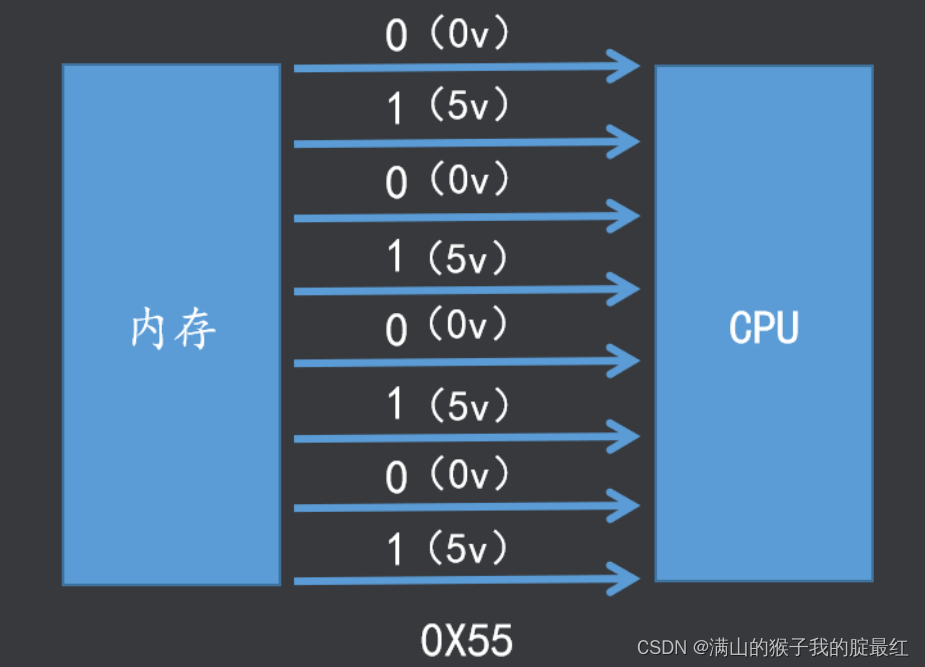

计算机系统中使用高、低电平表示逻辑1和0

数据在计算机中的存储、传输、运算(数据的处理方式)都是以二进制的形式进行的

数据的传输通过总线(Bus)真正传递的是电信号,高低电平(0、1)。运算在电路中进行,集成电路中运算。

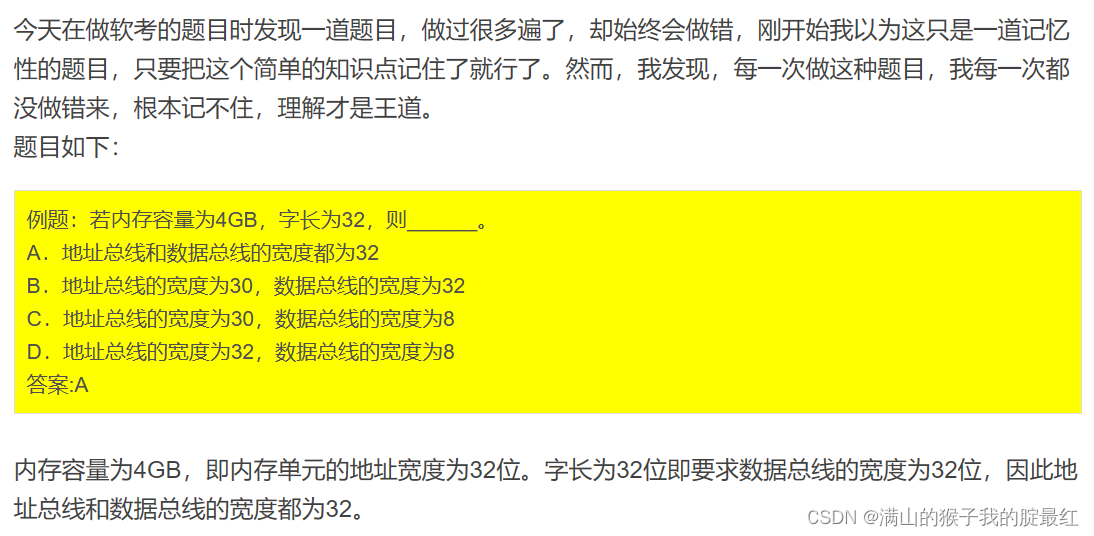

总线

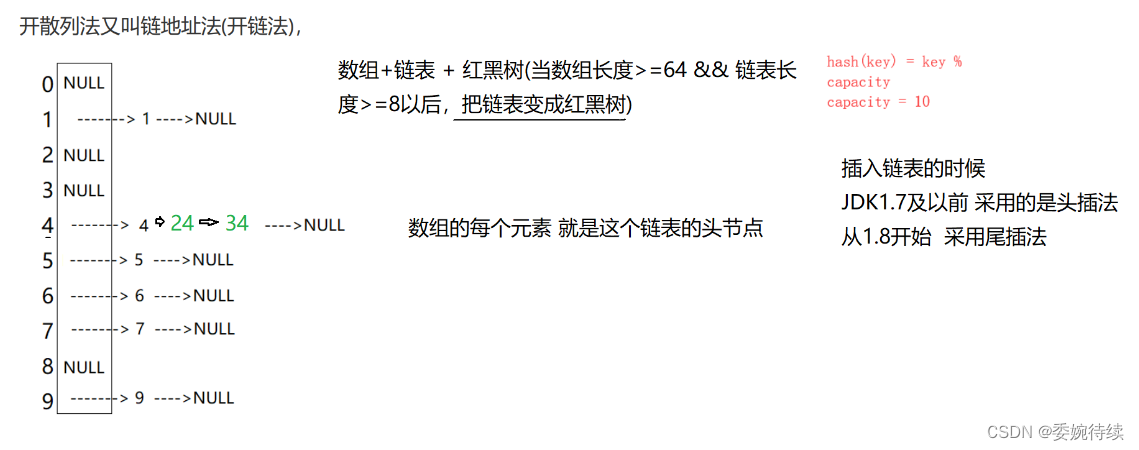

总线

总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束, 按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。

数据总线

(1)是CPU与内存或其他器件之间的数据传送的通道。

(2)数据总线的宽度决定了CPU和外界的数据传送速度。

(3)每条传输线一次只能传输1位二进制数据。如: 8根数据线一次可传送一个8位二进制数据(即一个字节)。

(4)数据总线是数据线数量之和。

地址总线

(1)CPU是通过地址总线来指定存储单元的。

(2)地址总线决定了cpu所能访问的最大内存空间的大小。如: 10根地址线能访问的最大的内存为1024位二进制数据(1024个内存单元)

(3)地址总线是地址线数量之和。

控制总线

(1)CPU通过控制总线对外部器件进行控制。

(2)控制总线的宽度决定了CPU对外部器件的控制能力。

(3)控制总线是控制线数量之和。

总结:

数据总线的宽度决定CPU与其他元器件一次最大传送的数据量;

地址总线的宽度决定CPU的寻址能力;

控制总线决定CPU对其他元器件的控制能力。

DMA总线

DMA(Direct Memory Access)即直接存储器访问,使用DMA总线可以不通过CPU直接在存储器及外设之间进行数据传递。

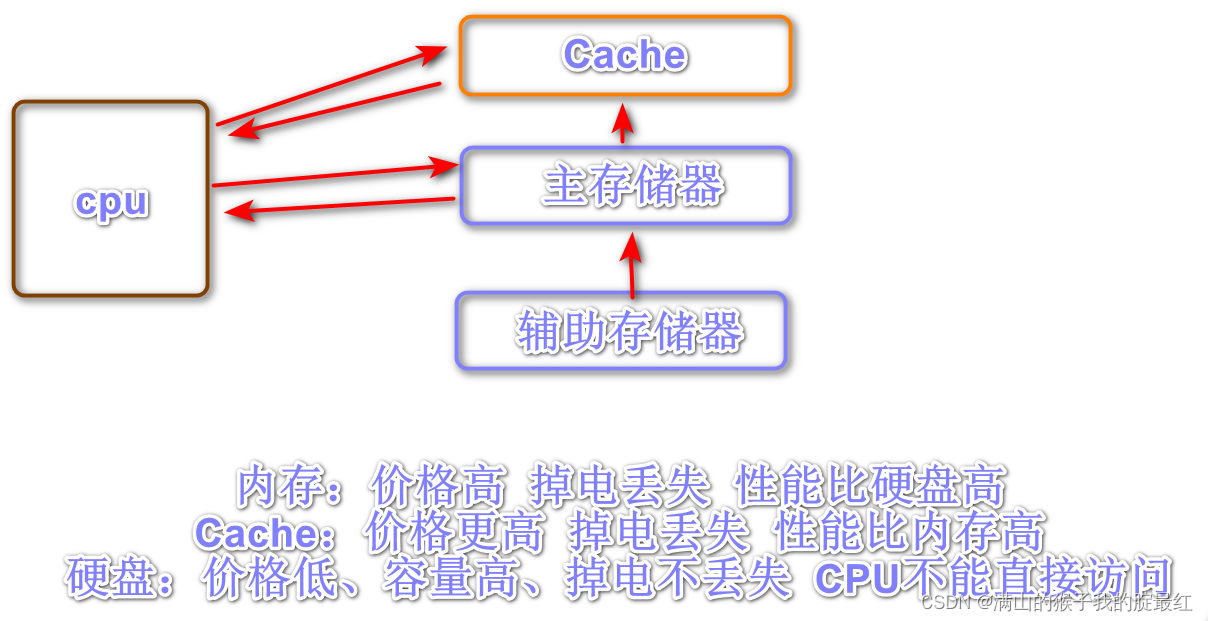

三级存储结构

cache: 速度快、价格贵、容量小、断电丢失、CPU可以直接访问。存储当前正在执行的程序中的活跃部分,以便快速地向CPU提供指令和数据

基本原理:

Cache的基本原理_cache颠簸-CSDN博客

高速缓存Cache详解(西电考研向)-CSDN博客

主存储器:速度、价格、容量介于CACHE和辅助存储器之间、断电丢失、CPU可以直接访问。存储当前正在执行的程序和数据

辅助存储器:速度慢、价格低、容量大、断电不丢失、cpu不可以直接访问。存储暂时不运行的程序和数据,需要时再传送到主存。

Cache对程序员来说一般会有透明性,也就是程序员其实是看不到Cache的,因此不能对它进行操作。

- ARM体系结构

认识ARM

ARM的含义?

- ARM代表一个公司

安谋国际科技股份有限公司_百度百科

1978年Acorn成立于英国剑桥

1980年晚期,苹果电脑开始与艾康电脑合作开发新版的ARM核心

1985年开发出全球第一款商用RISC处理器-ARM

1990年艾康电脑财务危机,苹果和VLSI投资,独立出子公司Advanced RISC Machines(ARM)

1991年,ARM推出RISC处理器-ARM6 93-ARM7 97--ARM9TDMI 99--ARM9E

2001--ARMV6 2002--ARM11

2004年,发布ARMV7架构的Cortex系列处理器,同时推出Cortex-M3

2005年,发布Cortex-A8处理器 07 M1和Cortex-A9 09 实现Cortex-A9 发布 M0

2010--M4

- ARM可以表示一些处理器的统称

早期经典处理器:ARM7 ARM9 ARM11 家族

Cortex-X系列

新出的,通常用在手机,只用一个(除了天机)-----》价格昂贵

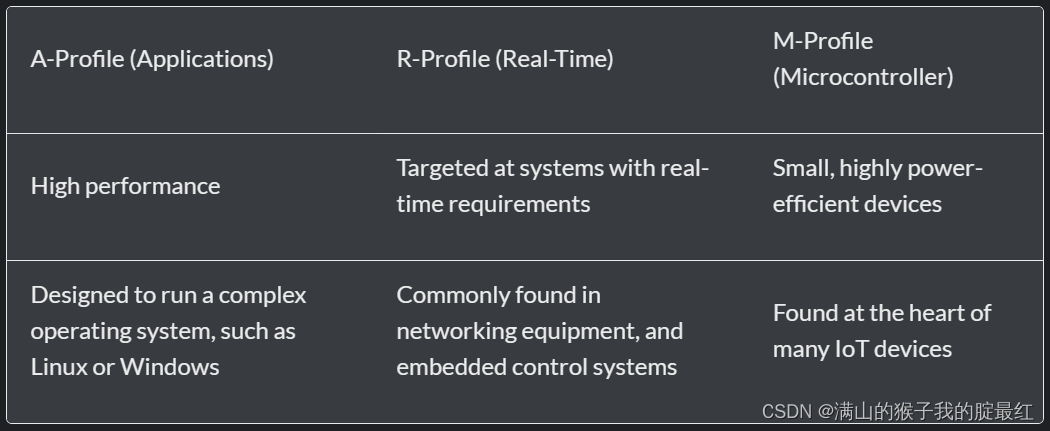

Cortex-A系列

针对开放式操作系统的高性能处理器

应用于智能手机、数字电视、智能本等高端运用

Cortex-R系列

提供非常高的性能和吞吐量,同时保持精准的时序属性和可预测的中断延时,通常用于时序关键的应用中

针对实时系统、满足实时性的控制需求

应于汽车制动系统、动力系统等

Cortex-M系列

为单片机驱动的系统提供了低成本优化方案

应用于传统的微控制器市场、智能传感器、汽车周边等

- ARM表示一种指令集

指令:能够指示处理器执行命令称之为指令

指令集:处理器能够识别的指令的集合称为指令集

ARM指令集:所有指令(机器码),都专用32bit存储空间,代码灵活,指令简洁,执行ARM指令PC每次自加4

Thumb指令集:所有指令(机器码),都专用16bit存储空间,代码灵活,指令简洁,执行ARM指令PC每次自加2

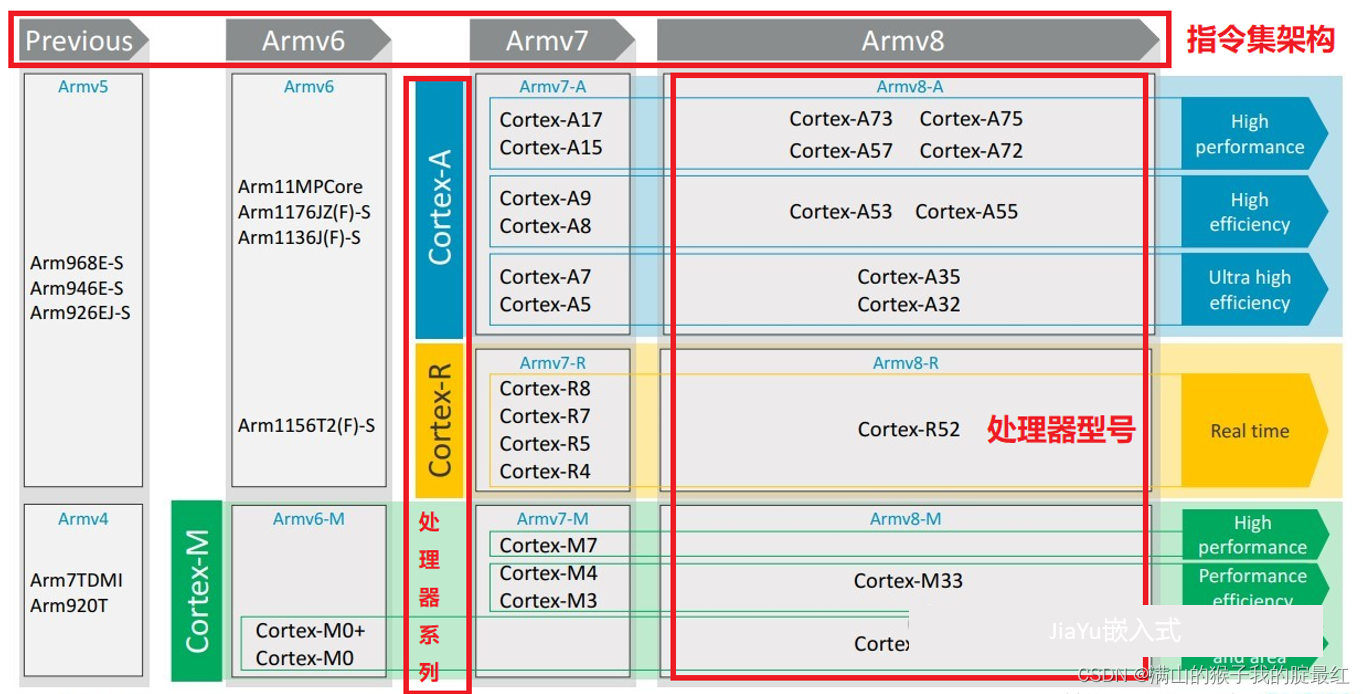

ARM的命名有指令集架构、 处理器架构、 处理器型号三类命名规则

架构:

arm-v6,arm-v7(32Bits),arm-v8(64Bits),arm-v9.2

架构指支持的汇编指令集(不同架构,汇编指令集不同)

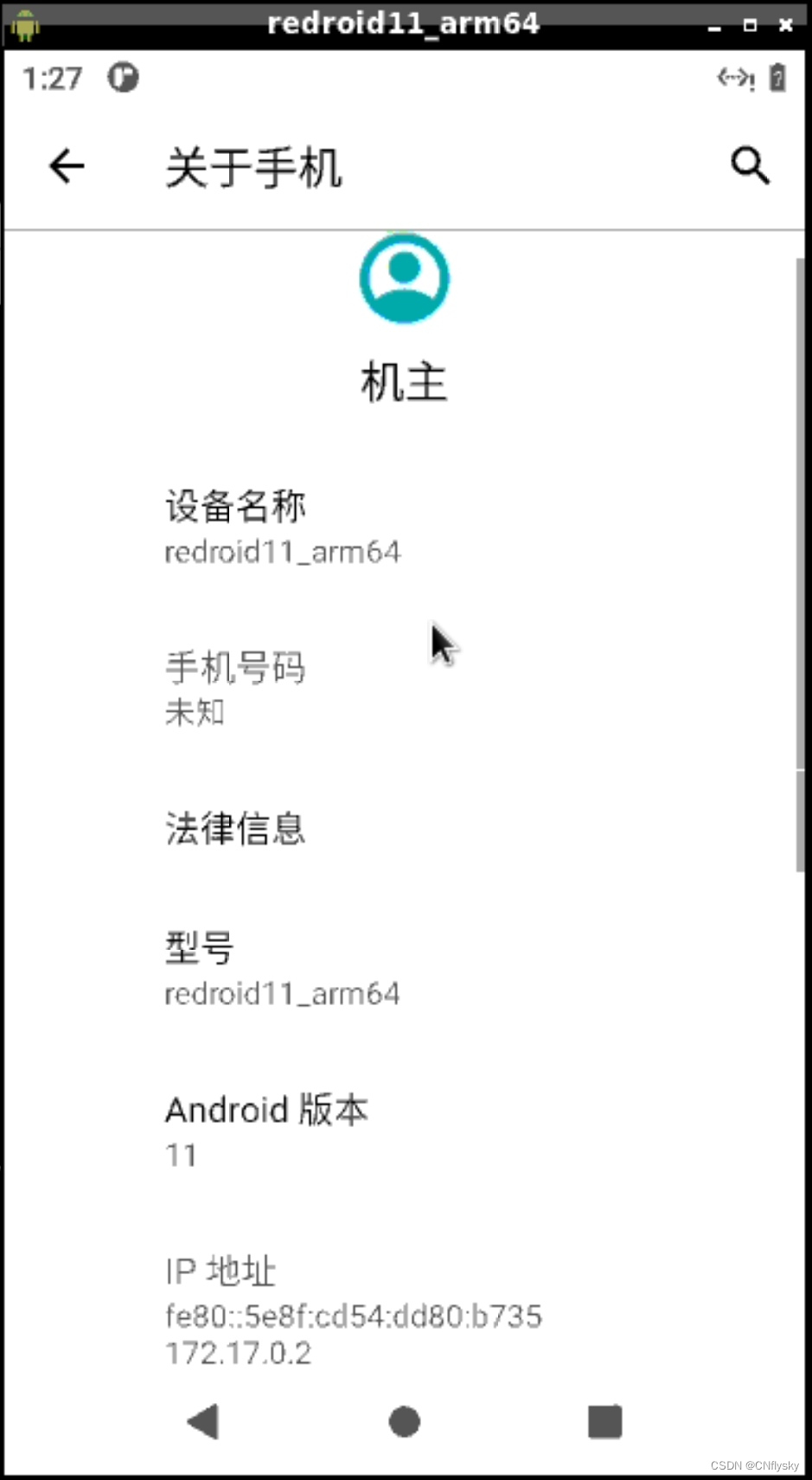

ARMv8-A--------->A53-------->S5P6818 (主频:1.4GHz)

内核:

cortex-A9,A53,A73,A77

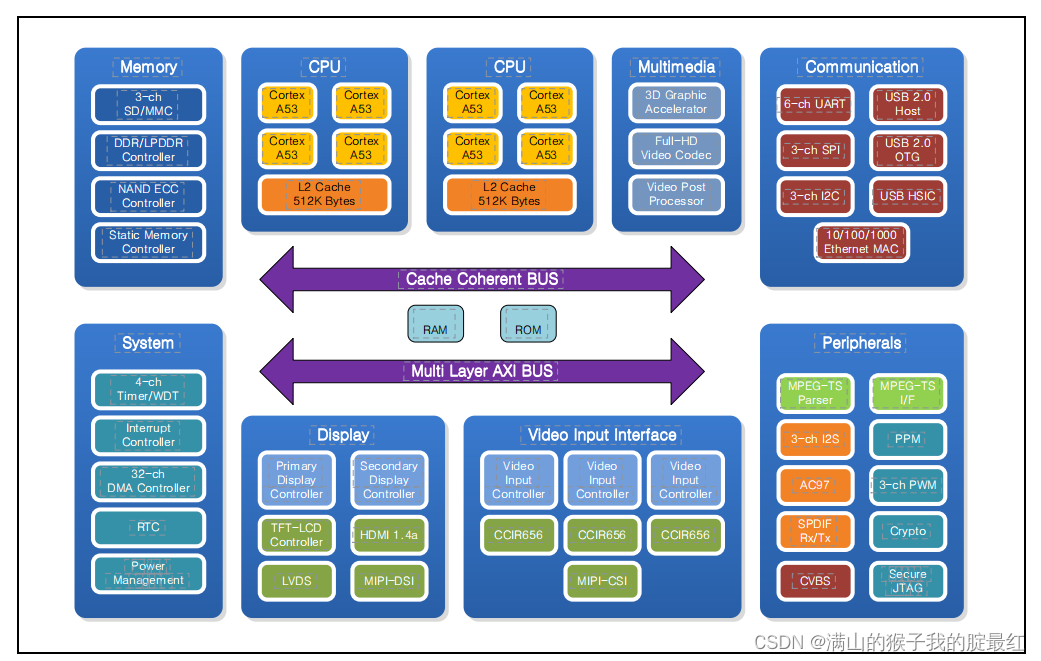

ARM公司授权芯片的公司,芯片产家在内核的基础上,增加了一些外设,发布一款芯片,这些芯片可以统称为SoC(天机9300、骁龙)

SoC:System of Chip:(片上系统)

S5P6818(8核)

指令集(RISC和CISC)

精简指令集(RISC)-->微处理器

只保留常用的的简单指令,硬件结构简单,复杂操作一般通过简单指令的组合实现,一般指令长度固定,且多为单周期指令。

RISC处理器在功耗、体积、价格等方面有很大优势,所以在嵌入式移动终端领域应用极为广泛

举例:如有加法运算器 ,没有乘法运算器 3*3 ---》3+3+3

复杂指令集(CISC)-->电脑CPU

不仅包含了常用指令,还包含了很多不常用的特殊指令,硬件结构复杂,指令条数较多,一般指令长度和周期都不固定

CISC处理器在性能上有很大优势,多用于PC及服务器等领域

ARM-v7架构:

ARM 指令集(32-bit) :一条指令占32位内存空间

Thumb 指令集(16-bit ):一条指令占16位内存空间

ARM-V8架构:(向下兼容ARM-v7架构)

ARM指令集:A64

Thumb指令集:T32

ARM-v7:

ARM指令集:A32

Thumb指令集:T16

ARM指令集功能更全,性能更高

thumb指令集比ARM指令集指令密度要大

指令对比查看

- 查看精简指令的指令(可以编译后,用反汇编查看代码指令)

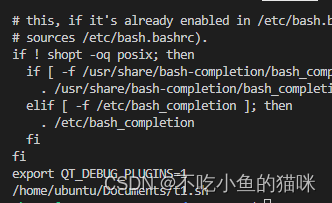

使用交叉编译工具编译程序,生成arm的可执行程序

创建一个a.c文件,随便写一个程序

编译生成a.out可执行文件:arm-none-linux-gnueabi-gcc a.c

查看可执行文件属性:file a.out

使用反汇编的命令将elf文件转换为反汇编文件.dis

arm-none-linux-gnueabi-objdump -D a.out > a.dis

- 查看ubuntu复杂指令集的指令:

编译生成a.out可执行文件:gcc a.c

查看文件属性:file a.out

反汇编:objdump -D a.out > a.dis

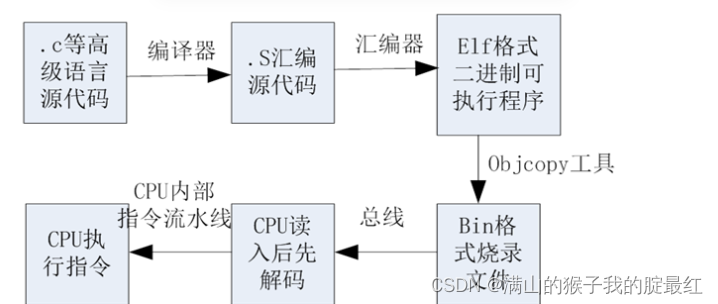

编译原理

机器码(二进制)是处理器能直接识别的语言,不同的机器码代表不同的运算指令,处理器能够识别哪些机器码是由处理器的硬件设计所决定的,不同的处理器机器码不同,所以机器码不可移植

汇编语言是机器码的符号化,即汇编就是用一个符号来代替一条机器码,所以不同的处理器汇编也不一样,即汇编语言也不可移植

C语言在编译时我们可以使用不同的编译器将C源码编译成不同架构处理器的汇编,所以C语言可以移植

ARM的数据类型

ARM-v7架构:32bit处理器

char:8位

halfword:16位

word:32位

doubleword:64位(cortex-a)

ARM-v8架构:64bit处理器 ,向下兼容32位(我们学习32位)

char:8位

halfword:16位

word:32位

doubleword:64位(cortex-a)

quadword:128位(ARM-v8)

处理器的32位和64位什么含义?

32位:一条指令可以进行32位数据的运算

64位:一条指令可以进行64位数据的运算

字节序

大端对齐

低地址存放高字节,高地址存放低节字

小端对齐

低地址存放低字节,高地址存放高字节

注:ARM一般使用的是小端对齐

(1.指针 2.共用体)