【SV】为什么需要异步复位?同步输入/异步输入、异步复位/同步复位(bad)、同步系统/异步系统

- 1. 同步输入/异步输入(synchronous and asynchronous inputs in sequential system)

- 为什么需要异步复位?

- 1.1 异步复位Asynchronous reset

- Explanation:

- Further knowledge:

- 1.2 Asynchronous reset and synchronous reset

- 1.3 异步复位同步释放Synchronized Asynchronous Reset

- 2. 同步系统/异步系统Synchronous/Asynchronous System

同步输入/异步输入、同步系统/异步系统、阻塞赋值/非阻塞赋值

Synchronous/Asynchronous inputs and system, Synchronous/Asynchronous reset

1. 同步输入/异步输入(synchronous and asynchronous inputs in sequential system)

为什么需要异步复位?

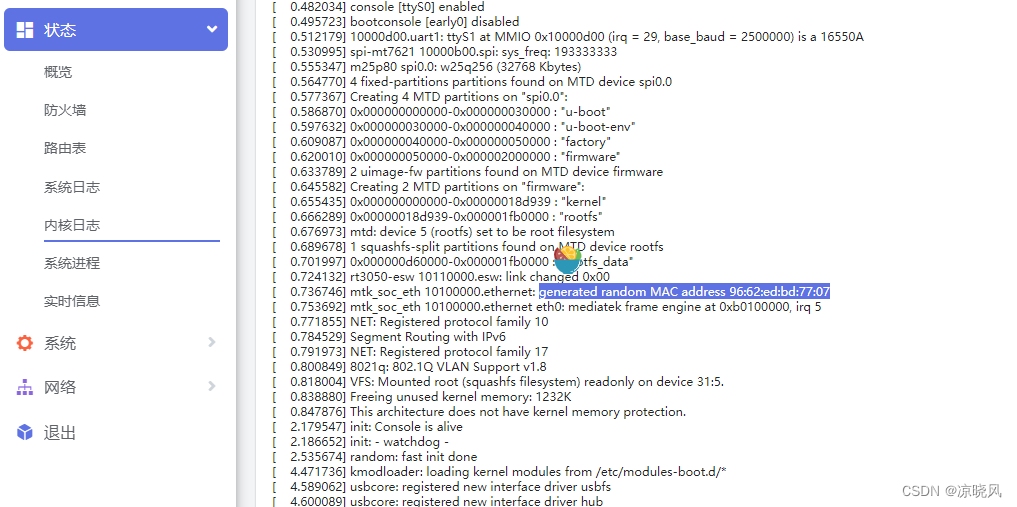

Explain the difference between synchronous and asynchronous inputs to a sequential system. For what purpose should an asynchronous reset input be used?

-

Synchronous inputs are enabled only if the clock signal is valid (synchronous input signals are dependent with clock), while asynchronous inputs is unrelated to the clock signal, it can be enabled in any point of the clock time, which ‘asynchronous’ means that the transition to a new state happened as soon as inputs had stabilized.

-

Asynchronous inputs to flip-flops only used for initialization. Asynchronous reset is used to initialize the system when it is first turned on.

1.1 异步复位Asynchronous reset

Explanation:

Because when power is first applied to a flip-flop its initial state is unpredictable, and in many applications, this is unacceptable, so flip-flops are provided with further inputs to set (or reset) their outputs to 1 or to 0.

Further knowledge:

It is very bad practice to use these inputs to set the state of a flip-flop during normal system operation.

The reason for this is that in synchronous systems, flip-flop only change state when clocked. The set and reset inputs are asynchronous and hence cannot be guaranteed to change an output at a particular time. It can lead to all sorts of timing problems. In general, keep all designs strictly synchronous or follow a structured asynchronous design methodology.

同步信号与异步信号的区别

1.2 Asynchronous reset and synchronous reset

FPGA中同步复位和异步复位的区别,应该怎样选择复位方案?

-

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。相当于对复位reset_n和输入din。

-

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

ps,记得有次做实验,我写成了同步的复位,就导致综合出来的网表有问题,因为网表文件里有个门的输入一直是(1‘b0)很懵逼,导致不能自动布线。后发现是复位信号的问题。

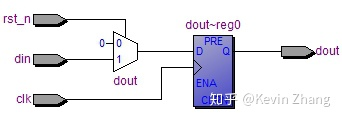

1.3 异步复位同步释放Synchronized Asynchronous Reset

关于“异步复位,同步复位,异步复位同步释放”的理解

异步复位同步释放(Synchronized Asynchronous Reset)

异步复位同步释放

- 目的:防止复位信号撤除时产生亚稳态事件。

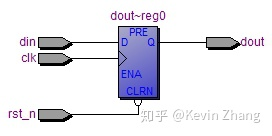

- 异步复位:显而易见,reset_n异步复位后,rst_n将拉低,即实现异步复位。

- 同步释放:这个是关键,看如何实现同步释放,即当复位信号reset_n撤除时,由于双缓冲电路(双寄存器)的作用,rst_n复位信号不会随着reset_n的撤除而撤除。

为了防止亚稳态的出现,将rst_n信号用DFF向后延一周期,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步

2. 同步系统/异步系统Synchronous/Asynchronous System

Difference between Synchronous and Asynchronous Sequential Circuits

|  | ||

|---|---|---|---|

| No. | Key | Synchronous Sequential Circuits | Asynchronous Sequential Circuits |

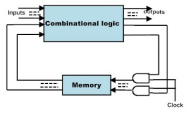

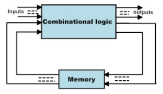

| 1 | Definition | Synchronous sequential circuits are digital sequential circuits in which the feedback to the input for next output generation is governed by clock signals. | On other hand Asynchronous sequential circuits are digital sequential circuits in which the feedback to the input for next output generation is not governed by clock signals. |

| 2 | Memory Unit | In Synchronous sequential circuits, the memory unit which is being get used for governance is clocked flip flop. | On other hand unclocked flip flop or time delay is used as memory element in case of Asynchronous sequential circuits. |

| 3 | State and reality | The states of Synchronous sequential circuits are always predictable and thus reliable. Since all the Internal State changes are in the strict control of a master clock source they are less prone to failure or to a race condition and hence are more reliable. | On other hand there are chances for the Asynchronous circuits to enter into a wrong state because of the time difference between the arrivals of inputs. This is called as race condition.Since there is no such universal clock source, the internal state changes as soon as any of the inputs change and hence are more prone to a race condition.Timings of the internal state changes are in our control. |

| 4 | Complexity | It is easy to design Synchronous sequential circuits | However on other hand the presence of feedback among logic gates causes instability issues making the design of Asynchronous sequential circuits difficult. |

| 5 | Performance | Due to the propagation delay of clock signal in reaching all elements of the circuit the Synchronous sequential circuits are slower in its operation speed | Since there is no clock signal delay, these are fast compared to the Synchronous Sequential Circuits |

| 6 | Example | Synchronous circuits are used in counters, shift registers, memory units. | On other hand Asynchronous circuits are used in low power and high speed operations such as simple microprocessors, digital signal processing units and in communication systems for email applications, internet access and networking. |

Synchronous and Asynchronous Circuits