连续赋值语句可以完成任意组合逻辑,本节对基本的逻辑电路进行测试分析,主要包含一下内容:

1. 反相器

2. 与门

3.与非门

4.或门

5.或非门

6.异或门

7.同或门

verilog实现逻辑操作的算符如下

// ~ .... Invert a single-bit signal or each bit in a bus

// & .... AND two single bits or each bit between two buses

// | .... OR two single bits or each bit between two buses

// ^ .... XOR two single bits or each bit between two buses

// ~^ ... XNOR two single bits or each bit between two buses

1. 反相器

反相器是简单的数字电路。他的功能是实现高低电平的反转。

反相器可以通过~符号可以实现。与c语言一样,都是左边赋值。assign是连续赋值语句的关键字(保留字),等式左边是输出语句,后边的逻辑表达式。反相器的输入有事一个,符号为a,通过~算符运算后,赋值给坐标的y值。y=~a,语句描述了一个反相器电路。一个完成的反相器模块实现如下。

module assign1(

input a,

output y

);

assign y = ~a;

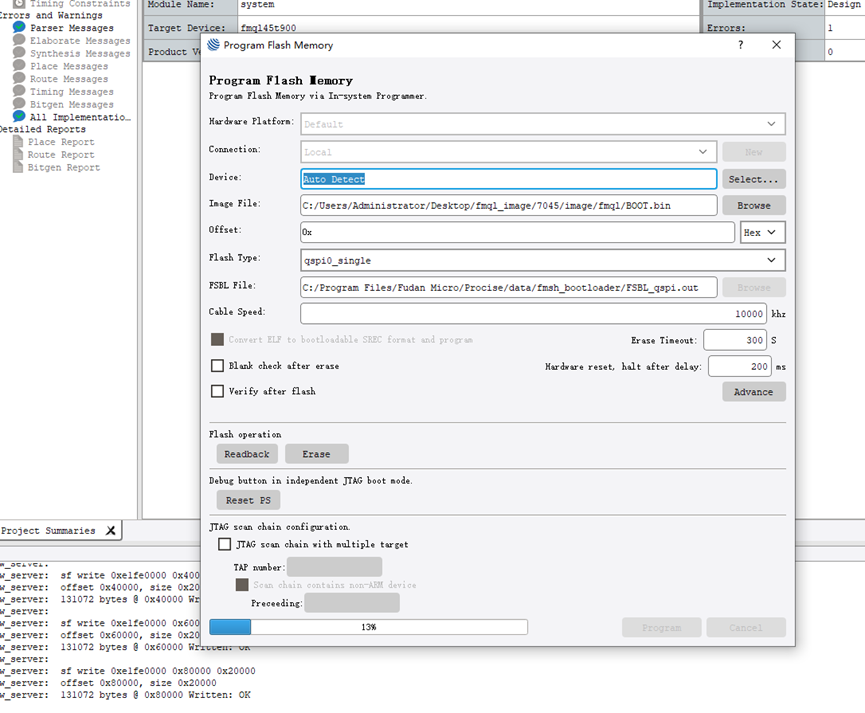

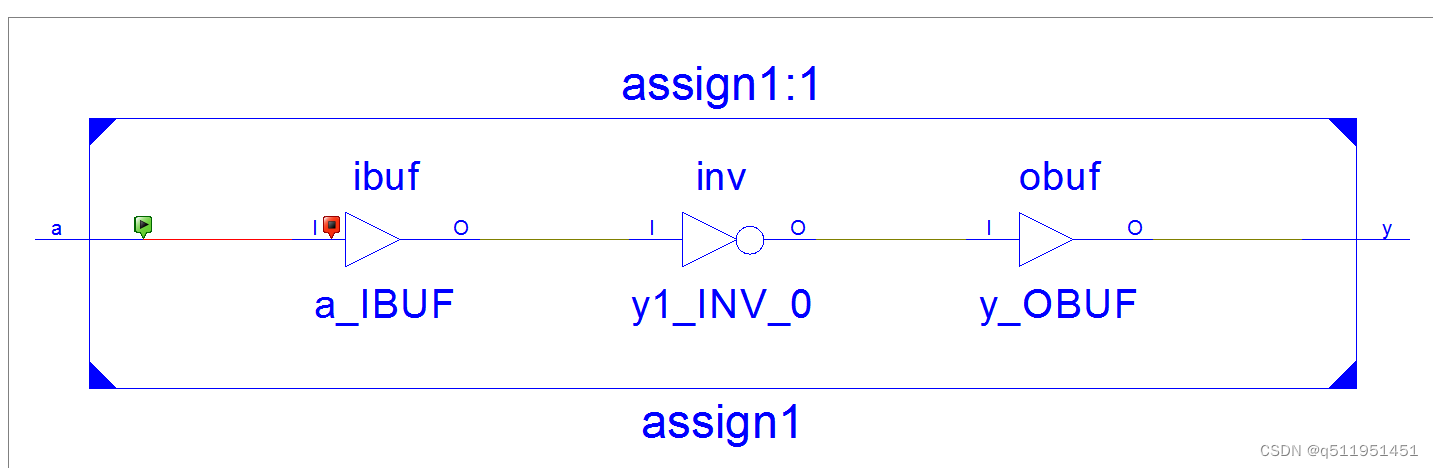

endmodule使用xilinx ise14.7进行综合后,得到RTL原理图以及技术原理图如下图,其中RTL原理图主要显示了反相器的逻辑功能。技术原理图中自动增加了ibuf和obuf原语,使用缓冲级把内部逻辑器件与外部信号线隔离起来。

2. 与门

与门的输入可以是2-n输入,以下演示2-5输入与门电路。

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = a2&a1;

assign y3 = a3&a2&a1;

assign y4 = a4&a3&a2&a1;

assign y5 = a5&a4&a3&a2&a1;

endmodule

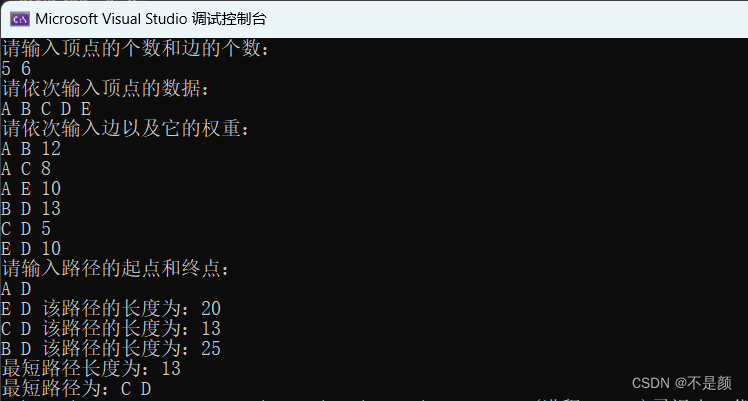

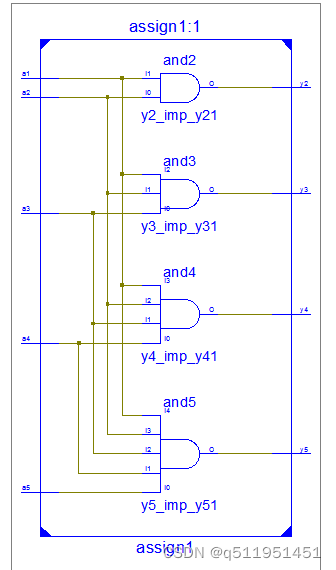

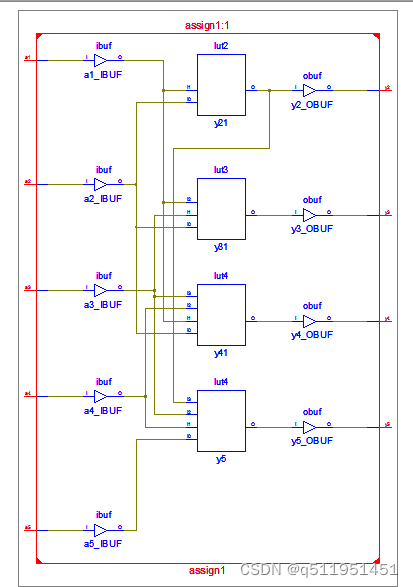

RTL原理图如下,寄存器传输级的原理图与预期的一致。多输入与门模块

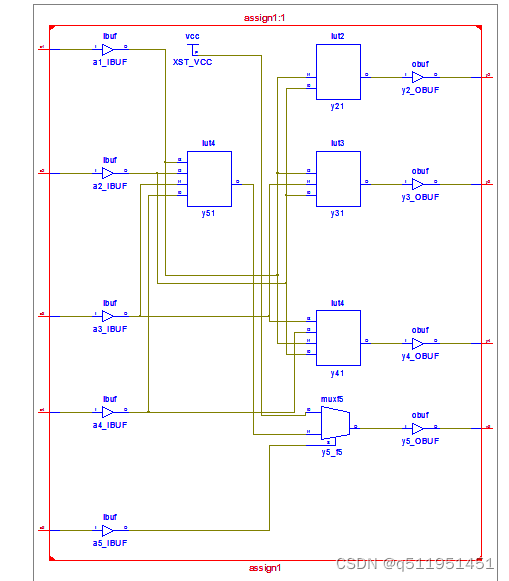

XST综合后的技术原理图如下,FPGA使用lut4查找表来实现组合逻辑。4个与门有4个输出,使用了4个lut来实现。双击lut可以查看lut具体实现的组合逻辑功能,

双击lut4得到如下结果

3.与非门

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = ~(a2&a1);

assign y3 = ~(a3&a2&a1);

assign y4 = ~(a4&a3&a2&a1);

assign y5 = ~(a5&a4&a3&a2&a1);

endmodule

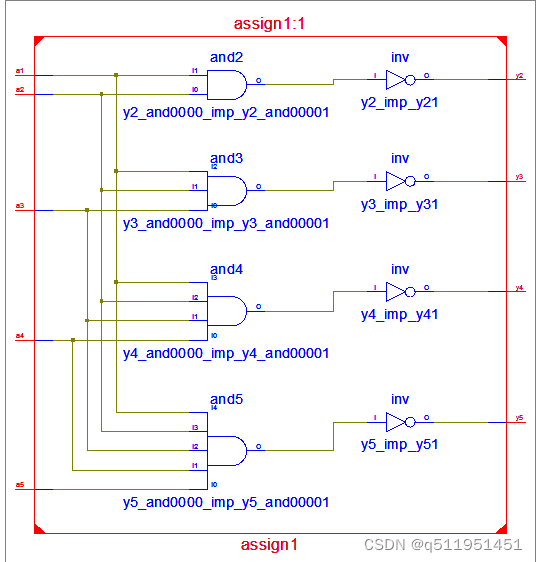

RTL原理图

技术原理图,由技术原理图可知,2-4输入与非门,使用Lut查找表即可实现,而5输入与非门需要一个与非门与一个mux二选一选择器时间。

双击lut4-y51得到内部逻辑结构如下

等效增值表

等效方程

小结:

选择器是fpga的基本结构,他可以与lut结合起来实现组合逻辑。

4. 或门

代码

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = (a2|a1);

assign y3 = (a3|a2|a1);

assign y4 = (a4|a3|a2|a1);

assign y5 = (a5|a4|a3|a2|a1);

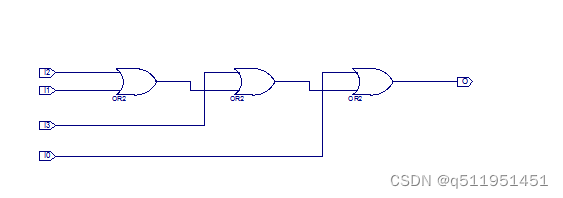

endmoduleRTL结构图

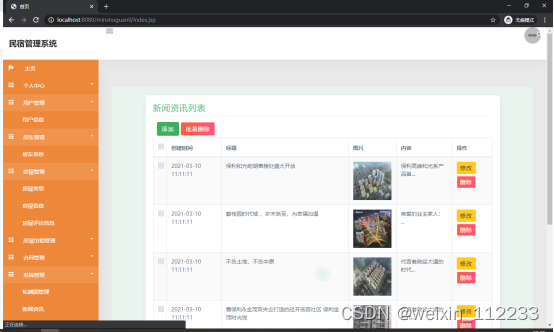

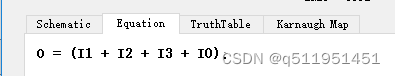

技术原理图,总共由4个lut实现组合逻辑,其中lut2+lut4/ y21+y5一起实现了5输入或门

y5的lut表

y5等效方程

6. 或非门

代码

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = ~(a2|a1);

assign y3 = ~(a3|a2|a1);

assign y4 = ~(a4|a3|a2|a1);

assign y5 = ~(a5|a4|a3|a2|a1);

endmoduleRTL结构图

技术原理图,或非门电路就是在或门电路后面增加一级反相器来实现。

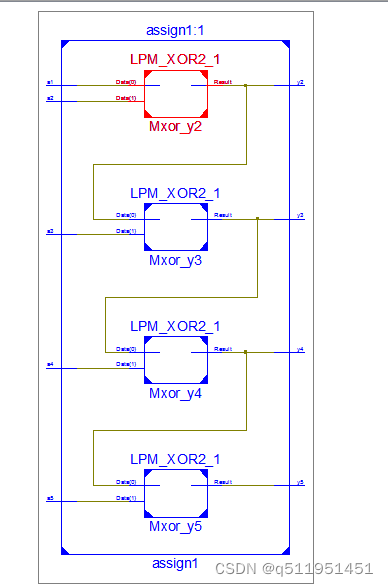

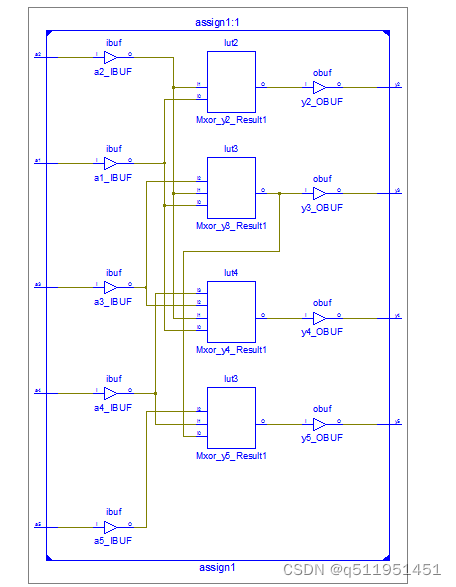

7. 异或门

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = (a2^a1);

assign y3 = (a3^a2^a1);

assign y4 = (a4^a3^a2^a1);

assign y5 = (a5^a4^a3^a2^a1);

endmoduleRTL结构图

技术原理图,异或门采用Lut查找表来实现,超过5输入的异或门采用两个Lut查找表来实现。

双击y5的lut

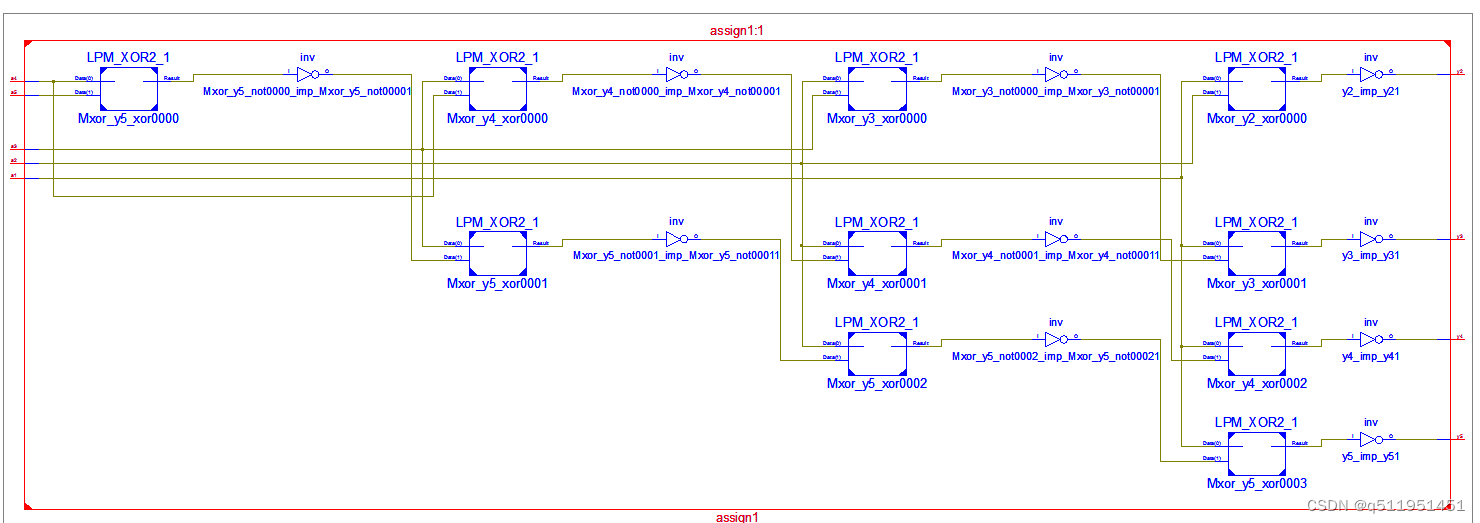

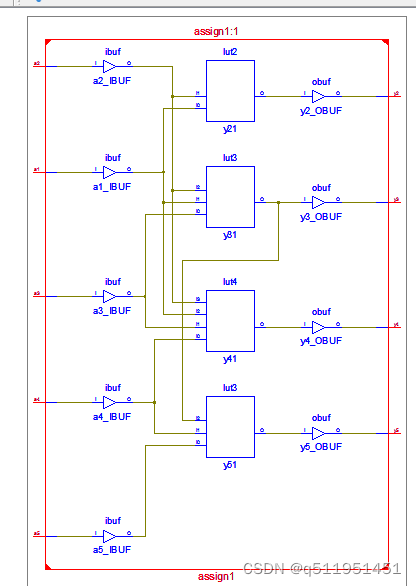

8. 同或门

代码

module assign1(

input a5,

input a1,

input a2,

input a3,

input a4,

output y2,

output y3,

output y4,

output y5

);

assign y2 = (a2~^a1);

assign y3 = (a3~^a2~^a1);

assign y4 = (a4~^a3~^a2~^a1);

assign y5 = (a5~^a4~^a3~^a2~^a1);

endmodule

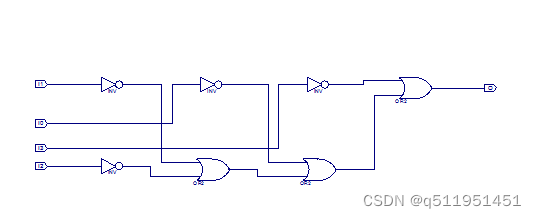

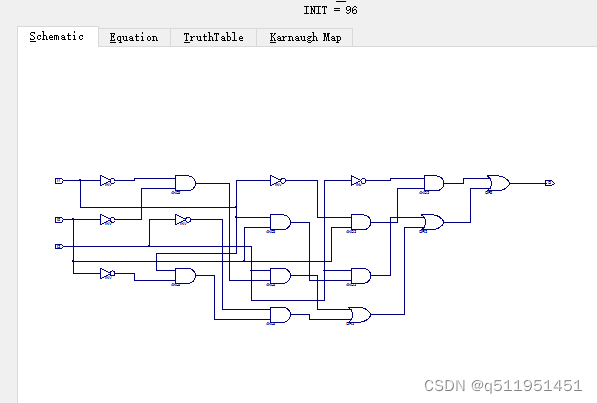

RTL结构图,同或门的结构让人眼花缭乱,不用担心,它的本质还是使用lut实现。

技术原理图,使用查找表实现的同或门如下,不管组合逻辑有多么复杂,完全可以使用查找表实现。这不仅简化了逻辑电路的实现,还可以实现逻辑电路编程。这是FPGA使用ram来制作查表来替代门电路的原因。

双击一下y51-lut查找表,内部实现的逻辑功能还是很复杂的。

总结

1. verilog的基本组合逻辑运算可以用assign语句实现,通过基本逻辑算符如~、&、|、^、~^来实现具体的组合逻辑功能。

2. FPGA的反相器使用反相器电路实现,与门,与非门,或门,或非门,同或,异或等多输入组合逻辑均采用lut查找表实现。另外部分组合逻辑可以使用Lut查找表+mux选择器来实现。主要的目的就是简化FPGA资源的使用

3. 逻辑功能的实现都是通过综合工具自动设计的。verilog将功能与具体的逻辑门设计隔离开来,极大的增加了开发效率,是目前verilog商用化的主要原因。另外他也存在缺点,使用verilog语言,让我们对门电路的认识不足,不利于查找电路问题以及进行电路优化,对于高性能的研究还是需要使用VHDL语言。幸运的是,使用verilog基本就满足大多数场景的应用了。