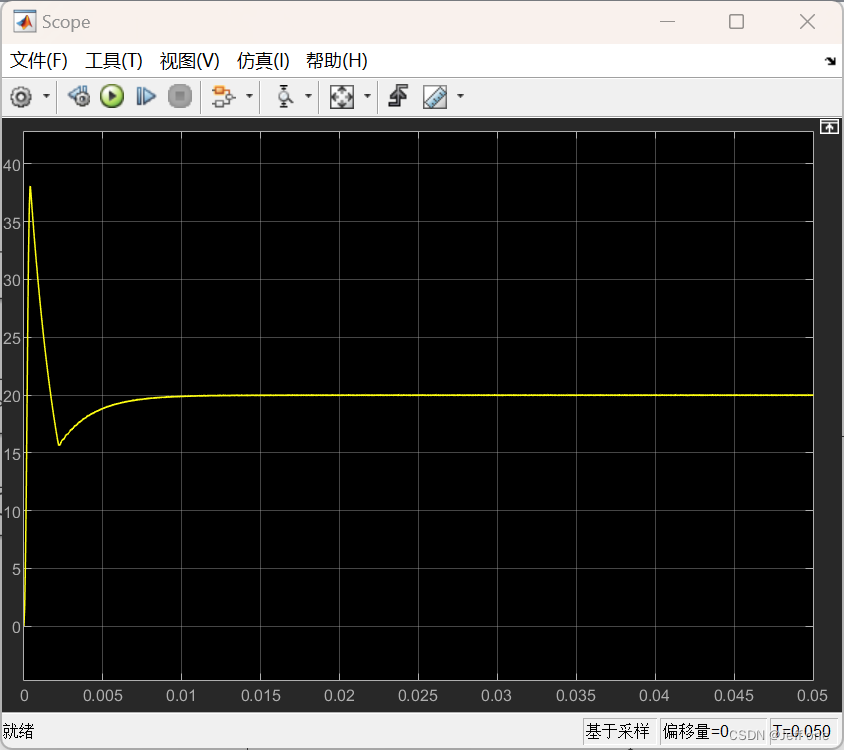

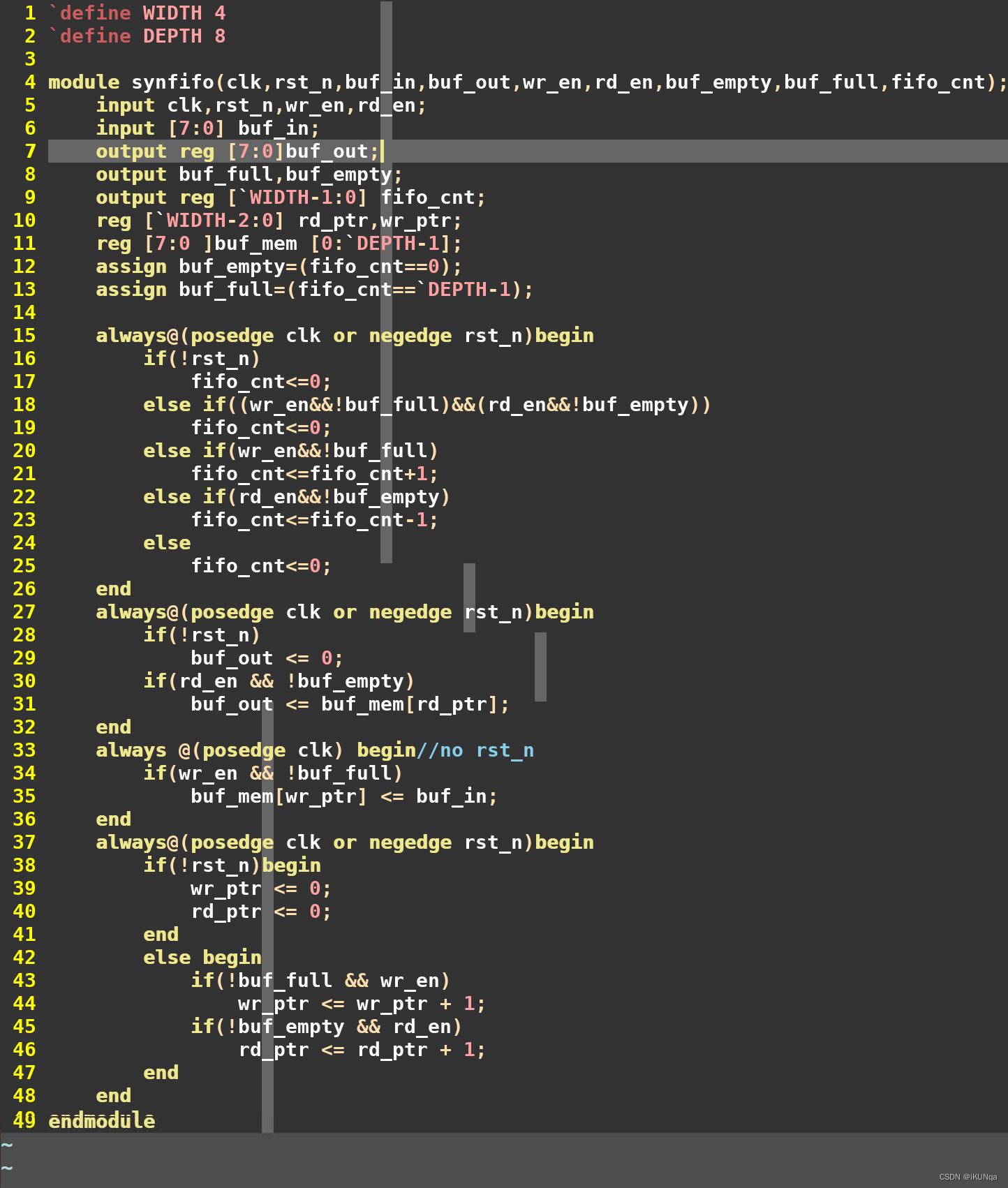

同步fifo,写时钟和读时钟为同一个时钟,用于交互数据缓冲

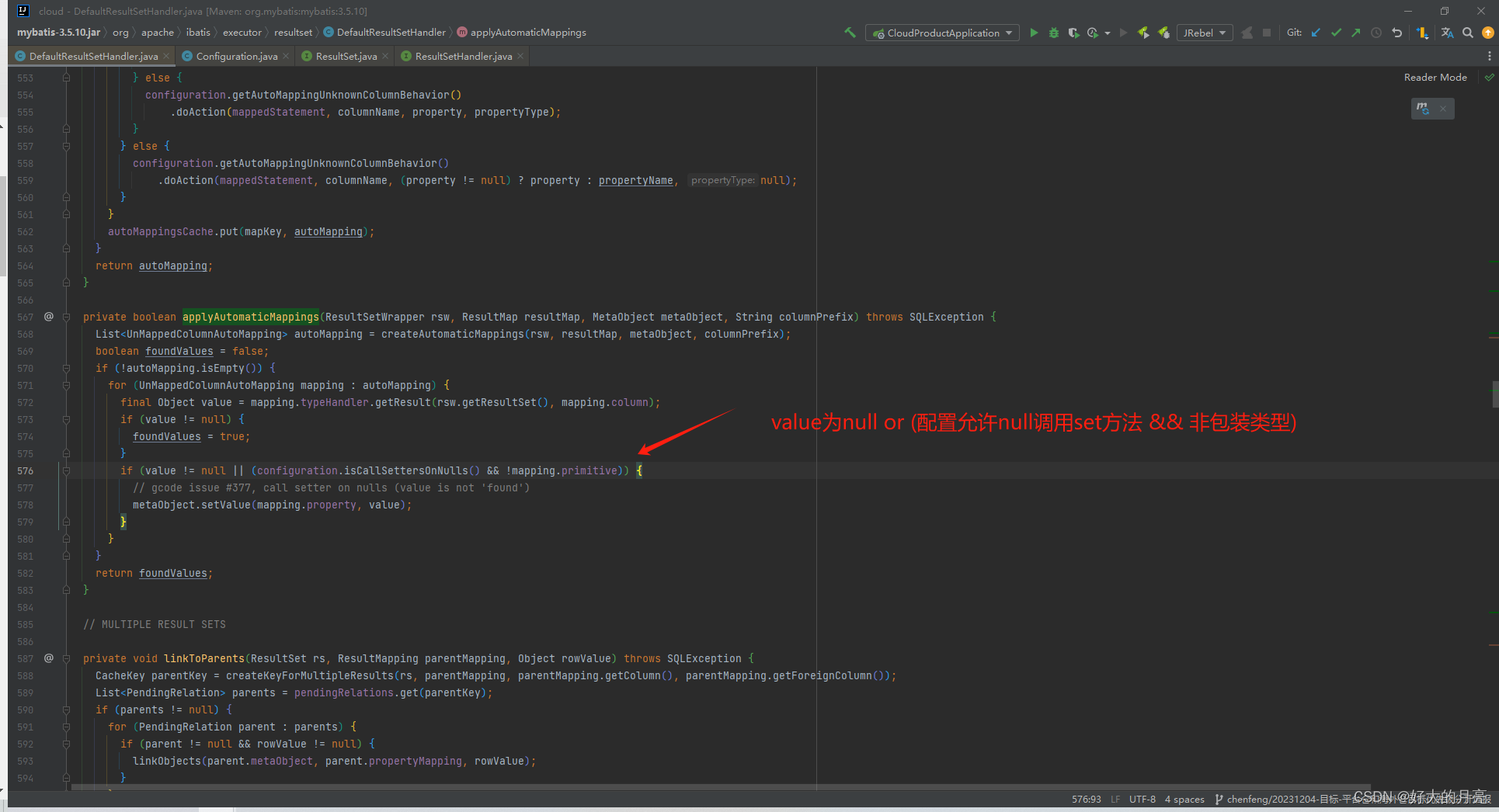

fifo的深度:同一块数据内存的大小

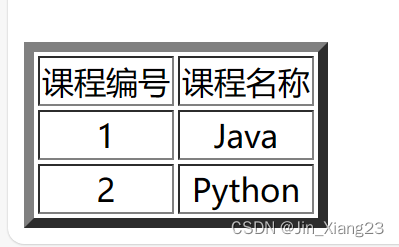

reg [2:0] Mem [8];//宽度3,深度8

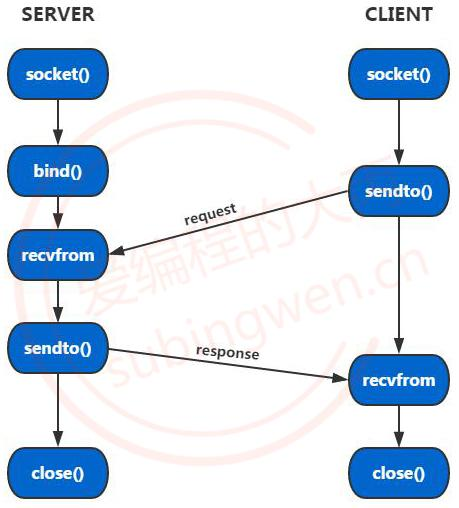

典型同步fifo的三部分

fifo写控制逻辑:写地址、写有效信号,fifo写满、写错等状态信号

fifo读控制逻辑:读地址、读有效信号,fifo写满、写错等状态信号

fifo存储实体memory/reg

空满判断

reg [2:0] Mem [8];//宽度3,深度8

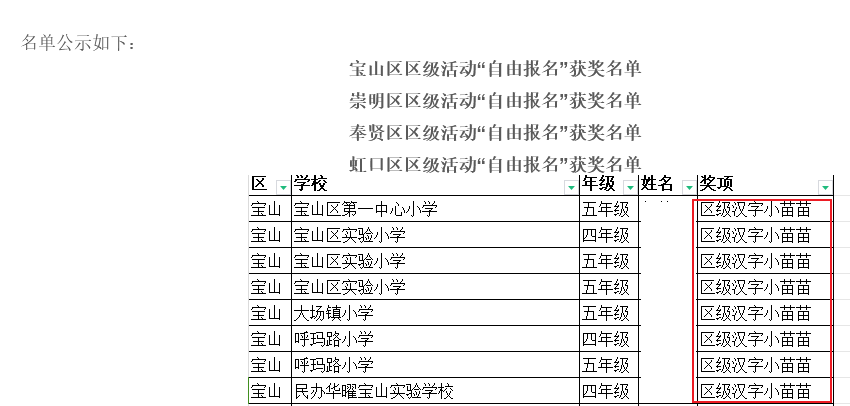

写指针Wr_ptr指向空,读指针Rd_ptr指向满

读写处于一个地址,用最高位的状态判断空与慢

写地址0011,读地址0011:空

写地址1011,读地址0011:满

一般fifo使用循环指针,不使用该判断,简单判断:个数为0空,个数为深度满

端口

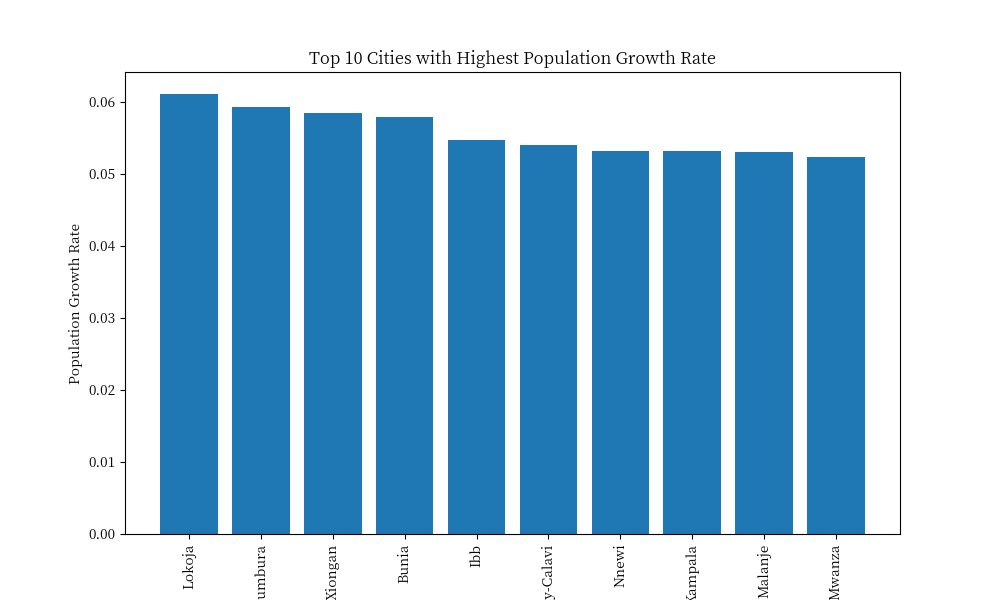

fifo_counter:0时,给出empty;等于fifo深度时,给出full

fifo_counter:写而未满时,加1;读而未空:-1;同时读写时,不变

读写地址宽度:与地址宽度相同;地址增加溢出时,变为0;循环指针

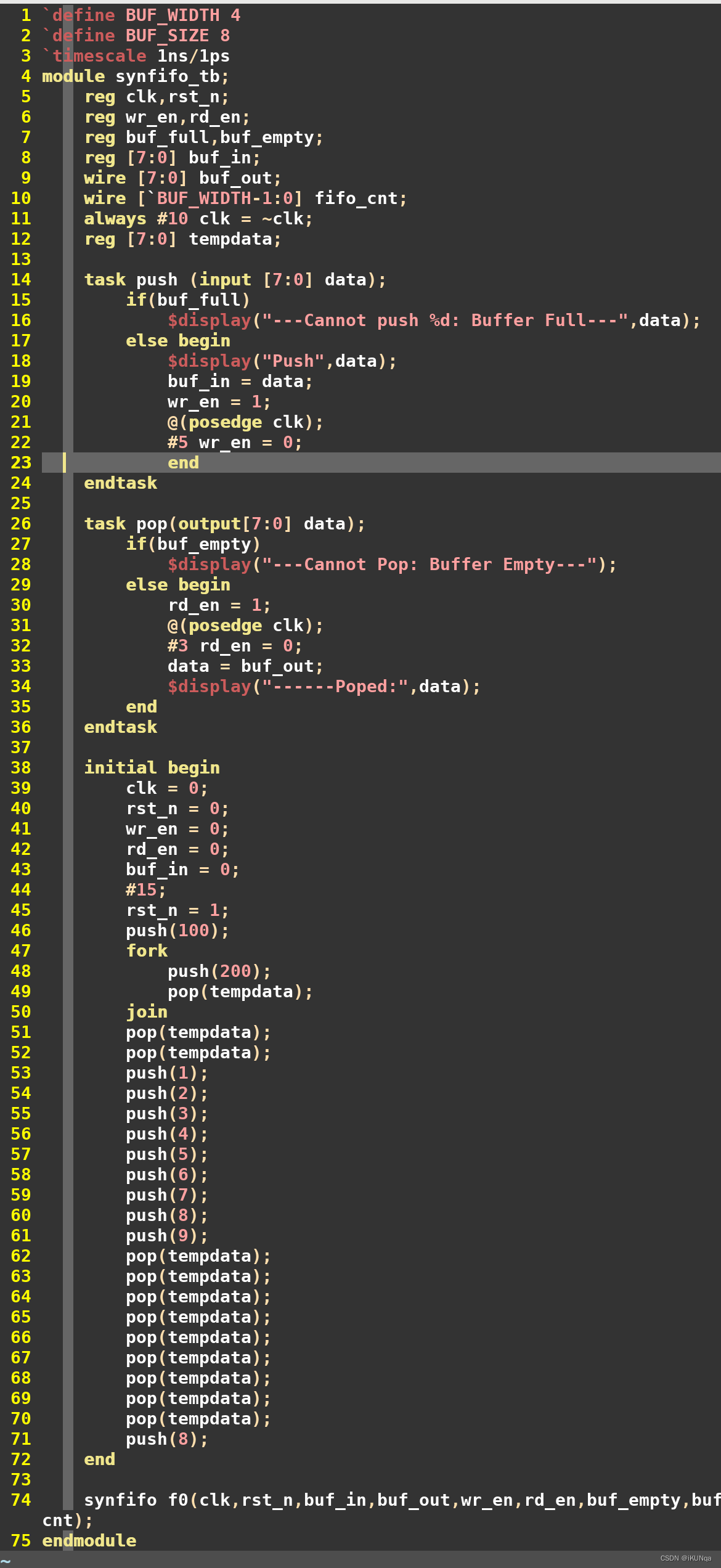

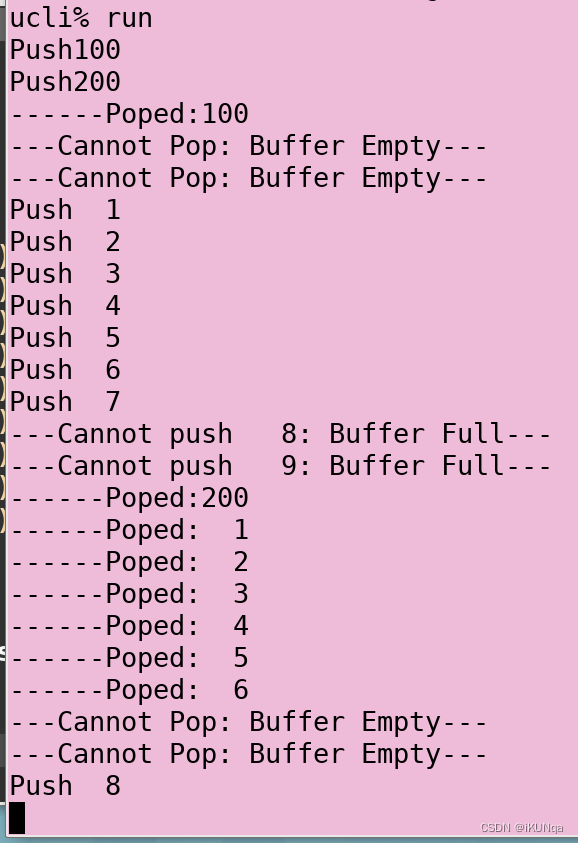

实现

结束该进程,ctrl+c再按q

问题:读不出第一个push数据