前言:

随着集成电路规模的越来越大,如今的大规模芯片都集成了很多功能模块,但是在实际的电路设计中我们又不可能把芯片所有的功能模块(或者说接口)全部用上,因此总会有或多或少的管脚会“用不上”,那这些未用的管脚一般怎么处理呢?

一、对于一般未用管脚的处理,分三步走

第一步:管脚分类(Input or Output or Bidirectional)

——对于Input pin需要看芯片手册对于该引脚的固定电平要求

——对于Output pin一般可以直接悬空处理的(除非芯片手册有特别要求)

——对于Bidirectional一般可以直接当做Output pin对待(除非芯片手册有特别要求)

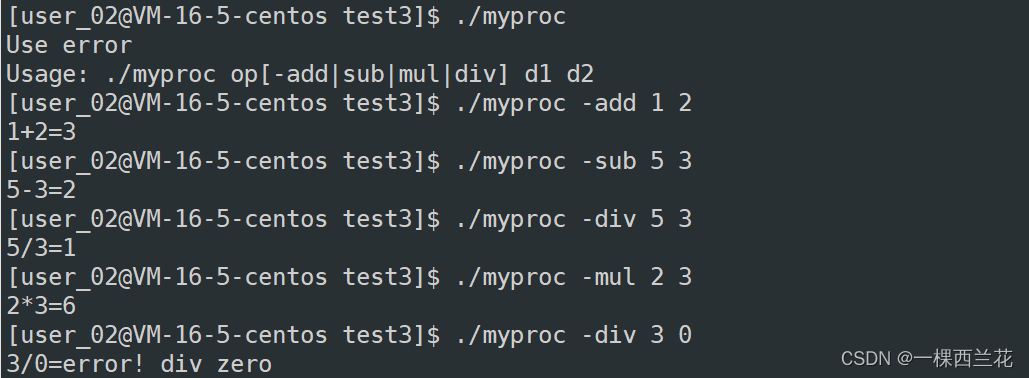

第二步:对照手册

一般芯片的手册对于管脚的使用都会有比较详细的说明和要求

第四列中有明确的说明,对于DEV_CLRn和DEV_OE这个两个管脚,不使用的情况下需要直接接地处理,而对于DATA[5:15]这一组信号,不使用的情况下可以悬空处理。

第四列中有明确的说明,对于DEV_CLRn和DEV_OE这个两个管脚,不使用的情况下需要直接接地处理,而对于DATA[5:15]这一组信号,不使用的情况下可以悬空处理。

经过第二步之后绝大多数的input管脚都有了合适的处理。那么问题来了,总会有那么一些input管脚,纵使找遍了手册每一个角落,厂家也没有给出一个合理的处置建议,那该怎么办呢?

第三步:对照管脚功能做处理

①对于厂家没有给出处置建议的未用Input pin,可以按照管脚的功能来做一些原则上的处理动作:一些时钟输入类功能的管脚,在不使用的情况下最好直接接地处理或者通过一个下拉电阻接地,防止管脚受到干扰影响芯片正常运行;一些使能控制类/硬件配置类的管脚,如果不使用,最好上下拉到一个固定的功能触发电平,让管脚有一个稳定的参考电平输入(当然大多数的芯片内部一般都有默认的上下拉匹配,也可以选择悬空处理,但是如果是比较敏感的信号的话,外部一个强制的上下拉会可靠很多);一些CMOS开关和多路复用器上未使用的引脚,如果不使用,最好固定到直流电位(CMOS开关和多路复用器上未使用的引脚可以接收杂散静电场的信号并将其注入设备,这将降低设备的性能),有时可能需要通过电容在交流端接地;一些具有三态的逻辑输入管脚,如果不使用,可能需要保持不连接(开路条件也被定义为一种逻辑状态:高阻态)。

②特殊的Output pin,例如CLK,最好在输出端并联一个小电容以减少EMI(电容谐振频率一般选择5倍以上CLK频率,将高次谐波旁路到地);例如放大器输出(包括缓冲电压基准的输出)可能在没有电容或偶尔有电阻负载的情况下振荡。这种振荡可能会干扰系统其他部分的工作,必须通过在输出引脚上使用适当的电容或电阻来防止;例如电流输出,未使用的电流输出通常需要一个上拉(或下拉)连接到电源或接地,以防止电路的其他部分的错误操作。

注意事项:

未用引脚的信号端接尽量分开,不要使用同一个电阻端接到地。因为存在触发失误的问题:

总之,必须了解未使用的引脚的功能,并找出该引脚存在的电势,什么电流流入它或者从它流出,它对静电场或者射频干扰的敏感度以及它是否需要容性或者阻性负载。IC的数据手册通常可以帮助你决定如何处理设计中未使用的引脚。

二、未用管脚的特殊考量:低功耗设计

1、将未使用的GPIO 配置为模拟输入模式

GPIO始终有一个输入通道,可以是数字或模拟通道,如果不需要读取GPIO数据,则优先配置为模拟输入

对 I/O 端口进行编程作为模拟输入配置时:

①输出缓冲器被关闭

②施密特触发器输入被禁用,因此I/O引脚的每个模拟值零消耗。施密特触发器的输出被强制为恒定值(0)。

③上拉和下拉电阻被硬件关闭

2、CMOS 器件引脚由N沟道和P沟道场效应管,通常在一个时刻,只有一个管子是开通的,但是,有一个非常短的时间转换期,这两种管子都会部分导通,在一个管子关闭而另一个开启的时候。一个没有端接的输入口可能振荡或在一个中间电平上浮动,导致所有场效应管设备都将在一个微导通的状态,导致了管子的损耗,增加了噪声,并要消耗额外的电源电流。因此,低功耗设计CMOS器件引脚应固定到某一直流电平上。

3、内部上拉或下拉电阻将输入端上拉至正电源或下拉至地。如果未使用的输入端具有这样的一个电阻,则不需要进行连接。然而,如果连接该引脚,则应将它与其电阻一样连接到同一电源,因为任何其它连接都会导致电流流入电阻,带来功耗(该功耗可能相当小,但只要可能就应避免任何浪费)

【题外话:引脚配置–待更新】

在FPGA中,一般将未用管脚软件配置成三态输入(具体原理暂时未了解,懂行的麻烦评论下)

以Altera FPGA为例,一般是将未用的管脚软件设置为三态输入比较安全?(具体原理暂时未了解,懂行的麻烦评论下)

在MCU中,未用GPIO配置为输出低电平可以抗干扰?(具体原理暂时未了解,懂行的麻烦评论下)