verdi+vcs

(1) vlogan/vcs增加编译选项 -debug_access+all -kdb -lca

(2) 在 simulation 选项中加入下面三个选项

-gui=verdi

+UVM_VERDI_TRACE="UVM_AWARE+RAL+HIER+COMPWAVE"

+UVM_TR_RECORD

这里 -gui=verdi是启动verdi 和vcs联合仿真。+UVM_VERDI_TRACE 这里是记录 UVM中 register,component 的波形。+UVM_TR_RECORD记录 transaction的信息。

用verdi调试时虽然可以单步执行,但是task中的局部变量一般都不可读取,造成调试困难。

“Undefined System Task call to '$fsdbDumpfile'”

需要包含verdi的路径:module load verdi

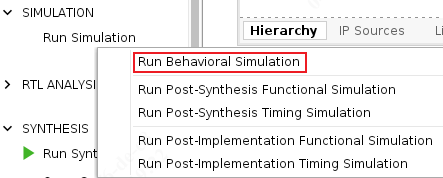

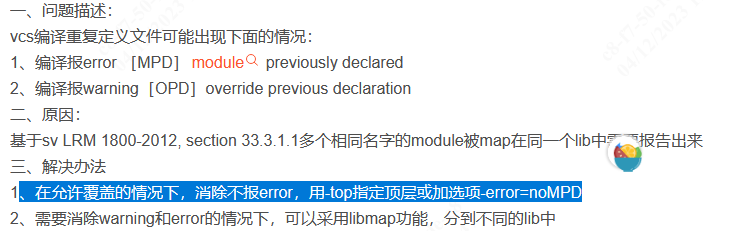

直接点击Run Behavioral Simulation,会编译报错提示文件重复包含,需要对模块重命名,

可是该package文件已经使用·define命令进行单次包含了,为什么还会提示重复冲突呢?

怀疑可能使用的vcs版本有bug,换了一个更高版本的vcs结果是一样的。

最后多次尝试发现,是由于vivado生产的编译脚本是分段编译的,也就是说这个重复冲突的文件在多个vlogan命令里被独立包含了,而又都编译到了同一个lib库中,于是手动修改compile.sh文件,将文件合并编译后该问题解决。

hvp/xlm文件打开

使用verdi -cov

参考:

如何用Verdi查看UVM环境中的变量?_verdi_仿真_debug

Verdi UVM Debug Mode 简单使用-CSDN博客

Synopsys VCS 编译时,启用debug选项-CSDN博客

vcs编译重复定义文件问题_module previously declared-CSDN博客

VCS编译命令 - 知乎

![[oeasy]python0002_终端_CLI_GUI_编程环境_游戏_真实_元宇宙](https://img-blog.csdnimg.cn/img_convert/79e41e0fe5ec211694f8bb3bc9455fbb.png)