题目来源牛客网,完整工程源码:https://github.com/ningbo99128/verilog

目录

1、VL25 输入序列连续的序列检测

题目介绍

思路分析

代码实现

仿真文件

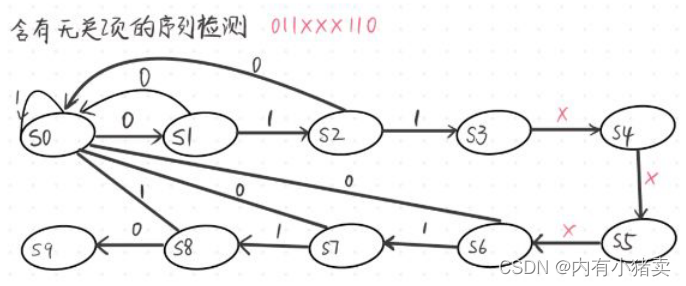

2、VL26 含有无关项的序列检测

题目介绍

思路分析

代码实现

仿真文件

3、VL27 不重叠序列检测

题目介绍

思路分析

代码实现

仿真文件

4、VL28 输入序列不连续的序列检测

题目介绍

思路分析

代码实现

仿真文件

1、VL25 输入序列连续的序列检测

题目介绍

请编写一个序列检测模块,检测输入信号a是否满足01110001序列,当信号满足该序列,给出指示信号match。模块的接口信号图如下:

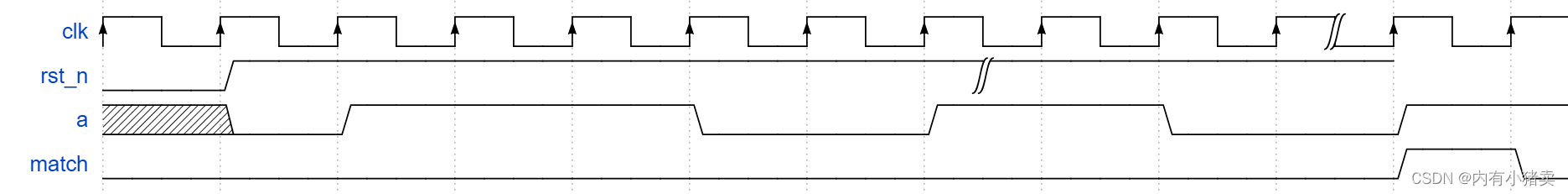

模块的时序图如下:

请使用Verilog HDL实现以上功能,并编写testbench验证模块的功能

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,待检测的数据

输出描述:

match:当输入信号a满足目标序列,该信号为1,其余时刻该信号为0

思路分析

由状态图可以看出,在s5、s6状态为1时,其状态分别为011101、0111001,不满足序列条件,从而跳转到s2状态继续执行检测;其余状态均为跳转到s2状态;最后在s8状态时,满足序列01110001条件,输出信号match为1。

代码实现

//第一段 状态转移

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

curr_state <= s0;

else

curr_state <= next_state;

end

//第二段 转移状况

always @(*)begin

case(curr_state)

s0: begin

if(a==0) next_state = s1;

else next_state = s0;

end

s1: begin

if(a==1) next_state = s2;

else next_state = s0;

end

s2: begin

if(a==1) next_state = s3;

else next_state = s0;

end

s3: begin

if(a==1) next_state = s4;

else next_state = s0;

end

s4: begin

if(a==0) next_state = s5;

else next_state = s0;

end

s5: begin

if(a==0) next_state = s6;

else next_state = s2;

end

s6: begin

if(a==0) next_state = s7;

else next_state = s2;

end

s7: begin

if(a==1) next_state = s8;

else next_state = s0;

end

s8: begin next_state = s0; end

default: begin next_state = s0;end

endcase

end

/********* 第三段 状态输出 moore FSM ************/

//标志信号

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

match <= 1'b0;

else if(curr_state == s8) //注意此处是curr_state

match <= 1'b1;

else

match <= 1'b0;

end 仿真实现

注意match的变化,是在a序列结束后的1个时钟周期,而不是在a序列最后一位刚开始就产生变化。

2、VL26 含有无关项的序列检测

题目介绍

请编写一个序列检测模块,检测输入信号a是否满足011XXX110序列(长度为9位数据,前三位是011,后三位是110,中间三位不做要求),当信号满足该序列,给出指示信号match。

程序的接口信号图如下:

时序图如下:

请使用Verilog HDL实现以上功能,并编写testbench验证模块的功能。 要求代码简洁,功能完整。

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,待检测的数据

输出描述:

match:当输入信号a满足目标序列,该信号为1,其余时刻该信号为0

思路分析

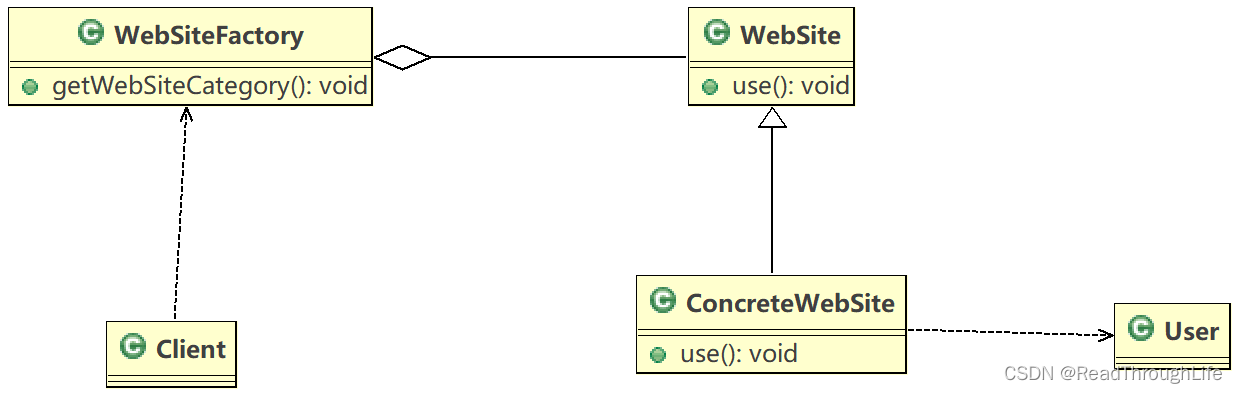

状态转移图如下:

有一个疑惑是,在s6状态时,011xxx后面有2个状态分别为011xxx0、011xxx1;如果是011xxx1那没问题,继续跳转下一个状态,那如果是011xxx0,应该返回哪个状态呢?要不要识别一下x的值,如果前3个x恰好是011,那应该返回到s3状态,而不是s0状态。这样好像把题目想的太复杂了。最后按照最简单的思路来,就好了。

代码实现

//第二段 转移状况

always @(*)begin

case(curr_state)

s0: begin

if(a==0) next_state = s1;

else next_state = s0;

end

s1: begin

if(a==1) next_state = s2;

else next_state = s0;

end

s2: begin

if(a==1) next_state = s3;

else next_state = s0;

end

s3: begin next_state = s4; end

s4: begin next_state = s5; end

s5: begin next_state = s6; end

s6: begin

if(a==1) next_state = s7;

else next_state = s0;

end

s7: begin

if(a==1) next_state = s8;

else next_state = s0;

end

s8: begin

if(a==0) next_state = s9;

else next_state = s0;

end

s9: begin next_state = s0; end

default: begin next_state = s0;end

endcase

end仿真文件

直接运行成功了,就没用vivado仿真。

3、VL27 不重叠序列检测

题目介绍

思路分析

代码实现

仿真文件

4、VL28 输入序列不连续的序列检测

题目介绍

思路分析

代码实现

仿真文件

VL29 信号发生器

VL30 数据串转并电路

VL31 数据累加输出

VL32 非整数倍数据位宽转换24to128

VL33 非整数倍数据位宽转换8to12

VL34 整数倍数据位宽转换8to16

VL35 状态机-非重叠的序列检测

VL36 状态机-重叠的序列检测

VL37 时钟分频(偶数)

VL40 占空比50%的奇数分频

VL41 任意小数分频

VL42 无占空比要去的奇数分频

VL43 根据状态转移写状态机-三段式

VL44 根据状态转移写状态机-二段式