前言

国民技术微控制器内置最多四个高级 12 位 ADC (取决于产品系列) ,具有校准功能,用于提高环境条件 变化时的 ADC 精度。

在涉及模数转换的应用中, ADC 精度会影响整体的系统质量和效率。为了提高此精度,必须了解与 ADC 相关的误差以及影响它们的参数。 ADC 精度不仅取决于 ADC 性能和功能,还取决于 ADC 周围的整体应 用设计。

此应用笔记旨在帮助用户了解 ADC 误差,并解释如何提高 ADC 精度。它分为三个主要部分:

• ADC 内部结构的简述,帮助用户了解 ADC 操作和相关的 ADC 参数

• 解释与 ADC 设计和外部 ADC 参数(例如外部硬件设计)有关的ADC 误差的不同类型和来源

• 关于如何使这些误差最小化的建议,侧重于硬件和软件方法

目录

1 、SAR 型 ADC 简介 1

1.1 SAR ADC 基本原理 1

2 、ADC 误差因素 2

2.1 环境导致的 ADC 精度误差 2

2.1.1 参考电压噪声/误差 2

2.1.2 模拟输入信号噪声 2

2.1.3 模拟信号输入阻抗的影响 3

2.1.4 I/O 引脚串扰 4

2.1.5 模拟信号电压超过范围 4

2.2 软件错误配置 4

2.2.1 时钟配置不合理 4

2.2.2 采样周期参数选择不合理 5

3、 如何获取高精度采样数据 5

3.1 将外部环境对 ADC 精度的误差最小化 5

3.1.1 参考电压噪声/误差最小化 5

3.1.2 模拟输入信号噪声消除 5

3.1.3 模拟信号输入阻抗影响最小化 6

3.1.4 I/O 引脚串扰最小化 6

3.1.5 模拟信号输入电压控制 7

3.2 软件正确配置 7

3.2.1 ADC 时钟配置 7

3.2.2 采样周期匹配 9

3.2.3 采样值平均 10

3.2.4 ADC 上下电和校准 10

3.2.5 通道切换 10

4、 结论 11

N32通用MCU 高精度ADC调试介绍

1 SAR 型 ADC 简介

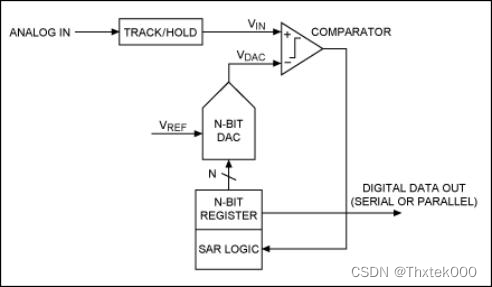

SAR 型 ADC,即逐次逼近型 ADC,采用的是多次比较的方式来获得最终的输出结果分辨率一般为 8 位至20 位,具有低功耗、小尺寸等特点。

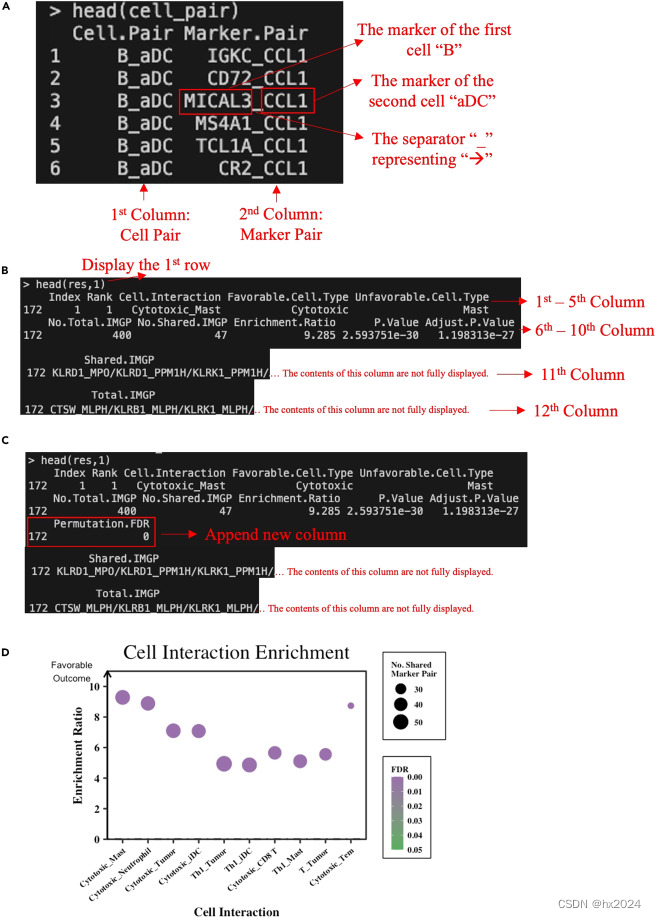

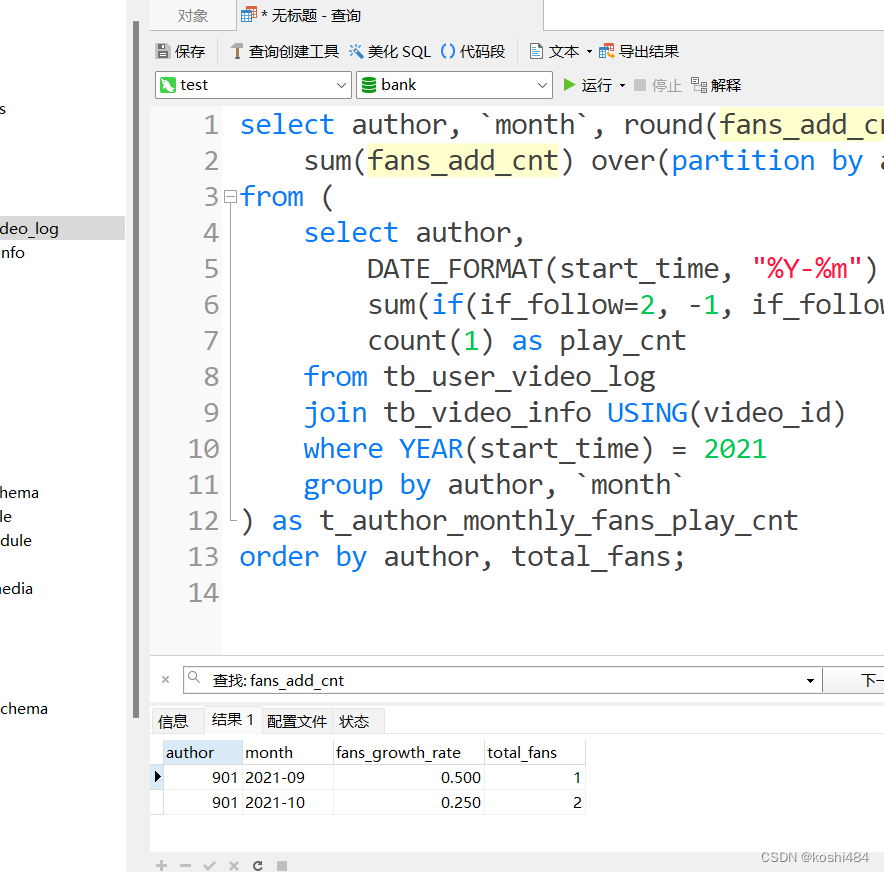

图1.1.1 SAR ADC工作原理模型

国民技术微控制器中内置的ADC使用SAR (逐次逼近) 原则,分多步执行转换。转换步骤数等于ADC转 换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一位。 ADC的内部设计基于切换电容技术。下图是以10位ADC为例的SAR切换电容的数字输出基本原理图。

图1.1.2 SAR ADC设计电路模型

2.1 环境导致的 ADC 精度误差

VDDA 模拟电源作被用作为 ADC 参考电压(VREF+ ),而模拟信号电压采集是以参考电压最为基准, 因此 VDDA 模拟参考上的任何噪声都会导致转换后的数字值变化。硬件设计要求 VDD 与 VDDA 直连,VDD 电源 的质量会影响 ADC 采样精度。

例如, 当参考电压为 3.3V (VDD = VDDA = VREF+ ) ,采集稳定模拟信号 1V ,保证软件配置符合要求, 转换后的结果为:

(1/3.3) × 4095 = 0x04D9

但是, 当 VDD 电源的峰间出现 10mv 的波动时,转换结果为:

(1/3.34) × 4095 = 0x04CA

误差 = 0x4D9 – 0x4CA = 15 LSB

除了可以选择 VDDA 模拟电源作为参考电压, 部分型号也可以选择参考电压为内部 VREF ,内部参考电压 的本身误差也会导致转换后的数字值变化。

例如, 选择内部参考电压为 2.4V (N32G03X 系列) ,采集稳定模拟信号 1V ,保证软件配置符合要求且 参考电压保持稳定, 转换后的结果为:

(1/2.4) × 4095 = 0x06AA

内部参考电压误差在 2%以内,计算最大比例误差, 转换结果为:

(1/2.4) × 4095 × (1-2%) = 0x0688

误差 = 0x06AA - 0x0688 = 34 LSB

电气设备(例如电机、电源线) 会在模拟信号上产生噪声,这些小而高频的信号变化出现在采样时间内, 会导致转换数字值出现较大的误差。

例如, 当参考电压为 3.3V (VDD = VDDA = VREF+ ) ,采集稳定模拟信号 1V ,保证软件配置符合要求, 转换后的结果为:

(1/3.3) × 4095 = 0x04D9

但是, 当模拟信号的峰间出现 10mv 的波动在采样时间内时, 转换结果为:

(1.01/3.3) × 4095 = 0x04E5

误差 = 0x4E5 – 0x4D9 = 12 LSB

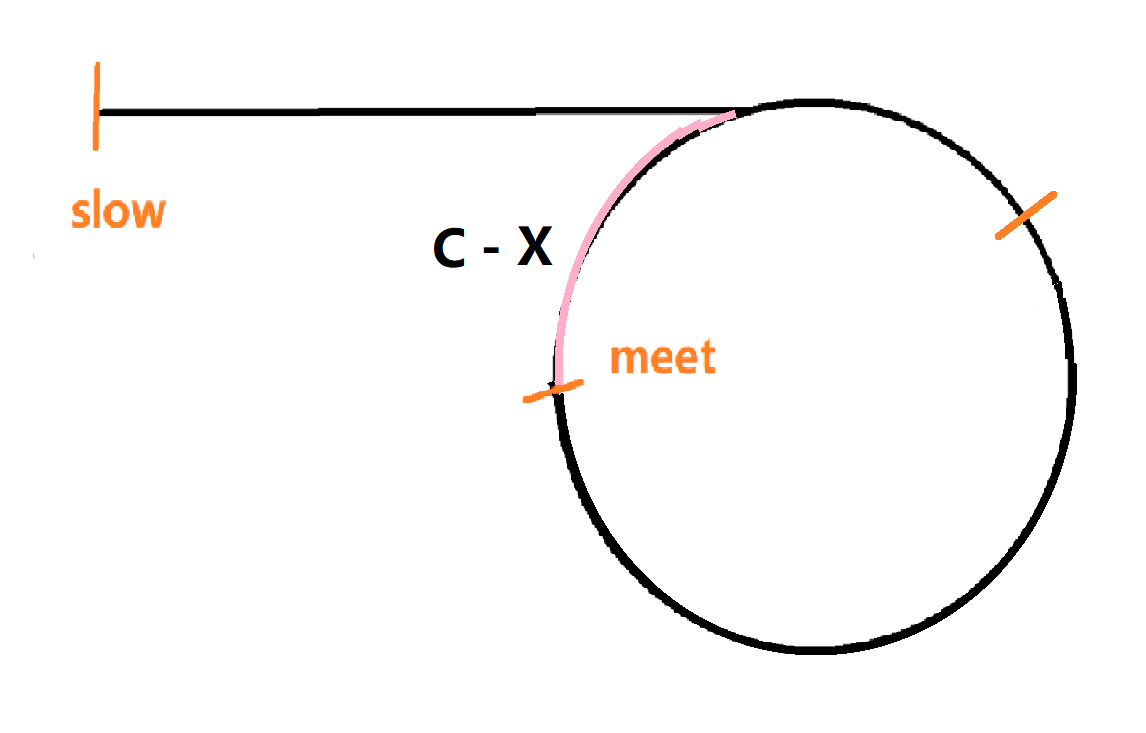

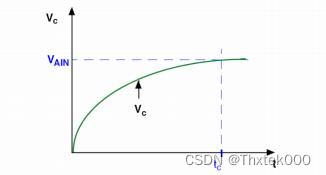

模拟信号和芯片引脚之间的阻抗或串联电阻, 会影响流入引脚的电流而导致采样电压出现变化。模拟信号 是通过电阻为 RADC 的开关控制内部采样电容 (CADC )的充电, 当添加其和芯片引脚之间的阻抗 RAIN 后,保持 电容充电所需时间会延长。

图 2.1.3.1 SAR ADC 采样等效电路模型

采样过程中开关闭合,采样电容上面的电压等效成一个一阶 RC 建立, 建立时间常数 T=(RIN+RADC)*CADC

图 2.1.3.2 SAR ADC 采样精度和信号阻抗模型 表 2.1.3.1 SAR ADC 采样建立时间常数

CADC 的有效充电收 RADC + RAIN 控制,充电时间常量为 tc = (RADC + RAIN ) × CADC 。如果采样时间短于通 过 RADC + RAIN 将 CADC 充满电的时间,则 ADC 转换的数字值会小于实际值。

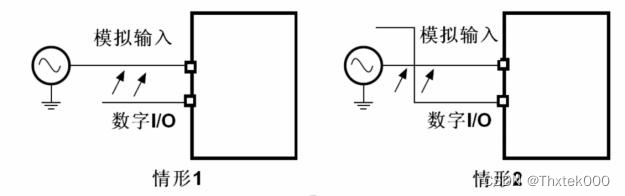

由于 I/O 之间的电容耦合,在切换 I/O 或者相邻数字端口存在高频翻转信号可能会在 ADC 的模拟输入信 号中产生一些噪声。 通常距离很近或交叉的 PCB 走线 I/O 端口也会产生串扰在模拟信号上。

PCB 走线上与模拟输入走线交叉的数字走线可能会影响模拟信号。

PCB 模拟参考地与数字参考地没有隔离也可能会影响模拟信号。

图 2.1.4.1 I/O 串扰的影响效果

模拟 I/O 端口输入低于-0.2V 电压或者高于 VDD 电压,会导致内部模拟输入通道导通,负压情况下会拉低 其他模拟 I/O 的采样数字值,高于 VDD 时,会拉高其他模拟 I/O 的采样数字值。

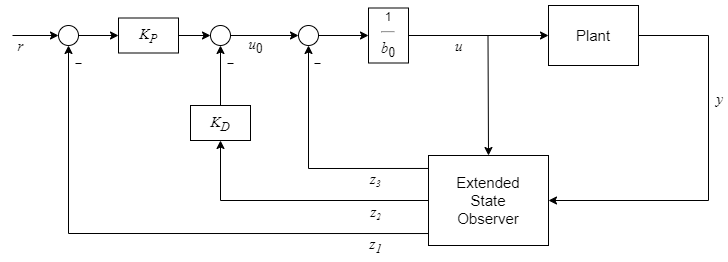

ADC 时钟源分为工作时钟源、 采样时钟源和计时时钟源。

■ 工作时钟为 HCLK,主要用于访问寄存器

■ 采样时钟为 ADC_CLK ,ADC_CLK 有两个源(HCLK 的分频或 PLL 的分频) , HCLK 分频与

系统是同步时钟, PLL 的分频与系统是异步时钟, 用同步时钟的好处是在触发 ADC 响应触发时,没 有不确定性,用 PLL 的分频时钟的好处是可以独立处理 ADC 的工作时钟, 不会影响到挂在 HCLK 的其他模块

■ 计数时钟可以是 HSI 和 HSE ,主要用于内部及时, 在 RCC 配置中,频率大小必须配置成 1MHZ 三个 ADC 时钟在不同系列下,需要根据产品主频和时钟限制做合理配置,任何超出时钟限制或达不大要 求的频率配置, 都会导致转换数字值出现偏差。

ADC 需要根据模拟输入信号的驱动能力来选择软件采样保持时间, 模拟信号和芯片 I/O 之间的阻抗越 大,所需采样时间越长。选择采样时间偏小,高阻抗输入的采集信号不能在采样时间内充满 CADC ,导致转换 的数字值偏小。

3.1 将外部环境对 ADC 精度的误差最小化

☑ VDDA 做参考电压

不推荐 ADC 参考源选择内部参考电压,由于其本身存在的误差无法规避及芯片个体差异性, 无法得出精 度高的采样数据。建议 ADC 参考源选择外部参考电压 VDDA 或 VREF+。

☑ 外部 VREF 噪声屏蔽

为提高转换精度,可以给 ADC 有一个独立的电源供应,它可以被单独滤波和屏蔽以不受 PCB 噪音的干 扰,一个独立的 VDDA 引脚给 ADC 供电, VSSA 引脚提供一个隔离的接地输入。

建议在电源线和地线之间连接具有优良高频特性的电容。也就是说,应在靠近电源的位置安装一个 0.1 µF 和一个 1 µF 的去耦电容,详情可参考数据手册。

☑ 平均方法

平均值滤波可以通过软件方式对模拟输入多次采样,筛掉最大值和最小值, 取剩下结果的均值。当模拟电 压不频繁变化时,此技巧有助于消除模拟输入上的噪声。

通过软件滤波的方式,可以减少输入信号噪声对转换结果的干扰, 但不会消除误差。

☑ 添加外部滤波器

模拟信号输入通道添加外部 RC 滤波器以消除高频噪声, 测量输入信号噪声,选取合适的阻容参数, 截至 频率 fc 刚好高于所涉频率范围的低通滤波器就足以限制噪声和混叠。

添加外部 RC 滤波器虽然可以消除噪声, 但也会对 ADC 的采样速率造成影响,这种情况下, 需加长模拟 信号的采样周期,具体计算可参考第 3.2.2 节的采样时间匹配。

☑ 减小输入阻抗

模拟信号到芯片采样电路端的阻抗越小, CADC 所需时间也会越小, 这种情况下就能实现高速 ADC 采样。 采样稳定的模拟信号,连接通路上不要连接 RC 器件。

☑ 采样时间匹配

模拟信号串联电阻保持电压稳定,则需要匹配合适的采样周期,阻抗越大, 采样周期越长。例如,采样内 部通道电压,通道上的阻抗无法测量,设计仿真其阻抗总体偏大, 选择采样周期则需要更长一点(参考 SDK 中 ADC 温度传感器的采样周期) ,否则转换出来的结果会偏小。

根据输入阻抗匹配采样时间,具体计算可参考第 3.2.2 节的采样时间匹配。

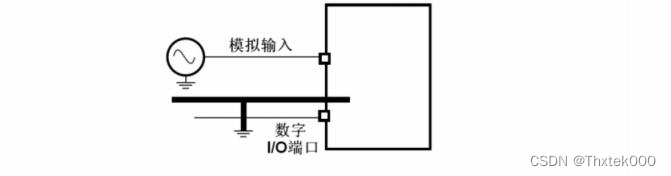

☑ 减少相邻 I/O 干扰

模拟信号输入的相邻 I/O,不能出现高频翻转信号。进行电路设计与 I/O 功能选择时,模拟通道相邻通道 最好不要选择高速通信功能。

☑ PCB 走线优化

模拟信号到 I/O 的 PCB 走线,秉承就近原则, 距离越短, 干扰越小,转换的结果越真实可靠。

若对 ADC 的采样速率要求较高, 需要做对地隔离, 同时在模拟 I/O 与相邻端口铺地隔离。也可以在输入 信号走线下层全层铺地, 例如三层板结构,第一层走模拟信号,第二次铺地,第三层为其他信号走线层。这种 情况能最大程度做到隔离噪声干扰。

图 3.1.4. 1 I/O 减少串扰的影响效果

3.1.5 模拟信号输入电压控制

☑ 输入电压控制-0.2V~VDD

在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加负压(比如-0.33V), 如果施加了此 负电压,会导致正常采样的 ADC 通道电压被拉低,导致读取的数据不准。

在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加高压(大于 VDD 电压) ,如果施加了 此高电压, 会导致正常采样的 ADC 通道电压被拉高,导致读取的数据不准。

3.2 软件正确配置

3.2.1 ADC 时钟配置

ADC 需要三个时钟, 工作时钟、采样时钟和计数时钟,在进行软件配置时, 三个配置都需要进行正确配 置,否则会影响转换的数字值。

☑ 工作时钟

这是访问寄存器的时钟, ADC 外设挂载在 HCLK 总线上, 所以不同系列的 MCU 配置 ADC 工作时钟的软 件操作一样,以库函数操作为例:

N32G45x:

1. RCC_EnableAHBPeriphClk(RCC_AHB_PERIPH_ADC1 | RCC_AHB_PERIPH_ADC2 | RCC_AHB_PERIPH_ADC3 | RCC_A HB_PERIPH_ADC4, ENABLE);

N32G43x/N32L40x/N32L43x:

1. RCC_EnableAHBPeriphClk(RCC_AHB_PERIPH_ADC, ENABLE);

N32G03x:

1. RCC_EnableAHBPeriphClk(RCC_AHB_PERIPH_ADC, ENABLE);

☑ 采样时钟

ADC_CLK 为 ADC 的采样时钟, ADC_CLK 有两个源(HCLK 的分频或 PLL 的分频), HCLK 分频与 系统是同步时钟, PLL 的分频与系统是异步时钟, 用同步时钟的好处是在触发 ADC 响应触发时,没有不确定 性,用 PLL 的分频时钟的好处是可以独立处理 ADC 的工作时钟,不会影响到挂在 HCLK 的其他模块。

N32G45x:该系列工作主频最高为144MHZ,可配置PLL 作为采样时钟源,最高可到72MHz ,支持分频 1,2,4,6,8,10,12,16,32,64,128,256 。可配置 AHB_CLK 作为采样时钟源, 最高可到 72MHz , 支持分频 1,2,4,6,8,10,12,16,32。

以库函数配置为例, 当系统主频大于 72MHZ 时, ADC_CLK 必须至少 2 分频。

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_AHB,RCC_ADCHCLK_DIV2); AHB_CLK 作为采样时钟源

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_PLL,RCC_ADCPLLCLK_DIV2); PLL 作为采样时钟源

N32G43x/N32L43x:该系列工作主频最高为 108MHZ,可配置 PLL 作为采样时钟源, 最高可到 72MHz, 支持分频 1,2,4,6,8,10,12,16,32,64,128,256。可配置 AHB_CLK 作为采样时钟源, 最高可到 72MHz , 支持分频 1,2,4,6,8,10,12,16,32。

以库函数配置为例, 当系统主频大于 72MHZ 时, ADC_CLK 必须至少 2 分频。

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_PLL,RCC_ADCPLLCLK_DIV2); PLL 作为采样时钟源

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_AHB, RCC_ADCHCLK_DIV2); AHB_CLK 作为采样时钟源

N32L40x:该系列工作主频最高为 64MHZ,可配置 PLL 作为采样时钟源, 最高可到 64MHz , 支持分频 1,2,4,6,8,10,12,16,32,64,128,256。可配置 AHB_CLK 作为采样时钟源, 最高可到 64MHz , 支持分频 1,2,4,6,8,10,12,16,32。

以库函数配置为例, 当系统主频最大 64MHZ ,ADC_CLK 最少可以 1 分频。

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_AHB, RCC_ADCHCLK_DIV1); AHB_CLK 作为采样时钟源

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_PLL,RCC_ADCPLLCLK_DIV1); PLL 作为采样时钟源

N32G03x:该系列工作主频最高为 48MHZ,可配置 PLL 作为采样时钟源, 最高可到 18MHz , 支持分频 1,2,4,6,8,10,12,16,32,64,128,256。可配置 AHB_CLK 作为采样时钟源, 最高可到 18MHz , 支持分频 1,2,4,6,8,10,12,16,32。

以库函数配置为例, 当系统主频最大 18MHZ 且为 48MHZ 时, ADC_CLK 最少可以3 分频。

1. ADC_ConfigClk(ADC_CTRL3_CKMOD_AHB, RCC_ADCHCLK_DIV3); AHB_CLK 作为采样时钟源

2. ADC_ConfigClk(ADC_CTRL3_CKMOD_PLL,RCC_ADCPLLCLK_DIV3); PLL 作为采样时钟源

计数时钟

ADC_1MCLK 用于内部计时功能,在 RCC 中配置,频率大小必须配置成 1M。可以选择 HSE 或 HSI 作为 计数时钟源,需根据时钟源的主频, 配置分频比后为 1M 时钟。

以库函数为例, 时钟源默认为 8MHZ ,则软件配置应该为:

1. RCC_ConfigAdc1mClk(RCC_ADC1MCLK_SRC_HSI, RCC_ADC1MCLK_DIV8); HSI 为 8MHZ

1. RCC_ConfigAdc1mClk(RCC_ADC1MCLK_SRC_HSE, RCC_ADC1MCLK_DIV8); HSE 为 8MHZ

进行 ADC 的软件配置过程中, 需要保证三个时钟配置符合用户手册要求, 异常配置会导致出现采样转换 数字值异常情况。

匹配合理的采样周期能提高 ADC 采样精度,使其在 ADC 最高性能下获取精准的采样转换数字值。

☑ 转换速率计算

ADC 使 用若 干 个 ADC_CLK 周 期 对 输 入 电 压 采 样 , 采 样 周期 数 目 可 以 通 过寄存器中更改。 每个通道可以分别用不同的时间采样。总转换时间如下计算:

TCONV = 采样时间+ 量化周期

采样时间可以通过软件配置,量化转换周期是固定值, N32G45x/N32G43x/N32L4xx 系列的量化周期为 12.5 个周期,N32G03x 系列的量化周期为 12 个周期。

不同系列的 ADC 最高采样速率有区别,N32G45x 最高采样速率(采样+量化) 为 5MSPS,

N32G43x/N32L4xx 系列的模拟输入通道分快速和慢速,快速通道最高采样率为 5MSPS ,慢速为 3MSPS ,具体 引脚可参考用户手册。N32G03x 的最高采样速率为 1MSPS。

以 N32G45x 系列举例, 配置 ADC_CLK 为 72MHZ ,软件设置采样周期 1.5 ,根据上面公式计算: ADC 采样速率 = 72 / (1.5 + 12.5) = 5.14 MSPS

☑ 阻抗匹配

为了获取更精准的测量结果, 需要选择合适的采样周期及通道输入阻抗, 其最大RAIN 计算公式为: RAIN <

− RADC 。Ts :软件中配置的采样周期数, 此为数值;fADC :ADC 的采样时钟,可参考章节

3.2.1 ;CADC :5pF (N32G45x/N32G43x/N32L4xx)、 13pF (N32G03x 系列) ,计算时需要换算为 F(法拉)单位; ln(2N+2) :N 表示 ADC 的转换位数为 12;RADC :70Ω(N32G45x 系列)、 200Ω(N32G43x/N32L4xx 快速通 道) 、500Ω(N32G43x/N32L4xx 慢速通道)、 1500Ω (N32G03x 系列) 。用户在进行计算时需要注意单位的 换算。详细参数可参考各系列数据手册。

以 N32G45x 系列举例, ADC 采样时钟为 72MHZ ,外部模拟信号输入阻抗为 1000Ω,为匹配合适的采样 周期应该如何计算:

RAIN < Ts − RADC

72000000×5×10−12 ×ln(212+2)

计算出,TS > 3.7 ,软件配置采样周期需要大于 3.7。

此方法的原理是提高 ADC 精度但降低 ADC 转换速度。如果被测模拟信号产生不稳定的 ADC 值,则可以 通过对一组值进行平均来获得给定输入信号的平均值。通过选择适当数量的待平均样本执行平均。此数量取决 于需要的精度、最低转换速度和其他 ADC 误差水平(如果另一种误差对 ADC 精度有更大影响,则增加平均 值数量不影响总测量精。

3.2.4 ADC 上下电和校准

☑ ADC 上下电

ADC 上电时,用户必须等待 PowerUp 过程完成才可以进入下一步的操作,可以通过查询 RDY 确认 是否上电完成。 ADC 下电时,用户必须等待 PowerDown 过程完成才可以进行下一步操作,可以通过查询 PDRDY 确认是否下电完成。

☑ ADC 校准

每次 ADC 时上电时, 最好执行 ADC 校准动作, 保证准换数字值准确。有的系列 ADC 具有校准自动装载 功能, 可以在下次电前装载第一次的校准值, 减少了 ADC 校准动作。

当模拟参考电压为 VDDA 时, VDD 供电为干电池等消耗性电源,可在每次采样前都进行 ADC 校准。

☑ 第一次采样

软件配置 ADC 时,第一次配置完通道采样周期和转换顺序且未开始触发转换时, CADC 会有一个注入电流 的过程,因此第一顺序的转换通道采样转换时间会大于软件配置时间, 后面的采样时间符合软件配置。

☑ 通道切换

在进行采通道的切换时, CADC 会有一个先放电再充电的过程,因此模拟输入通道上的阻抗越小,放电和 充电的速率就会越快,采样保持所需时间就会越短。同时切换通道也会占用 3 个 ADC 工作时钟。

☑ 模拟引脚悬空

模拟引脚处于悬空状态时,进行采样保持就无法进行一个放电过程,此刻采集到的电压仍是上一通道对 CADC 的充电电压。

此应用笔记描述主要的 ADC 误差, 以及尽可能减少 Nations ADC 误差和获得最佳 ADC 精度的方 法和应用设计原则。

![MYSQL报错 [ERROR] InnoDB: Unable to create temporary file; errno: 0](https://img-blog.csdnimg.cn/direct/2ad2f7b1efd84f4dba3677647dcb9b2f.png)