使用功率MOSFET常见的一些问题(三)

- 1.体二极管

- 2.封装和PCB布局注意事项

- 3.MOS并联

1.体二极管

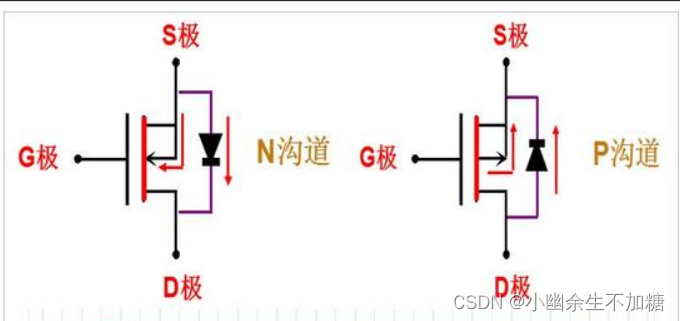

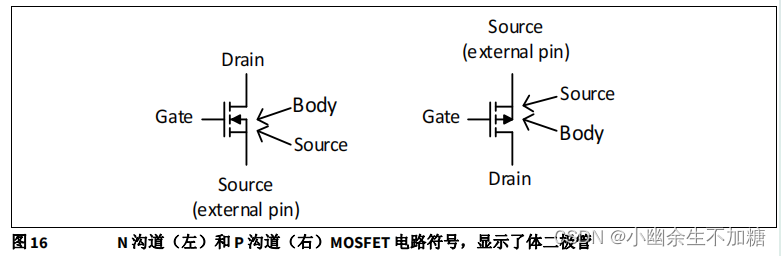

体二极管是 MOSFET 结构中的固有部分,由 p-body 层和 n-epi 层之间的 p-n 结形成,如图所示。功率MOSFET 是三端器件,其本体和源极在内部连接。这可以通过查看 N 沟道和 P 沟道器件的电路符号来理解。

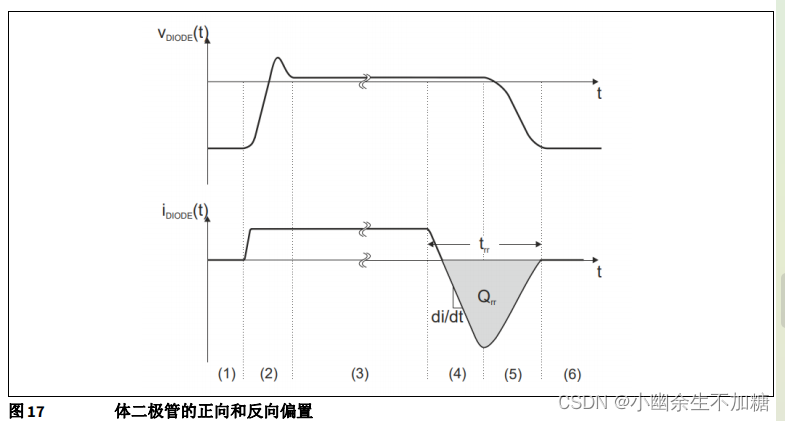

与其他 p-n 结二极管一样,MOSFET 体二极管具有少数载流子反向恢复,因此具有一定的反向恢复时间。当二极管在承载正向电流的同时反向偏置时,就会发生反向恢复现象。

反向恢复在数据表中的特征是时间trr 和在一组指定条件下测试的反向恢复电荷 Qrr。

在区间(1),二极管处于关断状态,并在区间(2)开始导通。在导通过程结束时,二极管变为正向偏置。反向恢复电荷累积并存储,而正向偏置二极管在区间 (3) 期间承载正电流。在关断区间 (4) 开始时,电流减小到零,然后以相反方向流动。在区间 (5) 期间完成反向恢复,在区间 (6) 完成关断过程,此时二极管处于阻塞状态。图中的阴影区域表示 Qrr,这是硬换向稳固性的关键器件参数。

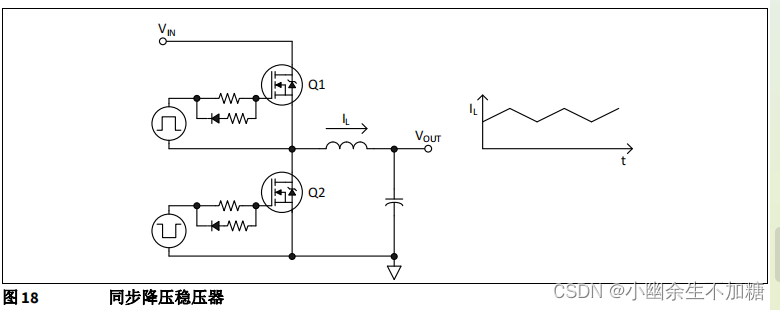

在半桥功率开关电路中,在将高开关电流进入到感应负载时,体二极管反向恢复就变得很重要。考虑一个在连续导通模式 (CCM) 下工作的同步降压稳压器,Q1 导通,Q2 关断,其中电流 IL 从半桥开关节点流出。

当 Q1 关断时,电感电流通过 Q2 体二极管,然后 Q2 在死区时间结束后导通。在 Q2 导通(同步整流)周期结束时,它再次关断,因此电流再次流过其体二极管。在死区时间结束时,Q1 导通,此时 Q2 体二极管恢复变得至关重要。如果 Q1 导通过快,则 Q2 的集成体二极管的峰值反向恢复电流就会上升过快,继而超过峰值反向恢复电流额定值,器件可能会损坏!

通过减缓换向过程中电流的变化率,可以降低体二极管的峰值反向恢复电流。通过减缓栅极驱动的上升速

度,可以控制电流的变化率,使用这种技术,峰值反向恢复电流可以降低到一个可接受的水平,而代价是要延长高功耗开关周期,因此始终需要权衡取舍。

对于在高达 20 kHz 左右频率下操作而言,可以减缓施加的栅极驱动信号以降低“配对”器件体二极管的峰

值反向恢复电流,这是一个很好的实用解决方案。在较高频率下,必须特别注意 MOSFET 开关所需的电压和电流,并选择合适的器件和栅极驱动方案。

2.封装和PCB布局注意事项

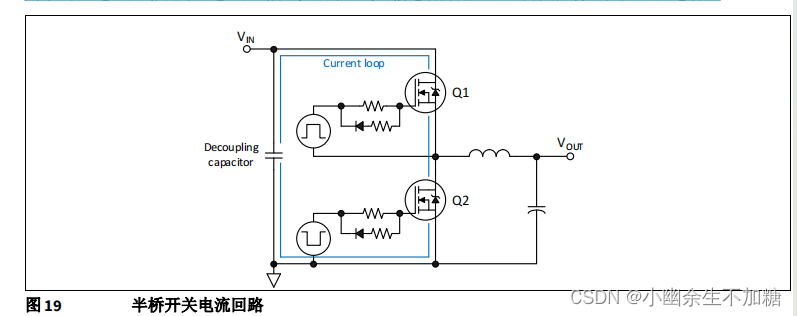

感量取决于漏极和源极连接的内部几何形状。因此,有必要考虑任何设计所需的封装类型,不仅要考虑其

热特性,还要考虑封装电感,而数据手册中可能没有明确说明。简而言之,在硬换向中开关电流高时,SMD 封装的电感要尽可能低,还需要良好的 PCB 布局,以实现可接受的性能,并避免可靠性和潜在的 EMI 问题。在为电源应用设计 PCB 时,建议使用制造商推荐的器件封装,并确保遵循处理和焊接指南 。

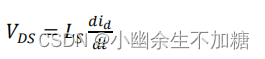

电源开关电路中的杂散电感增加了过压瞬态的振幅和能量,因此有必要降低开关速度以避免雪崩事件。电

压瞬态是由电流的快速变化产生的:

其中 LS 由电流回路确定,电流回路从最近的总线去耦电容开始,通过开关元件,然后返回电容。

在电路板布局中,电流回路的电感取决于形成回路的走线距离,以及 DC 总线去耦电容与 MOSFET 的

距离。较长的走线和较大的回路面积也会产生辐射 EMI。通过将 MOSFET 彼此靠近放置并尽可能靠近 DC 总线去耦电容,可以最大限度地减少回路。这可以通过在 PCB 中使用两层或多层线路,并将返回电流路径直接置于电流路径下方来实现,从去耦电容开始,并通过 MOSFET 以提供紧密耦合。返回路径通常采用电源地平面的形式。

通常在多层 PCB 中保留一个或多个铜层来实现。这里应该提到的是,信号/数字地和电源地应该分开,以避免“地弹”,它会影响敏感的控制电路。

电源和信号地最好单点连接,最好是去耦电容接地连接。

3.MOS并联

我们经常会遇到MOS管并联的设计,也存在很多问题。

对于大电流的电源系统而言,了解和控制并联MOSFET 之间的稳态和动态电流平衡非常重要。当器件在欧姆区工作时,有可能实现稳态电流平衡,因为 RDS(on) 具有正温度系数。可以实现电流平衡,

因为如果一个器件由于其 RDS(on) 低于其并联器件而会传导更多电流,则其管芯温度就会升高,从而提高其RDS(on) 并因此实现电流平衡。

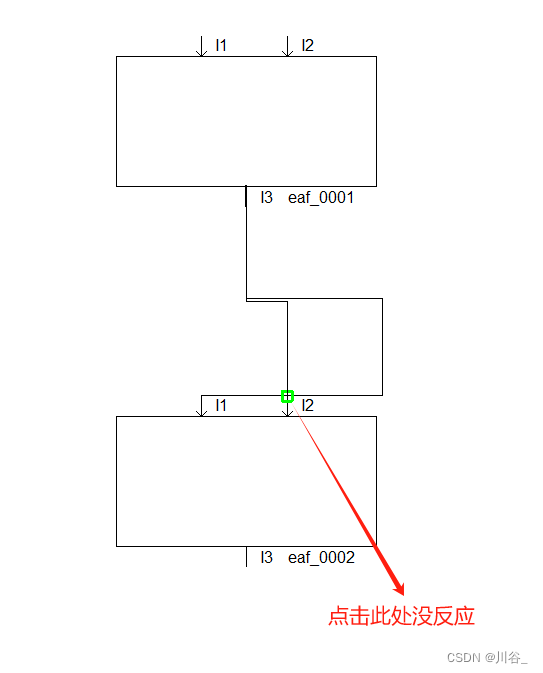

为实现有效地工作,器件应靠近放置,并用相同长度和宽度的走线连接到它们的漏极和源极。

然而,在开关条件下,实现并联会更加困难,随着频率的增加,更是如此。这是因为动态效应在每次导通和关断工作期间都会发挥作用,这可能会使一个器件比其他器件承受更大的压力。以下器件参数的错误匹配会影响开关期间的电流分配和功耗:栅极阈值 (VTH)、跨导 (gfs) 栅源电容 (CGS)、米勒电容 (CGD) 和体二极管恢复 (Qrr),以及 RDS(on)。如果部件匹配不当,一个器件可能会在开关期间承载大部分电流,这可能会超出SOA 限制。

应特别注意功率和热稳定性限制。除此之外,前面描述的热平衡机制需要一些时间才能达到平衡,而当快速开关时,这不可能实现。在并联应用中,应查看数据手册中上述参数的公差,因为更严格的公差控制可以实现更好的动态平衡。

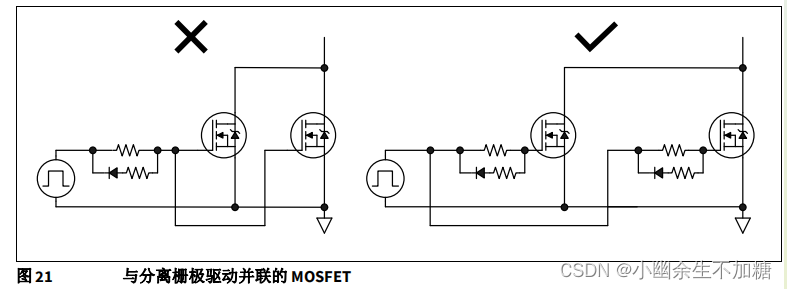

在 PCB 布局中,**栅极回路和电流回路电感需要尽可能保持一致。**电路布局应尽可能保持对称,以保持并联MOSFET 中的电流均衡。并联器件的栅极可以通过放置在栅极连接上的小铁氧体磁珠去耦,或者通过与每个栅极串联的单个电阻去耦,以防止寄生振荡。

栅极驱动电路的设计也很关键。由于当第一个 MOSFET 导通时,并联 MOSFET 不太可能同时导通或关断,因此在源极节点处会出现快速电压摆动。这可以通过较慢并联器件的 CGD 耦合,并在共享栅极连接处产生电压尖峰。这会在 MOSFET 快速导通和关断时产生振荡,可能会损坏 MOSFET 和栅极驱动器。为防止出现这种情况,每个并联 MOSFET 都应有自己的栅极驱动网络,放置在栅极和栅极驱动器的共享连接点之间。