文章目录

- PGA

- 14.1 Introduction简介

- 14.1.1 Features特性

- 14.1.2 Block Diagram结构框图

- 14.2 Linear Output Range线性输出范围

- 14.3 Gain Mode放大模式

- 14.4 External Filtering外部滤波

- 14.7 Enabling and Disabling the PGA Clock时钟使能禁止

- 14.10 Analog Front End Integration模拟前端

- 14.10.1 ADC

- 14.10.1.1 Unfiltered Acquisition Window未滤波采样窗口

- 14.10.1.2 Filtered Acquisition Window滤波采样窗口

- 14.10.2 CMPSS

- 14.10.3 Buffered DAC

- 总结

- 代码配置driverlib

- 代码配置bit-field

PGA

可编程增益放大器(PGA)用于放大输入电压,以增加下游ADC和CMPSS模块的动态范围。

14.1 Introduction简介

集成的PGA有助于降低成本和设计工作量,用于传统上需要外部独立放大器的许多控制应用。片上集成确保PGA与下游ADC和CMPSS模块兼容。软件可选择的增益和滤波器设置使PGA能够适应各种性能需求。

14.1.1 Features特性

PGA模块的可用功能包括:

- 四种可编程增益模式:3倍,6倍,12倍,24倍

- 内部由VDDA和VSSA供电

- 基于硬件的微调以减少偏移和增益误差

- 支持使用PGA_GND引脚的开尔文接地连接

- RC滤波用嵌入式串联电阻器

14.1.2 Block Diagram结构框图

PGA中的有源元件是一个嵌入式运算放大器(op-amp),它被配置为具有内部反馈电阻的非反相放大器。这些内部反馈电阻值被配对以产生软件可选择的电压增益。

器件引脚上有三个PGA信号:

- PGA_IN是PGA运算放大器的正输入。施加到该引脚的信号将被PGA放大。

- PGA_GND是PGA_IN信号的开尔文接地参考。理想情况下,PGA_GND参考等于VSSA,但是PGA可以容忍来自VSSA的小电压偏移。有关更多信息,请参阅设备数据手册。

- PGA_OF支持带RC组件的运算放大器输出滤波。滤波后的信号可用于内部ADC和CMPSS模块的采样和监测。

- PGA_OUT是运算放大器输出端的内部信号。它可用于内部ADC和CMPSS模块的采样和监测。

14.2 Linear Output Range线性输出范围

PGA的绝对输出范围受模拟VDDA和VSSA电源的限制——PGA不能产生大于VDDA或小于VSSA的输出电压。

尽管PGA可以在VSSA到VDDA的绝对电压范围内产生满量程输出,但放大器输出仅在绝对范围的子集内是线性的。这个减小的范围被称为线性输出范围。

设备数据手册中的PGA性能规范仅适用于线性输出范围。为了获得最佳性能,输入信号的调节方式应使PGA在正常系统操作期间保持在线性输出范围内。

但每个线性放大区域会随着PGA增益的改变而改变,因而需要查阅芯片手册以获得PGA的最佳性能。

14.3 Gain Mode放大模式

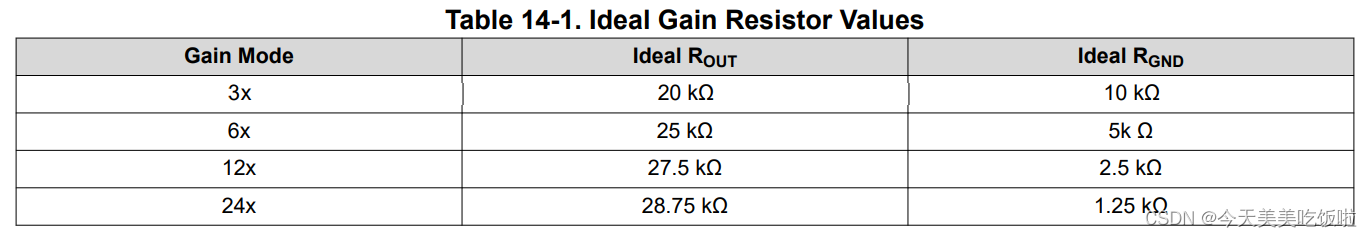

3x、6x、12x和24x的增益模式可使用PGACTL[Gain]寄存器字段进行软件选择。PGA的增益由电阻器ROUT和RGND之间的预设比率确定:

G

a

i

n

=

1

+

R

o

u

t

R

G

N

D

Gain=1+\frac{R_{out}}{R_{GND}}

Gain=1+RGNDRout

允许在正常操作期间改变增益模式,但在这样做时可以观察到最小调节时间以进入稳定状态。有关增益开关稳定时间,请参阅设备数据手册。

14.4 External Filtering外部滤波

PGA输出可以通过嵌入式串联电阻器路由到引脚,以对放大信号进行低通滤波。滤波器电阻可使用PGACTL[FILTRRESSEL]寄存器字段进行软件选择。默认选择PGACTL[FILTRESEL]=0将禁用过滤器路径。

可以使用标准低通RC方程来估计截止频率:

f

=

1

2

π

R

C

{f=\frac{1}{2\pi RC}}

f=2πRC1

14.7 Enabling and Disabling the PGA Clock时钟使能禁止

如果在PGA输出电压时禁用PGA的时钟,则输出电压不受影响,但PGA寄存器将不再通过寄存器写入进行更新。启用时钟将恢复寄存器写入。

14.10 Analog Front End Integration模拟前端

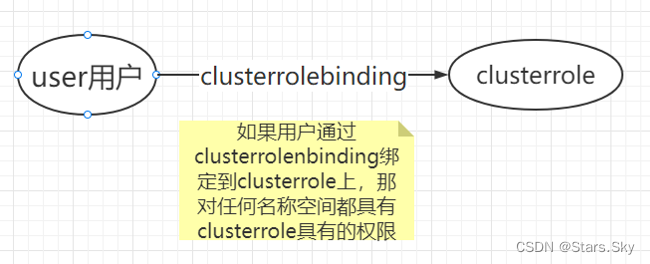

PGA与其他嵌入式模拟模块(ADC、CMPSS、缓冲DAC)一起作为模拟前端系统运行。

14.10.1 ADC

在最简单的应用中,PGA放大小的输入信号以增加ADC的动态范围。PGA还提供了缓冲来自ADC采样和保持电容器的输入信号的额外好处,这进一步减少了采样误差。

滤波和未滤波PGA输出路径均可用于ADC采样。采样PGA路径时,建议使用最小ADC采集窗口。

14.10.1.1 Unfiltered Acquisition Window未滤波采样窗口

设备数据手册提供了用一个ADC采样PGA_OUT信号的最小估计ADC采集窗口。该估计值应提供接近ADC的指定性能参数的采样精度。为了获得更好的性能,可以使用更长的采集窗口。

14.10.1.2 Filtered Acquisition Window滤波采样窗口

用一个ADC采样PGA_OF滤波信号的最小ADC采集窗口根据RFILTER和CFILTER的值而变化。为了确保良好的性能,请选择足够大的CFILTER电容器,以满足大多数ADC采样和保持电容器(Ch)充电要求。CFILTER值可以根据ADC采样误差的可接受量(LSBErr)来确定大小:

C

F

I

L

T

E

R

=

C

h

×

4096

/

L

S

B

E

r

r

C_{FILTER}=C_{h}\times 4096 / LSB_{Err}

CFILTER=Ch×4096/LSBErr

14.10.2 CMPSS

对于高于或低于参考电压的跳闸,可通过CMPSS模块监测PGA输出。每个CMPSS最多可使用两个独立的参考阈值进行跳闸检测。

滤波和未滤波PGA输出路径均可用于CMPSS跳闸监测。

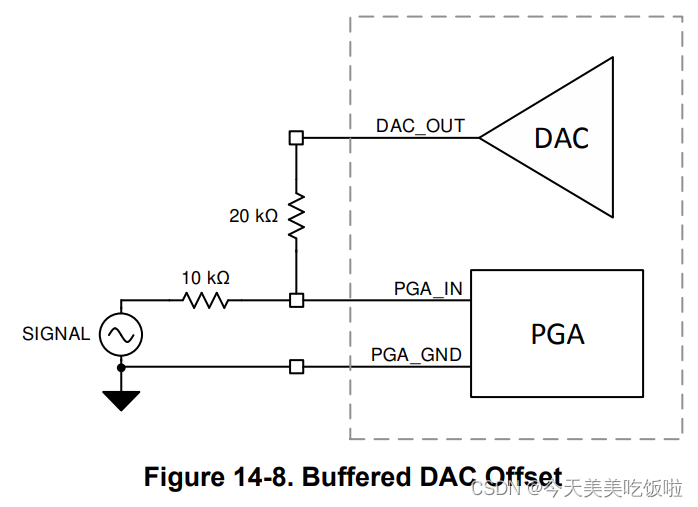

14.10.3 Buffered DAC

作为最佳实践,调节PGA输入信号,使得PGA输出在线性范围内居中。输入信号需要偏移和衰减的某种组合来实现这一目标。

例如,外部电阻分压器可以衰减输入信号,而嵌入式缓冲DAC可以提供正电压偏移

总结

PGA模块可以作为ADC、CMPSS与外部模拟信号之间的桥梁。当外部模拟信号幅值过小,PGA可以将放大后甚至滤波后再经由ADC,CMPSS信号处理。

代码配置driverlib

#define myPGA0_BASE PGA1_BASE

void myPGA0_init()

{

PGA_setGain(myPGA0_BASE, PGA_GAIN_3);

PGA_setFilterResistor(myPGA0_BASE, PGA_LOW_PASS_FILTER_RESISTOR_200_OHM);

PGA_enable(myPGA0_BASE);

//

// Delay for PGA to power up.

//

DEVICE_DELAY_US(500);

}

代码配置bit-field

void myPGA1_init()

{

// configure PGA gain mode

Pga1Regs.PGACTL.bit.GAIN = 0;

// configure PGA filter resistor

Pga1Regs.PGACTL.bit.FILTRESSEL = 1;

// enable PGA module

Pga1Regs.PGACTL.bit.PGAEN = 1;

// wait PGA to power up

DELAY_US(500);

}