文章目录

- 前言

- 一、简介

- 二、enclave相互作用与保护

- 三、enclave生命周期

- 四、数据结构和enclave操作

- 五、enclave page cache

- 六、enclave instructions and intel sgx

- 参考资料

前言

最近开始研究Intel SGX硬件特性,记录下研究过程。

目前安全性主要关注对存储中的静止数据或在网络上传输的数据进行加密,但却没有保护数据在使用过程中的安全。Intel SGX利用CPU平台的优势,并建立在安全基础之上,保护数据和应用程序在使用过程中的安全性。

传统的安全方法通常只关注数据的静态存储和传输,但在数据使用的过程中,例如在计算机的内存中进行处理,数据很容易受到恶意软件、攻击者或系统特权用户的威胁。在这种情况下,即使数据在存储或传输时受到加密保护,一旦数据在使用过程中解密,它就变得容易受到攻击。

Intel SGX通过利用CPU的硬件特性和安全功能,提供了一种解决方案来保护数据和应用程序在使用过程中的安全性。它通过创建受保护的执行环境(enclave),将敏感数据和应用程序隔离在一个受信任的环境中。这些受保护的区域在处理器内部创建,可以保护数据免受恶意软件、攻击和特权用户的访问。

在Intel SGX的保护下,数据和应用程序在使用过程中得到了保护,即使在主机系统被攻陷或存在恶意软件的情况下,也可以确保数据的安全性。这种新的安全方法填补了数据在使用过程中的保护空白,为敏感数据和应用程序提供了强大的安全性保障。

一、简介

Intel® Software Guard Extensions (Intel® SGX) 是添加到 Intel® 架构处理器中的一组指令和机制,用于内存访问。Intel SGX硬件使用户空间应用程序能够保留私有的代码和数据内存区域。

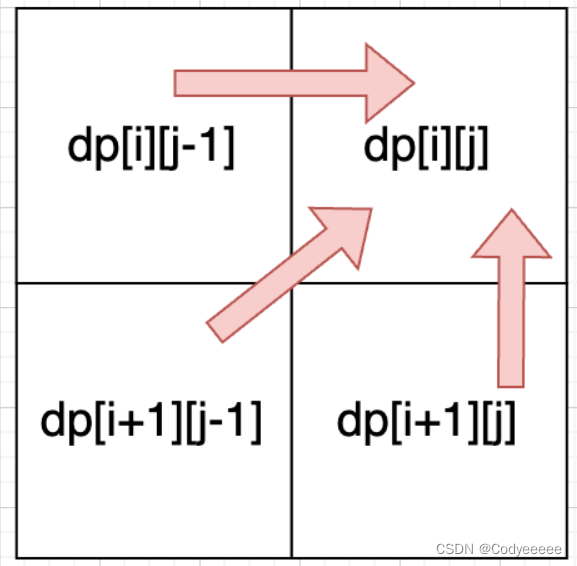

如下图所示:

Intel SGX 的关键功能和优势:

(1)提升机密性和完整性:Intel SGX 可以在操作系统、BIOS、虚拟机监视器(VMM)或系统管理模式(SMM)等层面存在特权恶意软件的情况下保护敏感数据。它确保在受保护的隔离区域内的数据保持机密性和完整性。

(2)部署选择性:使用 Intel SGX,可以灵活选择部署应用程序的方式。可以使用带有 SGX 库操作系统的现有应用程序,也可以使用提供的软件开发工具包(SDK)开发定制的应用程序。这种选择性使您能够根据特定需求定制解决方案。

(3)远程认证和配置:Intel SGX 支持远程认证,允许依赖方验证应用程序隔离区域的身份和完整性。此功能增强了隔离区域内配置密钥、凭证和其他敏感数据的安全性,为远程方提供了保障。

(4)减少攻击面:通过绕过操作系统和虚拟机层,运行在 Intel SGX 隔离区域内的应用程序可以直接与 CPU 进行通信。这样可以减少攻击面,并减轻系统更高层面的漏洞所带来的风险。

Intel SGX 提供了一个可信的执行环境,保护敏感数据,并使其能够在保护的隔离区域内进行安全协作。它提供机密性、完整性、部署灵活性、远程认证和减少攻击面等功能,使其成为保护数据隐私的有价值的技术。

Intel SGX 可以包含两个指令扩展集合,分别称为 SGX1 和 SGX2。

SGX1 扩展允许应用程序实例化一个受保护的容器,称为飞地(enclave)。飞地是一个可信的内存区域,其中应用程序功能的关键部分具有硬件增强的机密性和完整性保护。还引入了新的访问控制来限制对不驻留在飞地中的软件的访问。

SGX2 扩展允许在飞地内对飞地资源和线程执行进行更灵活的运行时管理。

"enclave"在计算机安全领域中指的是一种受保护的内存区域,它具有独立的安全性和隔离性。为了保持准确性,"enclave"在这里应该保留为英文术语。

我后续还是把enclave翻译为飞地。

二、enclave相互作用与保护

Intel SGX 允许应用程序的受保护部分在明文中进行分发。在构建飞地之前,飞地的代码和数据是可以自由检查和分析的。受保护部分被加载到飞地中,其中的代码和数据会被测量。一旦应用程序的受保护代码和数据加载到飞地中,内存访问控制会限制外部软件的访问。飞地可以向远程方证明其身份,并提供安全提供密钥和凭证所需的基本构件。应用程序还可以请求一个特定于飞地和特定于平台的密钥,用于保护希望存储在飞地外部的密钥和数据。

受保护部分的分发:Intel SGX允许应用程序的受保护部分在明文中进行分发,这意味着飞地的代码和数据可以在没有加密或混淆的情况下共享和分发。这使得飞地的分发和部署变得更加容易。

飞地的构建和检查:在构建飞地之前,飞地的代码和数据是公开的,可以进行检查和分析。这种透明性允许进行安全审计,验证飞地的功能和安全性。

测量和内存访问控制:一旦应用程序的受保护代码和数据加载到飞地中,它们将进行测量过程。这个测量过程确保了飞地内代码和数据的完整性。在建立飞地之后,将强制执行内存访问控制,以限制外部软件对飞地的访问。这种隔离性有助于保护飞地内容的机密性和完整性。

身份和安全提供:飞地具有向远程方证明其身份的能力。这使得安全通信成为可能,并在飞地与外部实体之间建立信任。飞地可以提供安全密钥和凭证的必要构建模块,增强系统的整体安全性。

飞地特定密钥:在飞地内运行的应用程序可以请求一个特定于飞地和特定于平台的密钥。这个密钥可以用于保护敏感信息,例如应用程序希望在飞地外部存储的密钥和数据。这个特性为需要在飞地安全内存之外持久保存的数据提供了额外的安全层。

Intel SGX引入了两个对于Intel架构来说非常重要的功能。第一个是飞地内存访问语义的改变( the change in enclave memory

access semantics)。第二个是对应用程序地址映射的保护(protection of the address mappings of the application)。

(1)飞地内存访问语义:Intel SGX在飞地内引入了新的内存访问语义。在飞地内部进行的内存访问是受到保护且与外部软件隔离的,提供了增强的机密性和完整性。飞地内存访问语义确保敏感数据和代码在飞地内部得到安全访问和处理,防止未经授权的访问或篡改。

(2)保护地址映射:Intel SGX还对应用程序的地址映射提供了保护。地址映射将应用程序使用的虚拟地址与物理内存位置关联起来。通过保护地址映射,Intel SGX防止恶意攻击试图篡改或操纵内存映射,确保飞地内存的完整性和安全性。

三、enclave生命周期

飞地内存管理分为两个部分:地址空间分配和内存提交。

(1)地址空间分配:地址空间分配指定了飞地可以使用的线性地址范围,这个范围被称为ELRANGE(Enclave Range)。在这个区域内,实际的资源并没有被分配。地址空间分配为飞地提供了可用的虚拟地址范围。

(2)内存提交:内存提交是将实际的内存资源(作为页面)分配给已分配的地址空间的过程。这个两阶段的技术允许飞地灵活控制其内存使用,并在飞地需求较低时动态调整,避免过度使用内存资源。内存提交将物理页面添加到飞地中,使得飞地可以使用这些页面存储数据或代码。操作系统可能会支持单独的分配和提交操作,以提供更灵活的内存管理控制。

通过地址空间分配和内存提交的机制,飞地可以根据需要动态地管理其内存使用情况。它可以根据实际需求调整内存资源的分配,避免浪费和过度使用,提高内存的利用效率。这种灵活性使得飞地能够适应不同的内存需求,并在资源有限的环境中有效地管理内存。

在创建飞地时,飞地的代码和数据是从明文源(非飞地内存)加载的。

飞地的代码和数据通常存储在非飞地内存中,例如主机内存或磁盘上的文件。在创建飞地时,这些代码和数据会从非飞地内存加载到飞地中。

加载过程包括将代码和数据从非飞地内存复制到飞地的内存空间中。这些代码和数据在加载过程中可能会经过验证和测量,以确保其完整性和安全性。

一旦代码和数据被成功加载到飞地内存中,飞地就可以在受保护的环境中执行这些代码和访问这些数据。通过将代码和数据加载到飞地中,可以实现对敏感信息的保护,防止未经授权的访问和篡改。

需要注意的是,加载过程中的明文源是指非飞地内存,因此在加载过程中需要采取适当的安全措施,以防止潜在的安全漏洞和攻击。

在通常情况下,不受信任的应用程序代码通过使用Intel SGX提供的EENTER叶子函数来启动一个已初始化的飞地。这将控制转移到位于受保护的飞地页面缓存(EPC)中的飞地代码上。飞地代码通过EEXIT叶子函数返回给调用者。在进入飞地时,硬件将控制权转移到飞地内部的软件。飞地内部的软件将堆栈指针切换到飞地内部的一个堆栈上。当从飞地返回时,软件会切换回原始的堆栈指针,然后执行EEXIT叶子函数。

具体流程如下:

不受信任的应用程序代码调用EENTER叶子函数,将控制权传递给飞地内的代码。

硬件将控制转移到飞地内部的软件。

飞地内的软件将堆栈指针切换到飞地内的堆栈上,使得执行过程在飞地内进行。

在飞地内部执行相应的代码和操作。

当需要从飞地返回时,软件将堆栈指针切换回原始的堆栈,然后执行EEXIT叶子函数。

EEXIT叶子函数将控制权返回给调用者,不受信任的应用程序代码继续执行。

通过使用EENTER和EEXIT叶子函数,控制权可以在不受信任的应用程序代码和受保护的飞地代码之间进行安全的转移。这样可以确保飞地内的代码在受保护的环境中执行,并且与不受信任的应用程序代码之间存在明确的边界。这有助于保护飞地内的敏感数据和功能免受不受信任应用程序代码的恶意访问和篡改。

在支持SGX2扩展的处理器上,飞地编写者可以使用SGX2指令集在飞地构建和运行后向飞地添加内存。这些指令允许向飞地添加额外的内存资源,用于堆等区域的使用。此外,SGX2指令还允许飞地添加新的线程。SGX2特性为软件模型提供了额外的能力,而不会改变Intel SGX架构的安全属性。

通过SGX2指令,飞地可以动态地增加内存和线程,以满足运行时的需求。这为飞地内的应用程序提供了更大的灵活性和扩展性。例如,当飞地需要更多的内存来处理大量数据或动态分配内存时,可以使用SGX2指令来向飞地添加额外的内存资源。同样地,当飞地需要并行执行任务时,可以使用SGX2指令来添加新的线程。

值得注意的是,SGX2特性提供了额外的功能,但不会改变Intel SGX架构的安全属性。飞地的安全性仍然由SGX的安全保护机制和硬件隔离提供。通过在运行时动态添加内存和线程,飞地可以更好地适应动态需求,同时保持飞地内数据和代码的安全性和隔离性。

从飞地中调用外部过程通常可以使用EEXIT叶子函数,并在受信任部分和不受信任部分之间建立软件约定。

以下是该过程的一般概述:

飞地内的受信任部分准备需要传递给外部过程的参数和数据。

受信任部分调用EEXIT叶子函数,将控制权转移到飞地外的不受信任部分。

不受信任部分位于飞地外的不受信任环境中(如操作系统或应用程序代码),从EEXIT函数接收控制权。

不受信任部分使用传递的参数和数据执行外部过程。

外部过程完成后,不受信任部分可能需要处理返回值或结果。

控制权然后转移回飞地内的受信任部分,通常使用受信任部分和不受信任部分之间约定的软件方式

这个软件约定定义了受信任部分和不受信任部分之间的通信方式、数据交换和控制流管理。它确保了在保持Intel SGX提供的隔离和安全保证的同时,受信任部分可以安全地调用外部过程并在飞地内部接收结果。

需要仔细设计和实现这个约定,以确保飞地数据和代码的完整性和安全性。可能需要适当的参数验证、数据编组和安全通信机制来建立一个稳健的受信任-不受信任接口。

一个活动的飞地会消耗Enclave Page Cache(EPC)中的资源(参见5节)。Intel SGX提供了EREMOVE指令,飞地管理器可以使用该指令来回收分配给飞地的EPC页面。当飞地被拆除时,飞地管理器会对每个飞地页面使用EREMOVE。

EREMOVE指令的成功执行将使该EPC页面可供分配给其他飞地使用。通过使用EREMOVE,可以有效地管理EPC资源的分配和回收,确保资源的高效利用。

当飞地不再需要某个页面时,飞地管理器可以使用EREMOVE指令来释放该页面,以便将其分配给其他需要的飞地。这样可以最大程度地提高EPC资源的利用率,并避免资源浪费。

需要注意的是,EREMOVE指令的使用需要谨慎,确保只在适当的时机和情况下使用,以避免对活动中的飞地造成不必要的影响。对于正在运行的飞地,应在确保其安全性和正确性的前提下进行资源回收操作。

四、数据结构和enclave操作

在运行一个保护区域(enclave)时,有两个主要的数据结构与之相关:SGX保护区域控制结构(SGX Enclave Control Structure,简称SECS)和线程控制结构(Thread Control Structure,简称TCS)。

每个保护区域都有一个对应的SECS,其中包含关于保护区域的元数据,这些元数据由硬件使用,无法直接被软件访问。SECS中包含一个字段用于存储保护区域的构建测量值(build measurement value)。这个字段名为MRENCLAVE,由ECREATE指令初始化,并在每次EADD和EEXTEND指令执行后更新。它在EINIT指令执行后被锁定。

每个保护区域包含一个或多个TCS结构。TCS包含由硬件使用的元数据,用于在进入/退出保护区域时保存和恢复线程特定信息。TCS中有一个字段名为FLAGS,可以被软件访问。这个字段只能被调试保护区域访问。标志位DBGOPTIN允许单步调试与TCS相关联的线程。

SECS在执行ECREATE指令时创建。TCS可以使用EADD指令或SGX2指令创建。

详细信息可以参考Intel v3 文档的第34.7节(SECS)和第34.8节(TCS)。

五、enclave page cache

(1)

保护区域页面缓存(Enclave Page Cache,EPC)是用于存储正在执行的保护区域的页面的安全存储空间。对于一个EPC页面,硬件执行额外的访问控制检查,限制对该页面的访问。在执行当前页面的访问检查和地址转换之后,硬件会检查当前执行的程序是否可以访问EPC页面。通常情况下,只有保护区域的所有者或正在设置EPC页面的指令才能访问EPC页面。

EPC提供了一个受硬件保护的内存区域,用于存储保护区域的代码和数据。这些页面不受普通内存管理机制的影响,因此对于未经授权的程序或操作系统来说是不可见的。硬件会执行额外的访问控制检查,确保只有拥有相应访问权限的程序才能访问EPC页面。

由于EPC页面是受保护的,通常只有保护区域的所有者可以访问和操作这些页面。其他程序或操作系统无法直接读取或写入EPC页面。只有在设置EPC页面的过程中,其他指令可能会访问EPC页面。

EPC(Enclave Page Cache)被划分为多个EPC页面。每个EPC页面的大小为4KB,且始终按4KB边界对齐。

这意味着EPC页面在EPC内存中占据连续的4KB空间,并且始终从4KB的倍数位置开始。对于每个EPC页面,硬件会分配4KB的存储空间,并确保它们之间没有重叠。这种页面对齐和大小的限制是硬件所要求的,以便有效地管理和访问EPC内存。

EPC(Enclave Page Cache)中的页面可以是有效的(valid)或无效的(invalid)。每个有效页面都属于一个保护区域实例。每个保护区域实例都有一个EPC页面,用于保存其SECS(SGX Enclave Control Structure)。每个EPC页面的安全元数据存储在一个名为Enclave Page Cache Map(EPCM)的内部微架构结构中。

EPC(Enclave Page Cache)由特权软件进行管理。Intel SGX提供了一组指令,用于向EPC添加和移除内容。在启动时,BIOS可以配置EPC。在EPC内存是系统DRAM的实现中,EPC的内容受到加密引擎的保护。

特权软件负责管理EPC的分配、回收和访问控制。通过使用指定的SGX指令,特权软件可以将保护区域的代码和数据加载到EPC中,并在不再需要时将其从EPC中移除。这些指令允许特权软件有效地管理EPC内存,并确保保护区域的安全性和隔离性。

在系统启动时,BIOS可以配置EPC的大小和位置。这意味着BIOS可以决定将多少系统内存用作EPC,并将其分配给SGX使用。这样可以为保护区域提供足够的安全内存空间。

(2)

EPCM(Enclave Page Cache Map)是处理器使用的安全结构,用于跟踪EPC(Enclave Page Cache)的内容。EPCM准确地持有每个当前加载到EPC中的页面的一个条目。EPCM对软件不可访问,并且EPCM字段的布局是实现特定的。

EPC是Intel SGX(Software Guard Extensions)中的一个关键组件,它是用于存储受保护的隔离区域(enclave)页面的内存区域。EPC在物理内存中保护了这些页面,并提供了保密性和完整性的保护。

为了跟踪EPC中的页面,处理器使用EPCM进行管理。每个加载到EPC的页面在EPCM中都有一个对应的条目。EPCM记录了页面的状态、访问权限和其他相关信息。通过EPCM,处理器可以有效地管理EPC中的页面,并确保页面的安全性。

需要注意的是,EPCM是处理器内部的数据结构,对软件是不可见的。软件无法直接访问或操纵EPCM。EPCM的布局和字段的具体含义是由具体的实现所确定的,因此可能会因处理器型号和实现而有所不同。

然而,EPCM包含以下结构信息:

• 相对于有效性和可访问性,EPC页面的状态。

• 页所属的保护区域的SECS标识符(参考Table 34-29)。

• 页面的类型:常规页、SECS页、TCS页或VA页。

• 保护区域被允许通过的线性地址来访问该页面。

• 在该页面上指定的读取/写入/执行权限。

EPCM结构在处理器的地址转换流程中用于对EPC页面进行访问控制。

EPCM结构的描述在表格34-29中,访问控制流程的概念性描述在intel vol3第34.5节中。

EPCM条目由处理器作为各种指令流的一部分进行管理。

六、enclave instructions and intel sgx

在Intel SGX中,可用的保护区域指令被组织为三个指令助记符下的叶子函数:ENCLS(特权级0)、ENCLU(特权级3)和ENCLV(VT根模式)。每个叶子函数使用EAX寄存器来指定叶子函数索引,并可能需要额外的隐式输入寄存器作为参数。ENCLS、ENCLU和ENCLV指令隐式地使用EAX,因此不使用ModR/M字节编码。对于ENCLS、ENCLU和ENCLV指令,不使用ModR/M编码,并且使用额外寄存器的使用由各自的叶子函数索引隐含地表示。

每个叶子函数索引也与一个唯一的叶子函数助记符相关联。Intel SGX指令的长格式表达形式采用ENCLx[LEAF_MNEMONIC]的形式,其中’x’可以是’S’、‘U’或’V’。长格式表达式清晰地表明了给定“叶子助记符”所需的特权级别要求。为简单起见,在本文档中,将仅使用唯一的“Leaf_Mnemonic”名称(省略ENCLx)。

表格提供了Intel SGX初始实现(引入于第6代Intel Core处理器)中可用的指令叶子的摘要。

Supervisor and User Mode Enclave Instruction Leaf Functions in Long-Form of SGX1:

| Supervisor Instruction | Description | User Instruction | Description |

|---|---|---|---|

| ENCLS[EADD] | Add an EPC page to an enclave. | ENCLU[EENTER] | Enter an enclave. |

| ENCLS[EBLOCK] | Block an EPC page. | ENCLU[EEXIT] | Exit an enclave. |

| ENCLS[ECREATE] | Create an enclave. | ENCLU[EGETKEY] | Create a cryptographic key. |

| ENCLS[EDBGRD] | Read data from a debug enclave by debugger. | ENCLU[EREPORT] | Create a cryptographic report. |

| ENCLS[EDBGWR] | Write data into a debug enclave by debugger. | ENCLU[ERESUME] | Re-enter an enclave. |

| ENCLS[EEXTEND] | Extend EPC page measurement. | ||

| ENCLS[EINIT] | Initialize an enclave. | ||

| ENCLS[ELDB] | Load an EPC page in blocked state. | ||

| ENCLS[ELDU] | Load an EPC page in unblocked state. | ||

| ENCLS[EPA] | Add an EPC page to create a version array. | ||

| ENCLS[EREMOVE] | Remove an EPC page from an enclave. | ||

| ENCLS[ETRACK] | Activate EBLOCK checks. | ||

| ENCLS[EWB] | Write back/invalidate an EPC page. |

表格总结了未来Intel处理器的Intel SGX增强功能。

Supervisor and User Mode Enclave Instruction Leaf Functions in Long-Form of SGX2:

| Supervisor Instruction | Description | User Instruction | Description |

|---|---|---|---|

| ENCLS[EAUG] | Allocate EPC page to an existing enclave. | ENCLU[EACCEPT] | Accept EPC page into the enclave. |

| ENCLS[EMODPR] | Restrict page permissions. | ENCLU[EMODPE] | Enhance page permissions. |

| ENCLS[EMODT] | Modify EPC page type. | ENCLU[EACCEPTCOPY] | Copy contents to an augmented EPC page and accept the EPC page into the enclave. |

参考资料

Intel v3 Chapter 33

https://www.intel.com/content/www/us/en/developer/tools/software-guard-extensions/overview.html