目录

1.SRAM保护配置使能

2.测试结果分析

3.小结

我们接着上文继续来梳理如何配置LMU的保护机制 英飞凌TC3xx的LMU SRAM保护机制(一)-CSDN博客

1.SRAM保护配置使能

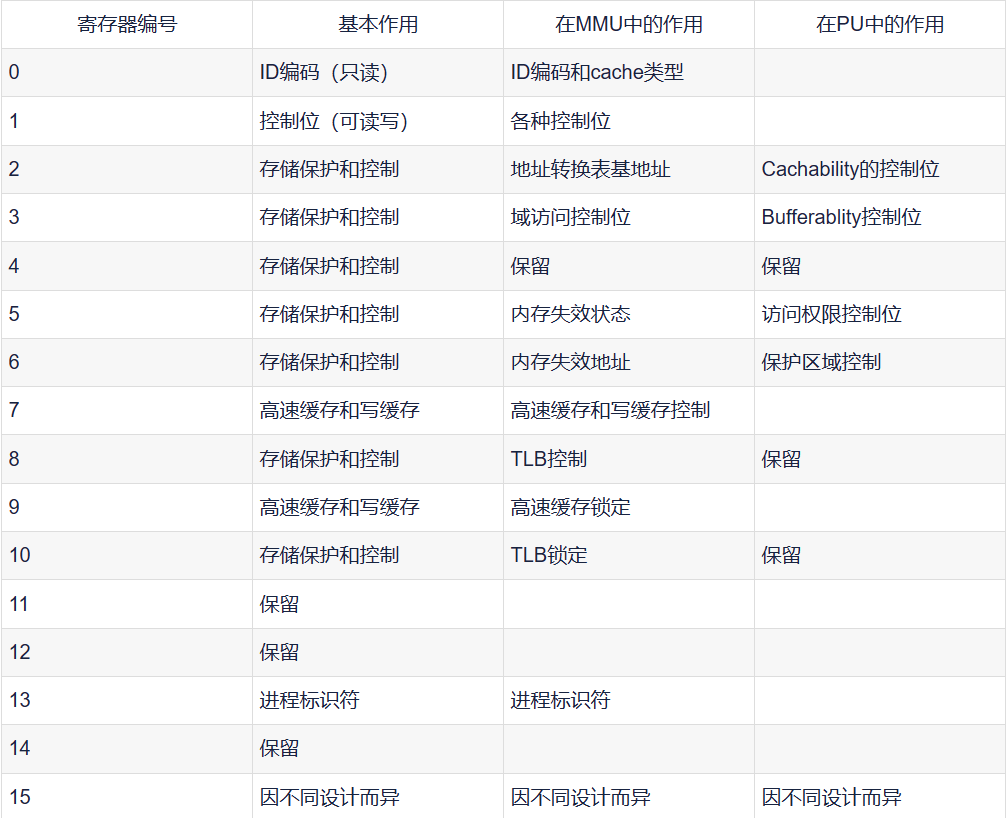

简单举两个例子,地址下限寄存器如下:

可以看到使用SRI地址的bit31-5用于作为边界,为什么低5位不要呢?因为手册上说明最小保护单位为32byte。

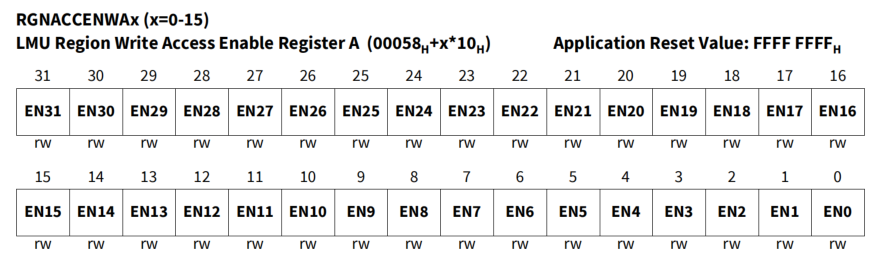

写权限配置寄存器如下:

所以,配置就很简单了:

首先明确保护区域,配置好上下限,

然后根据需要开启或者关闭对应master tag id的读写权限。

开测

2.测试结果分析

事实上,真的有上述那么简单吗?我做了这么一个试验:

1.LMU0从B004 000+32KB,使用了Master Tag ID保护,CPU0仅有写操作;

2.在上述位置定义变量

3.测试CPU0写访问操作

代码示例如下:

void lmu_test(void)

{

int cpu_id;

int i;

cpu_id = GetCoreIdcpu_id();

printf("CPU %d original lmusfdata:%u\n", cpu_id, testdata[32 * 1024 - 1]);

for (i = 0; i < 32 * 1024; i++)

{

lmutestdata = cpu_id;

}

printf("CPU %d modified lmusfdata:%u\n", cpu_id, testdata[32 * 1024 - 1]);

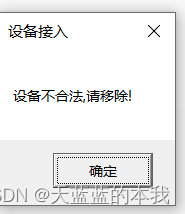

}实际上,CPU0仍然可以进行写访问。

这就有点奇怪了,因此回看芯片手册,发现这样一句话:

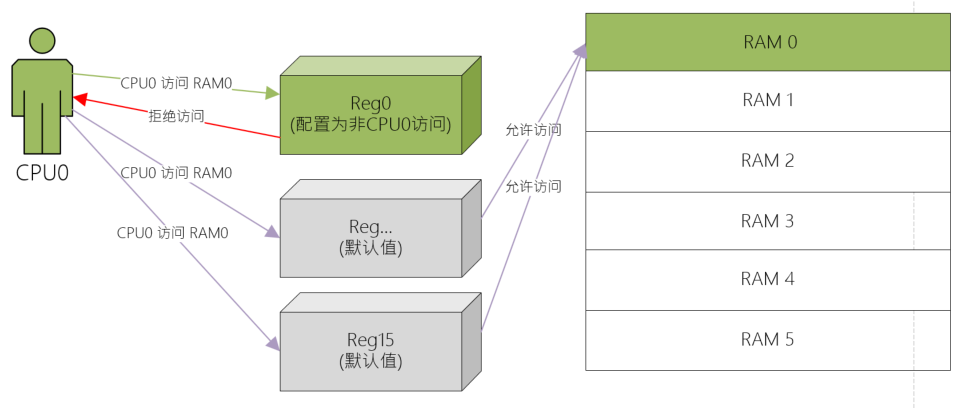

针对LMU0的区域,我只配置了一组寄存器,而其他15组没有配置,查看寄存器默认值,[LA,UA] = [0x00000000, 0xFFFF FFE0]。

问题就来了,交叉的区域是根据最高权限来的,所以CPU0仍然可以通过其他寄存器访问LMU0的受保护区域,如下:

也就是说,想要CPU0不能访问RAM0,还得把余下所有的寄存器组均配置,这里有两种方式就不一一列举了。

最后一个for循环将所有寄存器全部配置了,测试结果cpu0无法写入。

3.小结

这用起来就很麻烦了,假设现在想CPU0独占RAM0,CPU1独占RAM3,那首先配置2套寄存器,只开启CPU0/1的读写权限;为了保证独占成功,还得去配置其余14套寄存器,那应该如何去分寄存器呢?例如RAM0的独占写几套寄存器?RAM3独占需要写几套寄存器?

不知道各位有没有实际应用过这种以master tag id方式保护的内存保护方法,欢迎大家积极讨论。