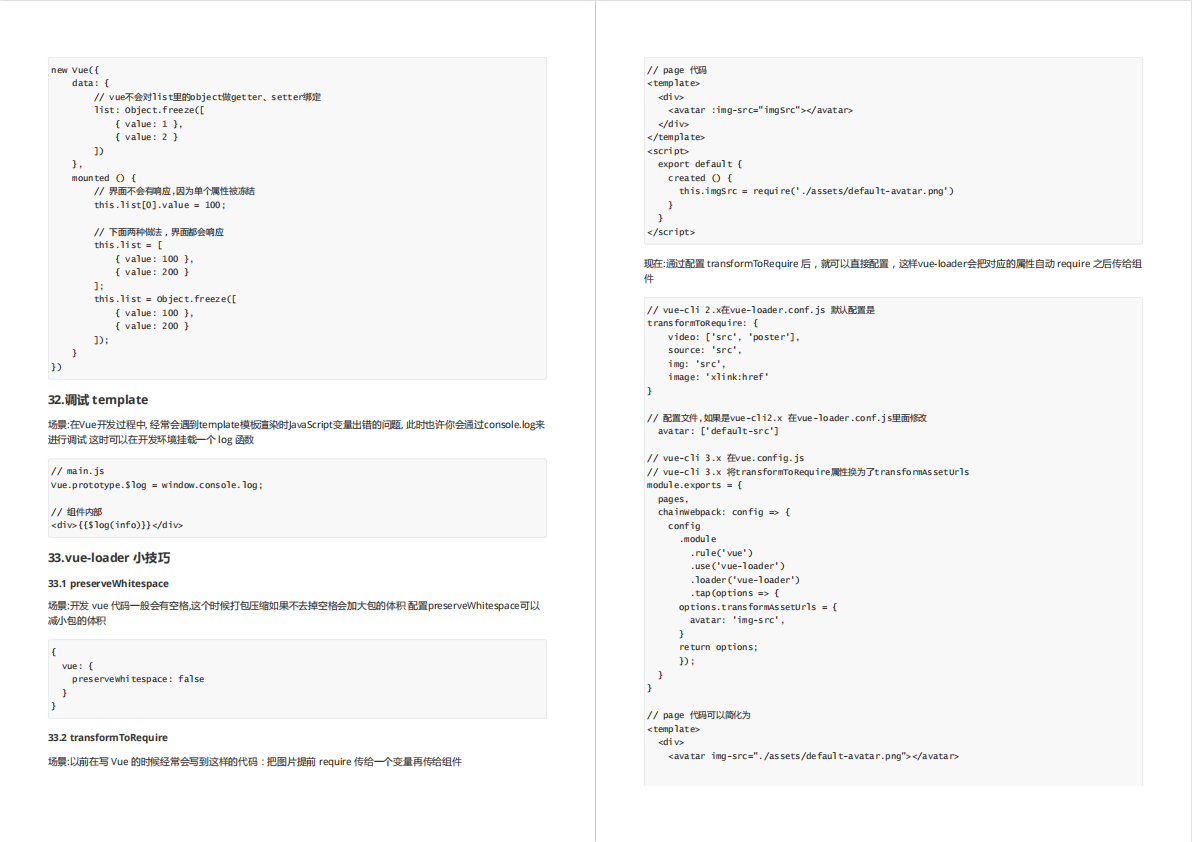

pdm 协议

PDM接口只有两根信号线:

PDM_CLK 时钟信号。

PDM_DATA 数据信号。

I2S协议

数据发送规格

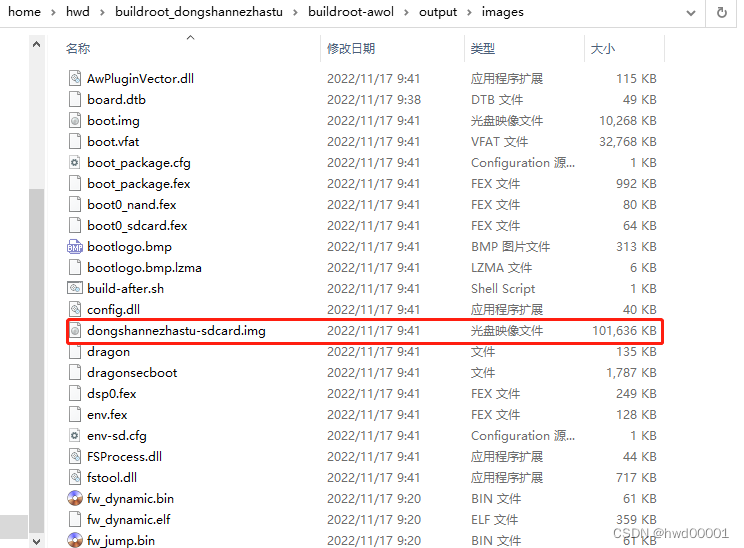

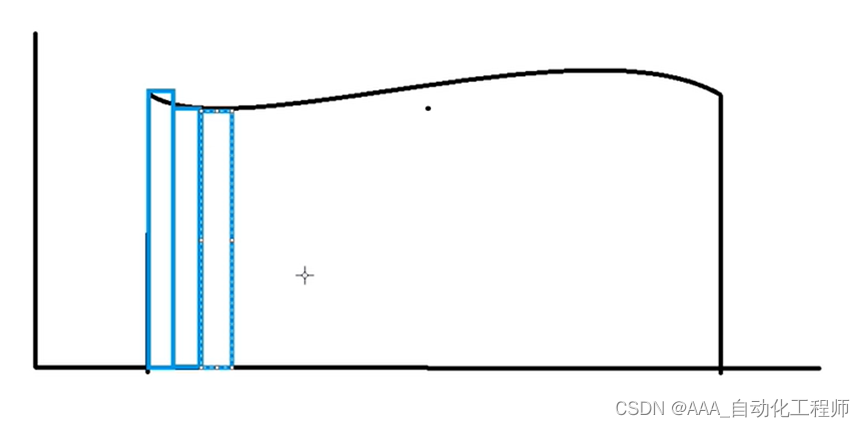

I2S在BCLK的下降沿发送数据(发送),在上升沿进行数据采样(接收)。每次是先发送最高位,最后发送最低位。MSB在WS变化的下一个时钟周期有效。因此,最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。也就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。

I2S发送数据:发送是在每个时钟周期的下降沿发送数据,这样在WS沿变化开始后的第二个下降沿发送数据的最高位。接着在每个下降沿依次发送数据,直到发送完最低位。

I2S接收数据:在每个时钟周期的上升沿接收数据,在WS沿变化开始后的第二个上升沿接收数据的最高位。接着在每个位时钟上升沿依次接收数据,直到接收完最低位。

比如如下的一个ws高电平内,在每个clock上升沿采集数据,可以读到ws为高时data电平为10010100 11011001 01010011 01010100

对应data数据为0x94 D9 53 54

驱动配置

- pdm data输出接 I2S data数据输入线,pdm clk由I2S clk提供,所用规格需clk在1M-3.5M之间,故设定clk=1.024M.

- 配置I2S clk时钟树(配置I2S 时钟控制寄存器)查看时钟树方法,cat /sys/kernel/debug/clk/clk_summary

- 使能I2S clk时钟;

- 配置I2S 接受寄存器的采样深度为32bits

- 配置和I2S关联的dma

pdm data 转 pcm data

采用抽取滤波器将pdm 的频谱数据转为pcm的模拟数据

sample

(待写。。。)

![[附源码]SSM计算机毕业设计班级风采网站JAVA](https://img-blog.csdnimg.cn/fb4d03f8cf8f41bb85cbca6aa71605b8.png)

![[MySQL]复杂查询(进阶)](https://img-blog.csdnimg.cn/30a79469ee0341b7820dca7d4ccead77.png)