UASRT参数配置

数据发送过程

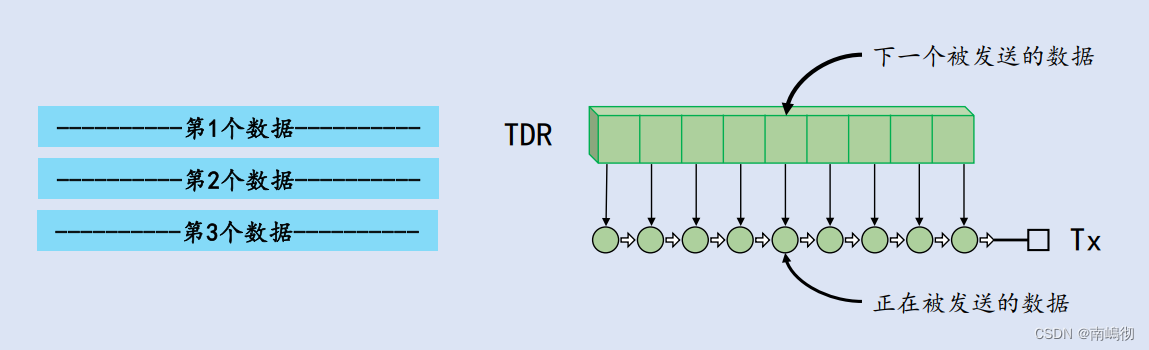

1.双缓冲

当要发送三个数据 且是连续发送 第一个数据写入TDR寄存器 然后到移位寄存器发送(一个一个bit的发送)在第一个数据在移位寄存器发送的时候第二个数据就已经被写入TDR寄存器了等到第一个数据发送完第二个数据就进入移位寄存器中发送 依次类推第三个数据也是同第二个数据如此

这样通过双缓冲就可以完成多个数据的连续发送

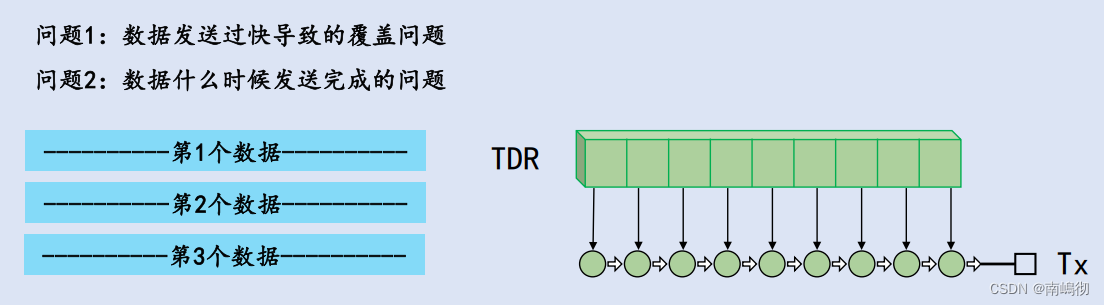

在数据的发送中会存在两个问题

1 就是数据发送过快 在写入寄存器中数据覆盖了(如第二个数据被第三个数据覆盖了)

2 还有就是不知道数据发送完到底是什么时候

那么就涉及到了SR状态寄存器 通过读取状态寄存器的一些比特位可以解决相关的问题

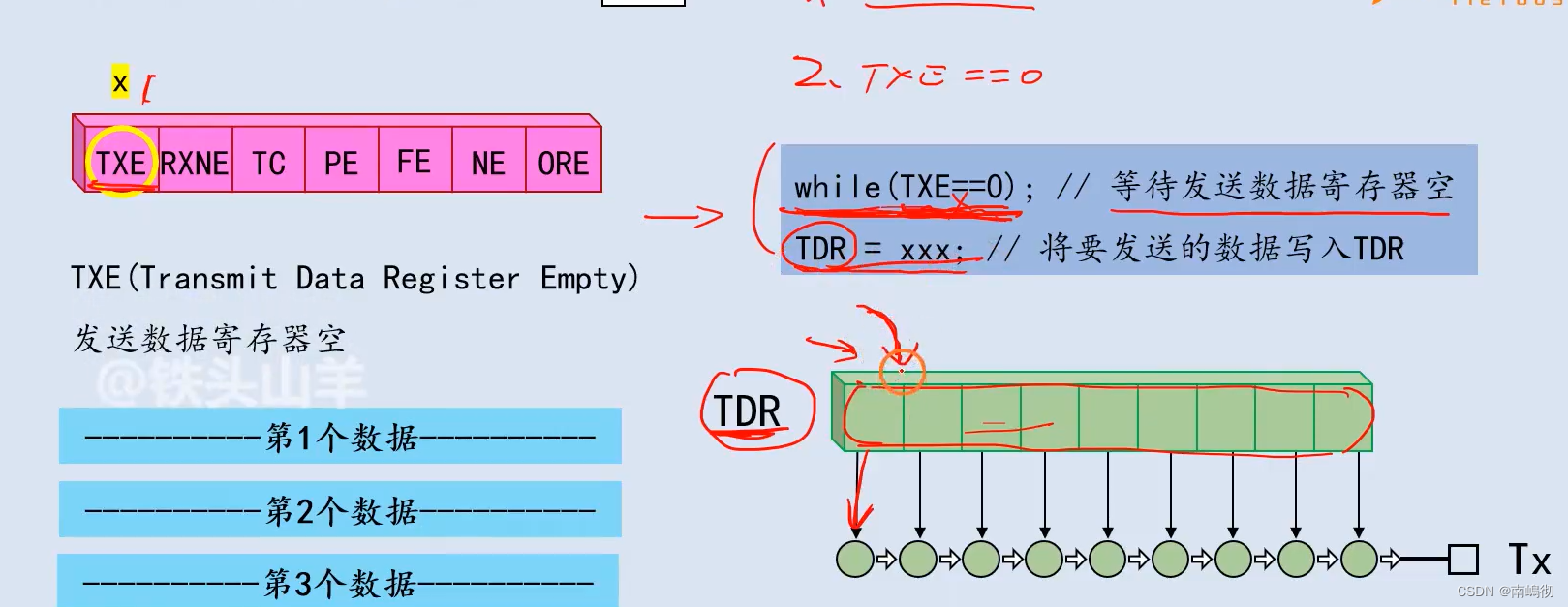

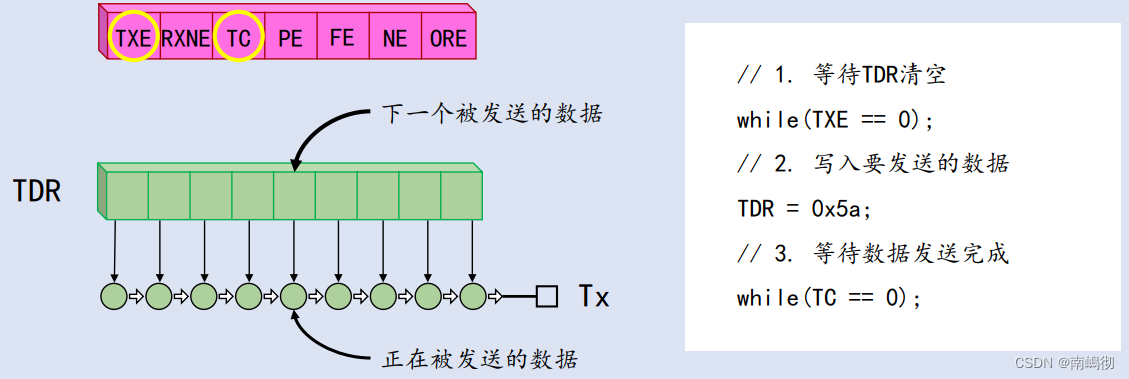

TXE标志位

TXE是SR状态寄存器的最左边

当IDR寄存器中还有数据时(数据正在等待被传输到移位寄存器中被发送)TXE位就为0 当IDR寄存器没有数据时(表示可写入数据)TXE位就为1 这样写一个while循环当TXE为0时就不写入数据 当TXE为1时就可以写入数据

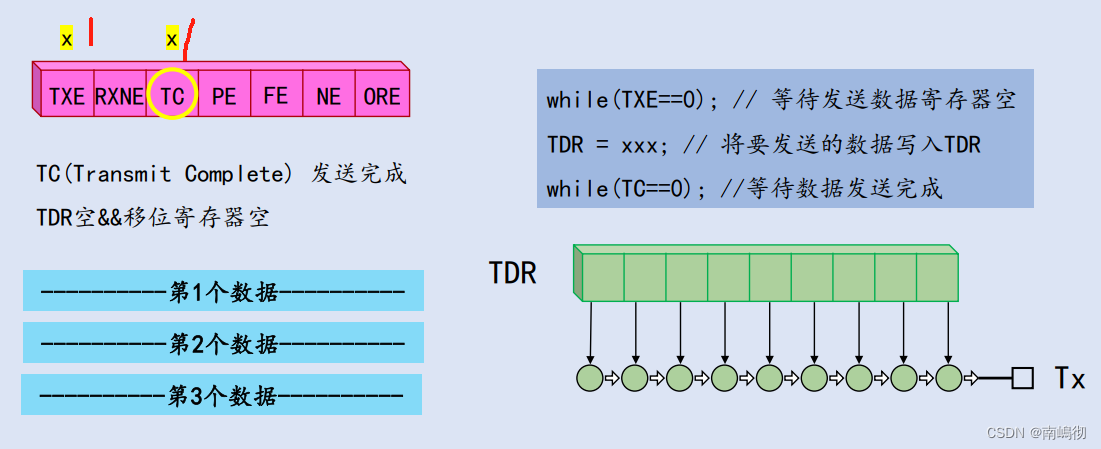

TC标志位

TC标志位为1时需要TDR寄存器为空 并且移位寄存器也为空 才使得TC标志位为1 当数据进入TDR 然后进入移位寄存器中处理一段时间才能全部把一个字节的数据发送完成 当数据还在移位寄存器发送的时候 TXE为1 (IDR寄存器为空) 当移位寄存器传输完数据后 移位寄存器也为空位状态 然后TC也为1 当标志位TXE和TC都为1就表示一个数据的传输完成

单个数据的发送

当TDR = 0后就写入要发送的数据到移位寄存器中 然后等待数据发送完成后 标志位TC=0标志着可以写入下一个数据到TDR寄存器中

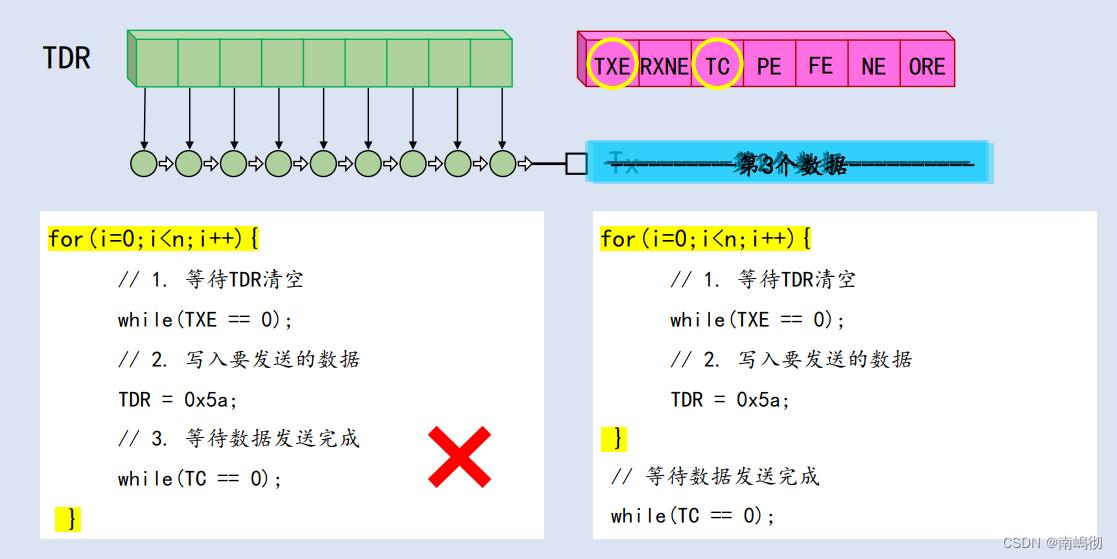

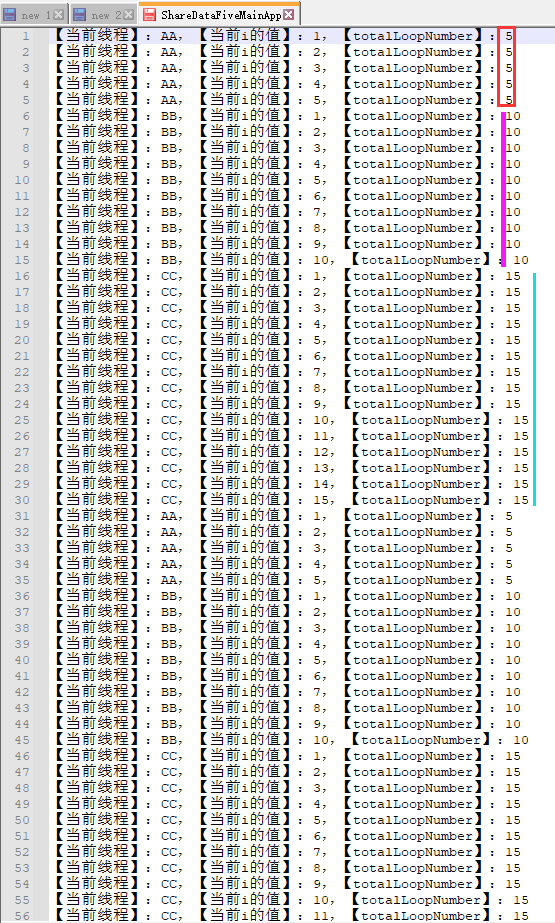

数据的连续发送

第二种循环才是对的 第二种方式运用到了两个缓冲 但是第一个方式一直是一个数据再发送 就是第一个数据发送完才能发送第二个数据 而第二种方式是在第一个数据发送时第二个数据也被写入TDR寄存器 更加高效快捷

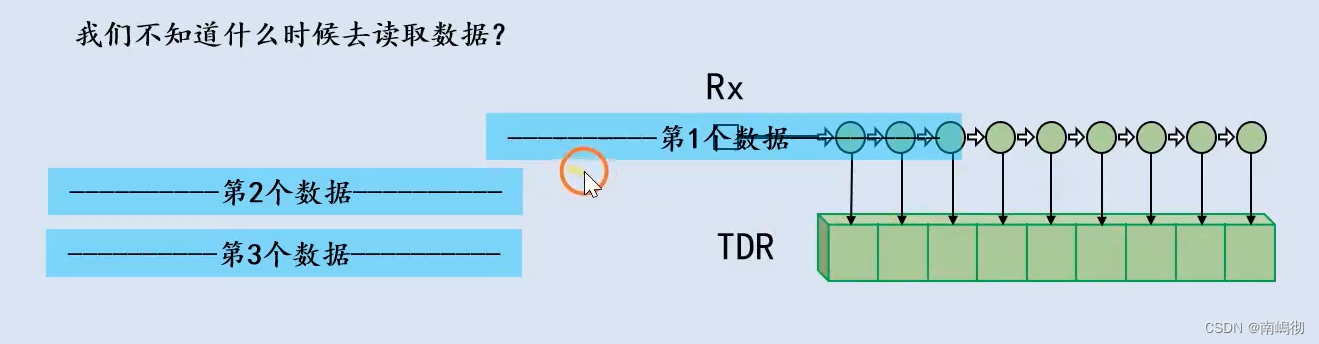

数据接收时候的问题

我们不知道什么时候读取数据的 就是不知道什么时候发送方发送数据会造成读取数据过快和过慢造成数据的丢失

图中的寄存器应为RDR

当数据到移位寄存器中 RDR寄存器读取数据过早时就会乱码

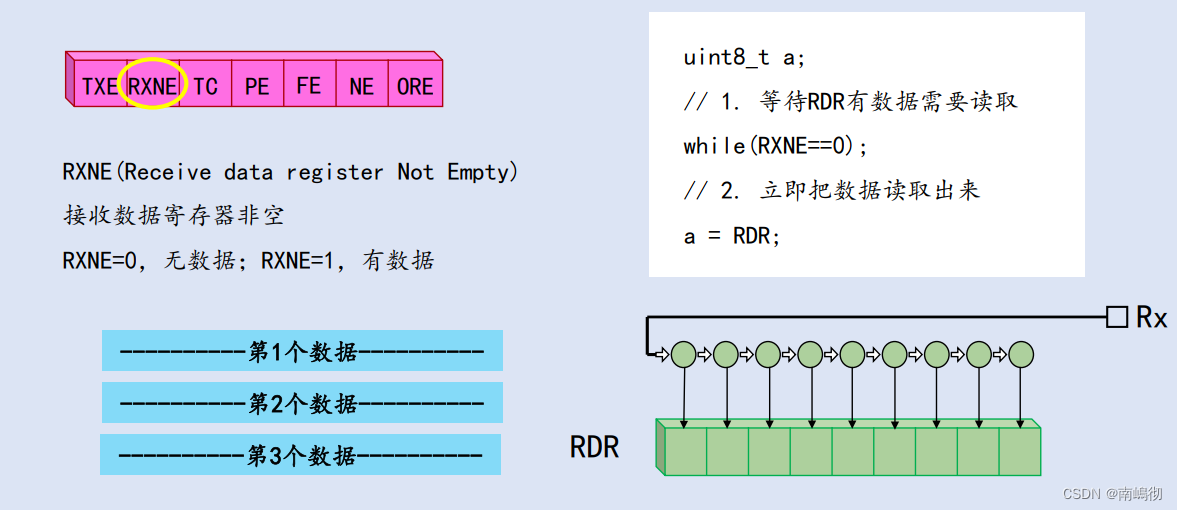

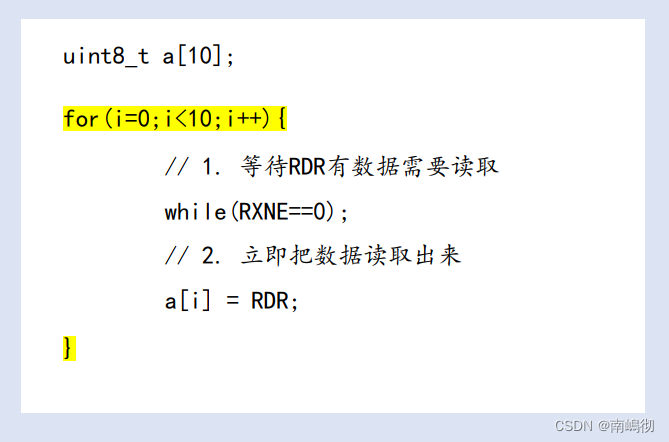

一个字节的数据读取 就是接收单个数据的代码

接收多个数据的代码

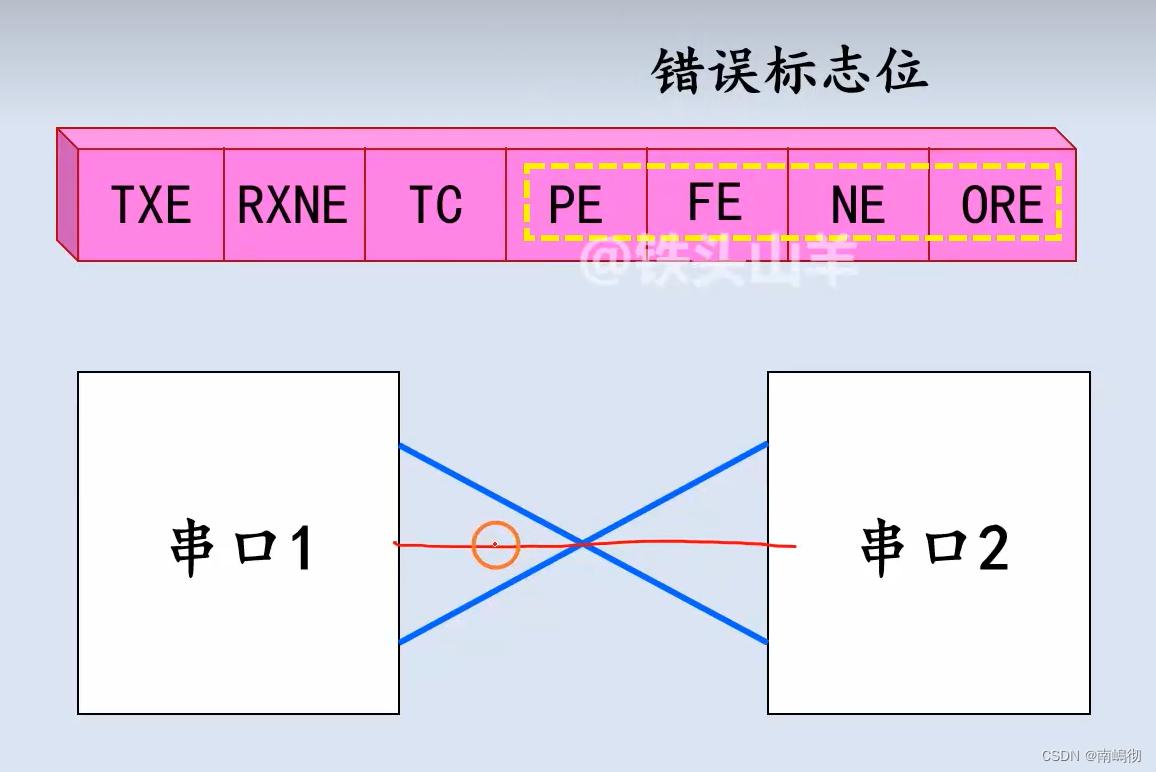

错误标志位

在串口传输数据的过程中可能会发生数据错误的情况 但是如何来判断数据是否错误呢? 就是通过错误标志位 错误标志位实在SR状态寄存器中的

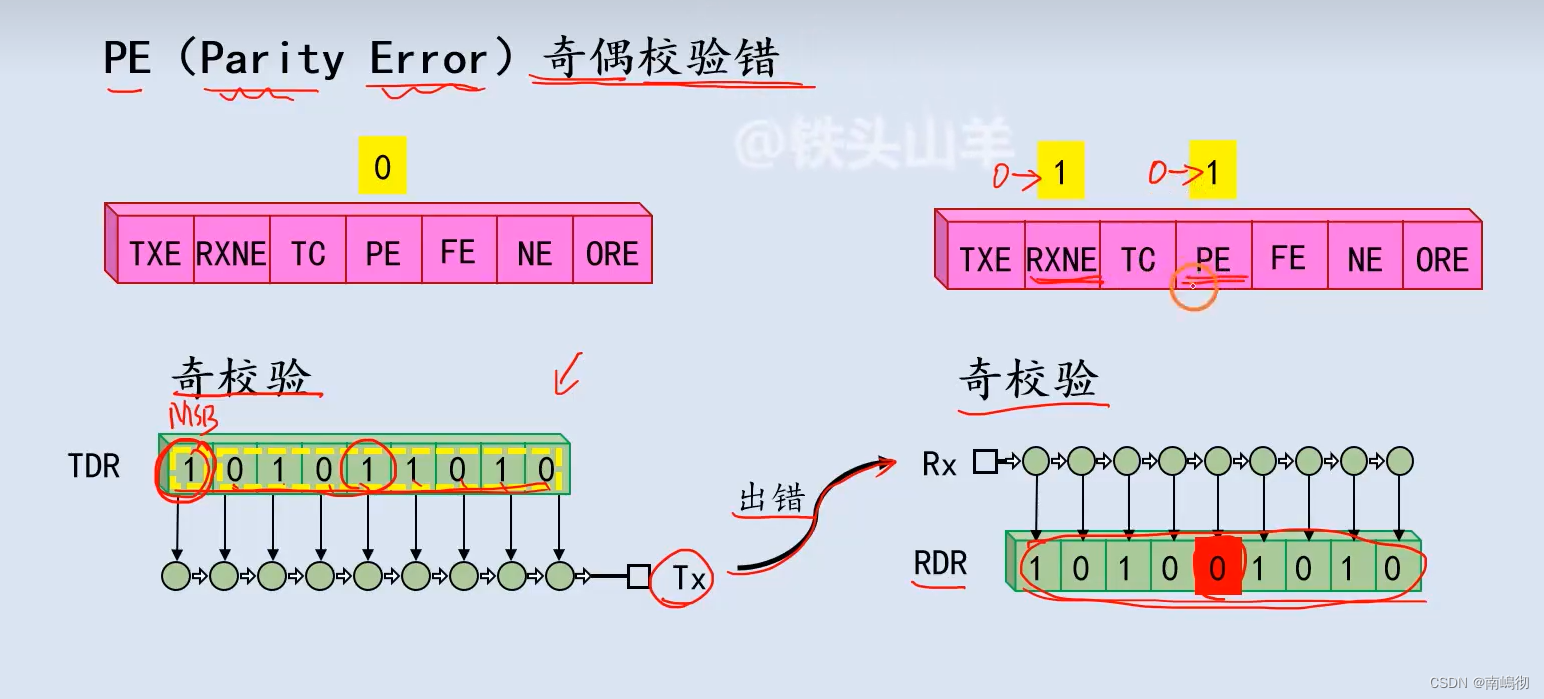

PE奇偶校验错

当数据在传输的过程中以数据帧的形式传输 通常会拿最后一个位MSB作为校验位 如这里设置为奇校验 数据中只有4个1就在MSB校验位中自动补上一个1

一共就有5个1 在数据的传输中有错 数据出错 接收方的SR状态寄存器中的RXNE位由0变为1表示接收到了数据 PE位为1表示接收到的数据错误

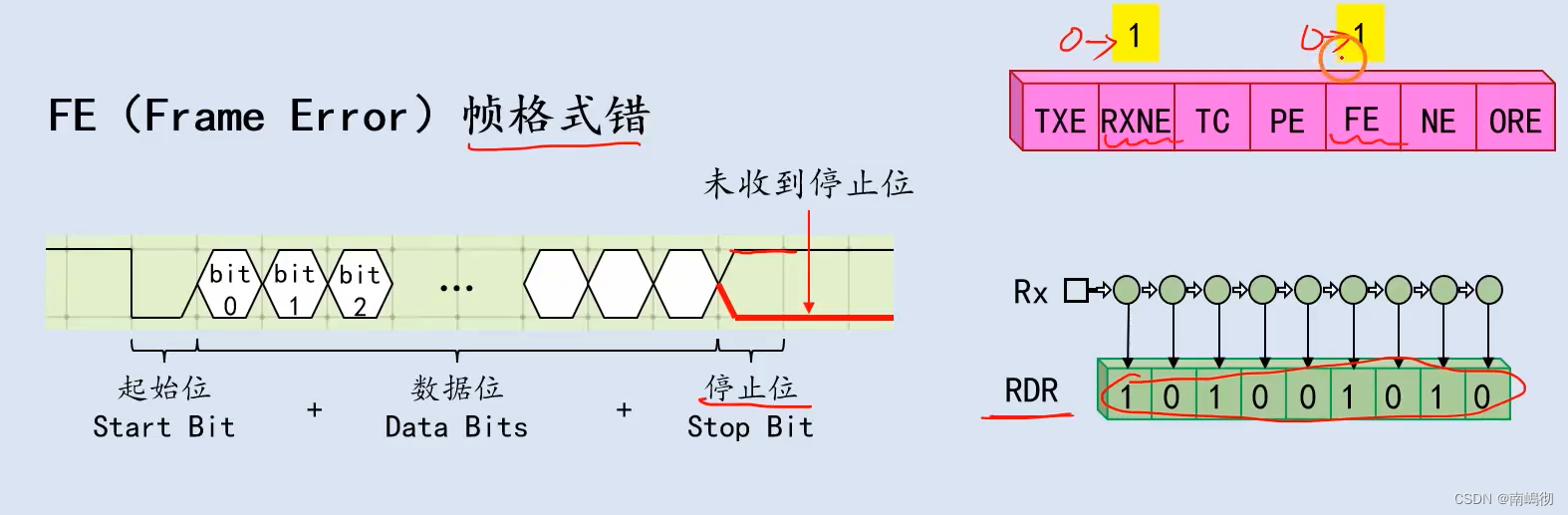

FE帧格式错

就是在该收到停止位的地方没有收到停止位的高电平 表示接收到的数据不完整FE标志位置1

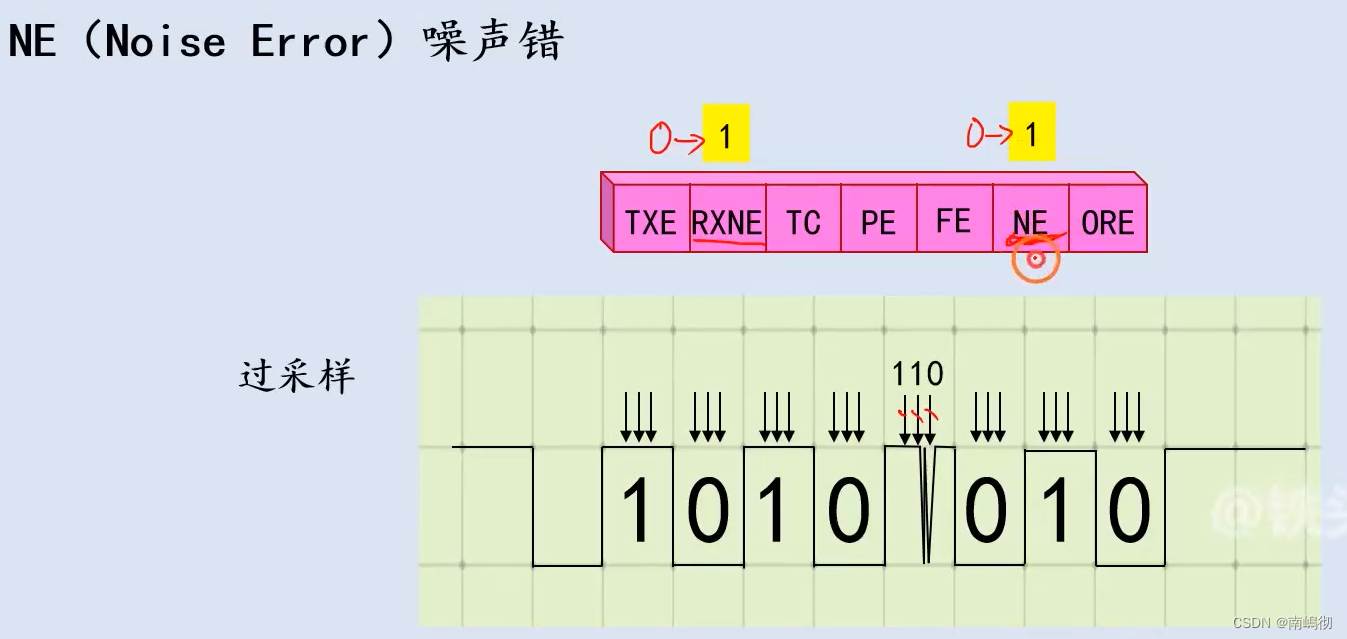

NE噪声错

在数据的传输中数据是以数据帧的形式传输的 通常接收方会以一定的频率读取 如果三次读取到的都是高电平 那么就认定为高电平 但是由于噪声的影响会造成数据的读取失误就是不知道读取到的是什么电平

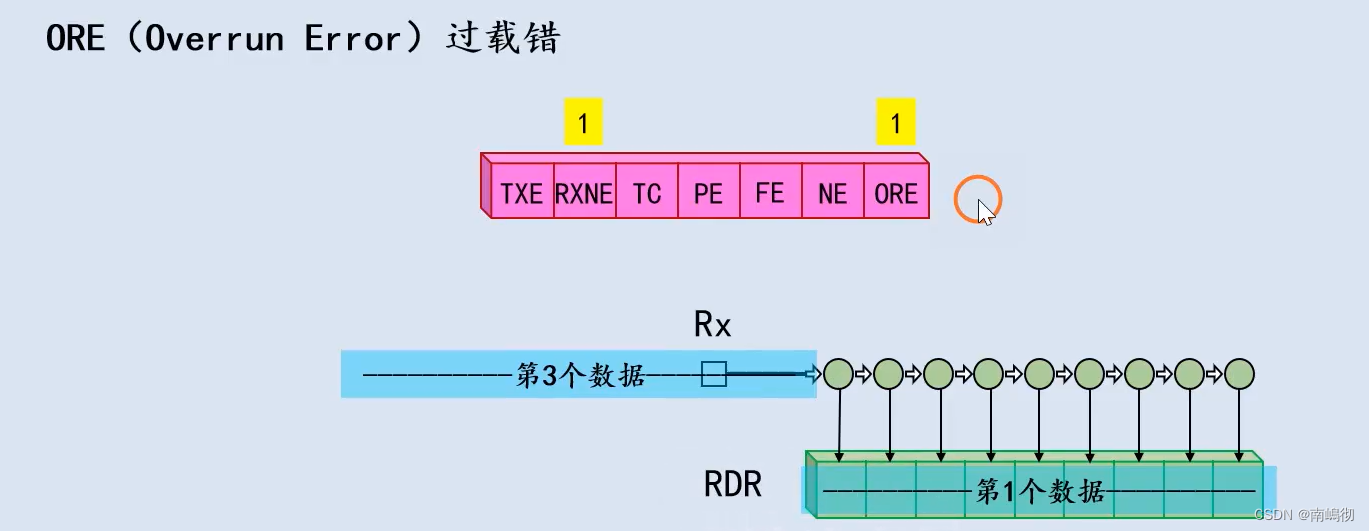

ORE过载错

由于读取数据过慢造成第二个数据被第三个数据覆盖 造成数据丢失 SR寄存器的ORE位就为1

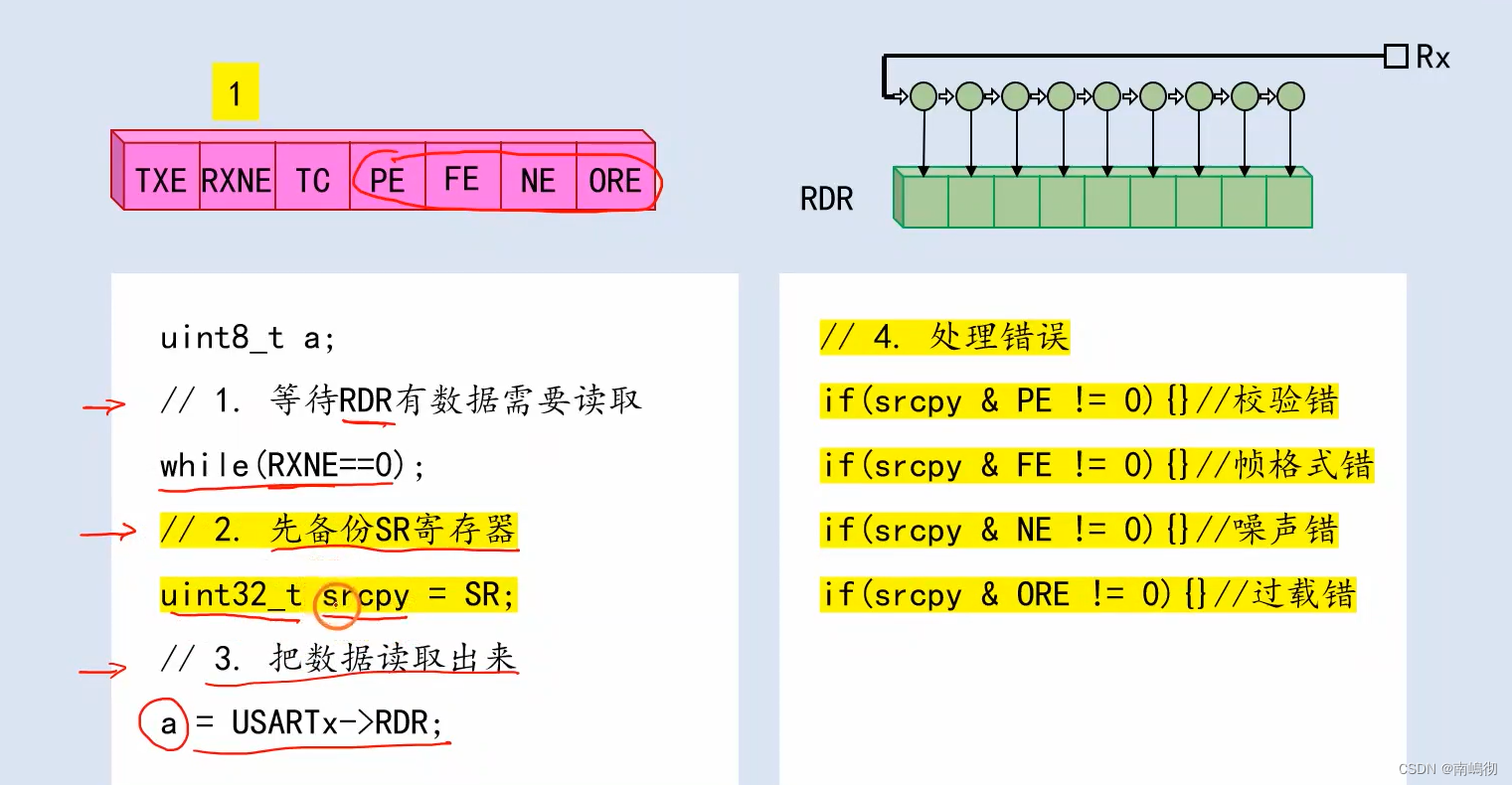

错误标志位的使用方法

接收到数据后 srcpy就为SR寄存器 检查是否错误校验位有错

![2023年中国农业机器人行业市场规模及发展趋势分析[图]](https://img-blog.csdnimg.cn/img_convert/c25ff6c236d5266b88b82585909e631c.png)

![2023年中国负极材料分类、产量及市场规模分析[图]](https://img-blog.csdnimg.cn/img_convert/d611948fb9ec855ae06a223d6a944cac.png)