https://www.ni.com/zh-cn/shop/wireless-design-test/what-is-the-mimo-prototyping-system/introduction-to-the-ni-mimo-prototyping-system-hardware.html

概览

随着采用无线连接方式的设备大量涌现,迫切需要研发可满足更高数据与容量需求的无线技术。来势汹汹的物联网(IoT)设备已对既有的无线网络造成很大负担,而随着视频流与虚拟现实技术的普及,现有数据传输速率已无法满足要求。多输入/多输出(MIMO)这项技术有望通过实现新一代无线技术来解决上述问题。只要使用多根天线,便能在相同的时域与频域传输多个数据信号,可大幅提升容量、吞吐量或可靠性,也可三者兼顾。随着顶尖研究人员与无线网络公司迫切探索全新通信技术,MIMO也将成为一个热门话题。

多用户MIMO (MU-MIMO)技术尤为突出,由其可见第五代(5G)无线网络的广阔前景。MU-MIMO使得基站能够采用大量天线,通过高级信号处理技术同时锁定多个用户,并重复使用相同的时间与频率空间。MU-MIMO与大规模MIMO(MU-MIMO的其中一个版本)能够将无线网络容量提高10倍以上,同时提供更高的可靠性和网络密度。

MU-MIMO与大规模MIMO的部分基本原理已经大致清楚,但研究人员必须建立真实原型,才能加快创新。通过NI MIMO原型验证系统这款测试台,研究人员便能针对5G MIMO系统进行原型验证,快速实现预期成果。

内容

- MIMO原型验证系统硬件

- 系统架构

- 系统配置选项

- 软件界面

- 总结

MIMO原型验证系统硬件

MIMO原型验证系统包含USRP RIO射频头、FlexRIO FPGA协处理器、时钟分配模块、PCIe路由硬件以及PXIe机箱和控制器。该系统可以配置为多种尺寸,以满足各种MIMO应用的要求,包括单用户MIMO (SU-MIMO)、多用户MIMO (MU-MIMO)和大规模MIMO。 本文将详细介绍各种系统组件与配置。MIMO应用框架技术白皮书对应用软件进行了相关介绍。

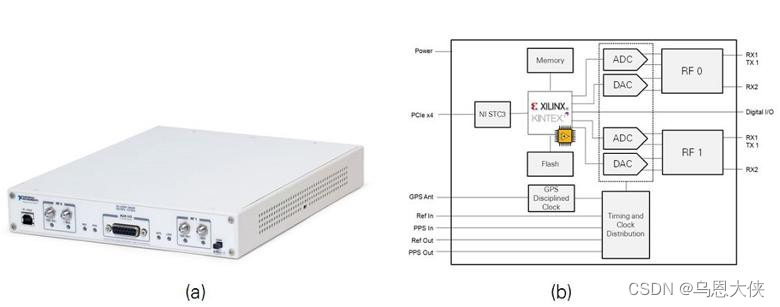

USRP软件无线电

USRP RIO软件无线电(SDR)采用集成式2x2 MIMO收发仪和高性能Xilinx Kintex-7 FPGA,这些组件均封装在半宽1U机架安装式外壳中,能够提高基带处理速度。此外,USRP RIO SDR通过连接至系统控制器的有线式PCI Express x4链路连接至主机控制器,并以高达800 MB/s的数据流速度将数据传输至台式或PXI Express主机(或通过ExpressCard以200 MB/s的速度传输至笔记本电脑)。图1为USRP RIO硬件的简要程序框图。

图1.USRP RIO硬件(a)与系统程序框图(b)

有线式PCI Express开关盒

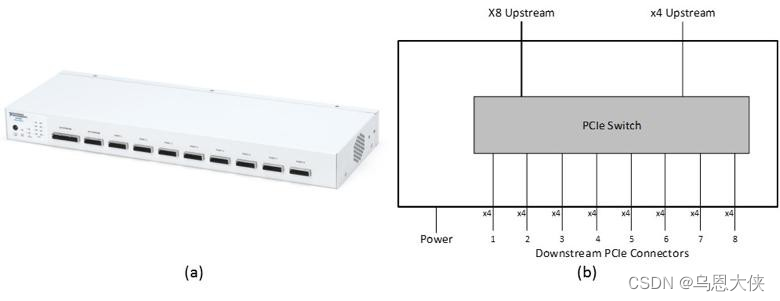

CPS-8910有线式PCI Express开关盒(CPS)将多个USRP RIO PCI Express链路汇聚到单个数据流中,不仅可以简化系统,同时也能有效地聚合多个通道。凭借有线式PCI Express x4 Gen 1链路,此开关盒可支持多达8个独立下游设备。在MIMO配置中,这些数据流汇聚到单个PCI Express x8 Gen 2链路,可实现高达3.2 GB/s的汇总数据传输速率。在其他配置中,可改为使用PCI Express x4 Gen 1上游链路。除此之外,CPS-8910也支持USRP设备之间的点对点数据流。铜质与光纤PCI Express线缆均受支持。图2为CPS-8910硬件的简要程序框图。

图2.开关盒(a)与系统框图(b)

PXI Express机箱背板

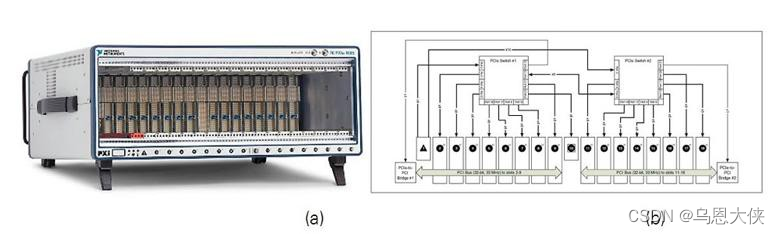

此系统采用PXIe-1085,PXIe-1085是一款高级18槽PXI机箱,每个插槽皆搭载PCI Express Gen 3技术,适用于高吞吐量、低延迟应用。机箱可提供8 GB/s的单槽带宽和24 GB/s的系统带宽。图3为双开关背板架构。

图3. 18槽PXIe-1085机箱(a)与系统框图(b)

高性能FPGA协处理器

MIMO原型验证系统集成了灵活的高性能FlexRIO FPGA处理模块,可使用PXI系统的LabVIEW FPGA模块进行编程。PXIe-7976R FlexRIO FPGA模块可做为独立设备使用,能够为大型可自定义的Xilinx Kintex-7 410T提供与PXI Express背板连接的PCI Express x8 Gen 2链路。

图4.PXIe-7976R FlexRIO模块(a)与系统框图(b)

精确时钟生成

PXIe-6674T同步模块(图5)具有高精确度的板载恒温晶体振荡器(OCXO),能够生成10 MHz参考时钟。该信号可以针对各个USRP RIO射频头建立参考时基,以确保精准的同步。PXIe-6674T也可对其中一个USRP RIO SDR的同步触发信号进行处理并重新输出。

图5.PXIe-6674T定时与同步模块

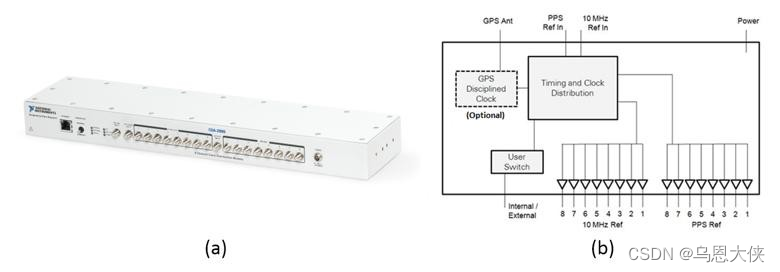

8通道时钟同步

CDA-2990 8通道时钟分配模块能够通过长度匹配轨迹,以8种方式放大并分割10 MHz参考信号和每秒脉冲信号,可为多达8个USRP设备提供频率与定时同步性能。CDA-2990通过集成式GPS驯服振荡器(GPSDO)额外增加内部定时与频率参考。图6显示的是使用GPSDO的CDA-2990的系统简图。

图6.CDA-2990 (a)和系统框图(b)

系统架构

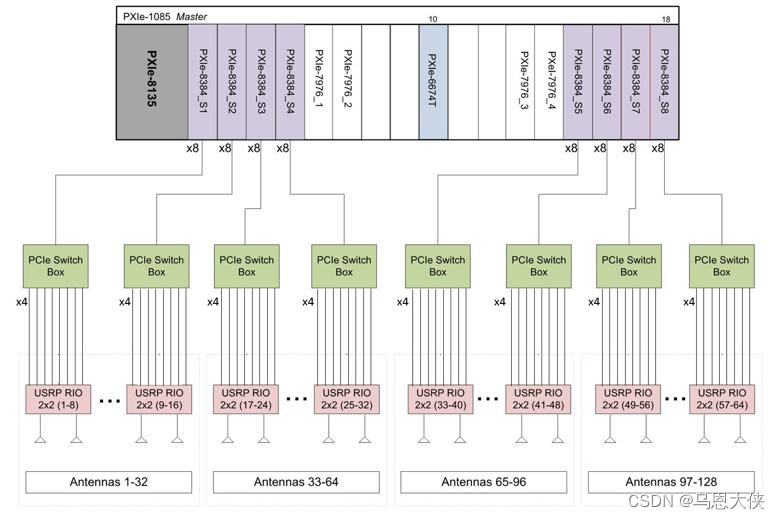

上述硬件元件组合在一起便构成测试台,该测试台天线数量可从几根扩展到超过128根同步天线。为了简单起见,本文的每个范例皆使用128根天线配置。

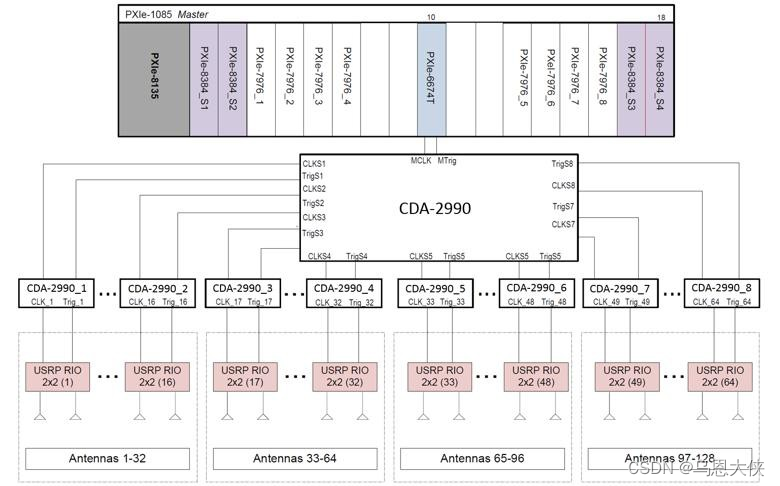

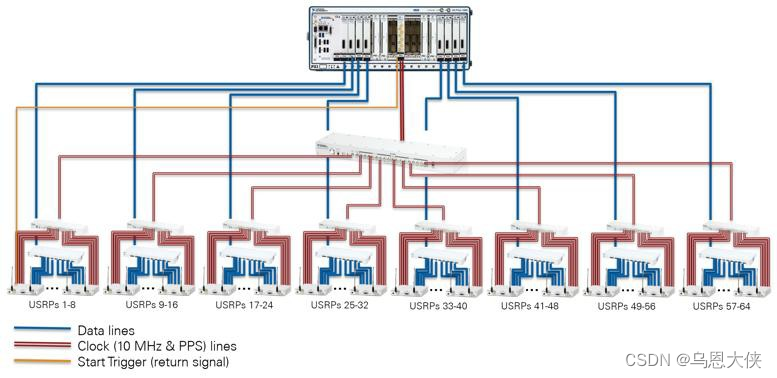

数据处理

高通道数MIMO系统需要能够非常稳定地进行数据处理。高达128个通道的I与Q样本皆须实时处理,以便收发。为了处理如此繁多的数据,MIMO原型验证系统采用了高吞吐量PCI Express总线。数据通过PCI Express开关盒从USRP RIO SDR传送至单个PXI Express机箱。机箱可汇聚数据,以便通过FPGA协处理器与四核英特尔i7 PXI控制器集中处理这些数据。如图7所示,PXIe-1085机箱是主要的数据汇聚节点与实时信号处理引擎。在机箱的插槽1内,PXIe-8135 RT控制器可用作中央系统计算机。PXIe-8135 RT配备了2.3 GHz四核英特尔酷睿i7-3610QE处理器(单核睿频加速模式可达3.3 GHz)。此机箱额外嵌入了8个PXIe-8384(S1到S8)远程控制模块,可将PCI Express开关盒连接至主系统。每个开关盒因而能够汇聚8个USRP RIO链路。PXI机箱与开关盒之间的链路采用PCI Express x8 Gen 2技术,可以在机箱与各个开关盒之间提供高达3.2 GB/s的速率。

此系统还具有PXIe-7976R FlexRIO FPGA协处理器模块,可满足MIMO原型验证系统的实时信号处理需求。每个PXIe-7976R皆采用强劲的Kintex-7 410T FPGA。每个FlexRIO模块都可以通过背板彼此间接收或传输数据,还可以与所有USRP RIO SDR相互接收或传输数据;每个FPGA协处理器的延迟均不到5 µs、吞吐量高达3.2 GB/s。FlexRIO FPGA协处理器的数量根据所使用的天线数量从1至4个不等。

图7.MIMO原型验证系统的数据通道

定时和同步

正确的定时和同步对于任何MIMO系统而言都至关重要。MIMO原型验证系统采用通用的10 MHz参考时钟与数字触发器,用于触发每个射频头的采集或生成功能,以确保系统级的同步(见图8)。机箱内的PXIe-6674T同步模块可通过OCXO生成较为稳定且精确的10 MHz参考时钟(精确度可达80 ppb)。该模块也提供数字触发,以实现与主机CDA-2990时钟分配附件的设备同步。而主机CDA-2990则负责向另外8个CDA-2990模块提供并缓存10 MHz参考(MCLK)与触发(MTrig),然后再供应至USRP RIO SDR,以此确保每根天线共用10 MHz参考时钟与主机触发器。因此,上述的定时与同步架构可非常精确地控制每个射频头/天线元件。这样便可实现相位相干运行,让各个通道与其他通道保持稳定的相位偏移。这时可使用软件校准技术充分地对齐通道。

图8.MIMO原型验证系统的时钟分配

数据路径硬件与定时模块结合在一起可构成强大的测试台,该测试台能够实时处理庞大的数据流量,并且满足MIMO研究人员的同步需求。此外,此系统本身也具有扩展性。只需稍微调整硬件架构,便能轻松添加更多天线。

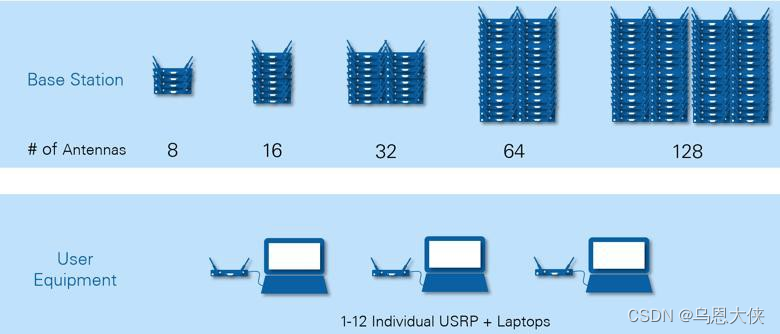

单天线UE

在MU-MIMO中,多天线基站能与数个单天线用户端设备(UE)进行通信。MIMO应用框架最多支持1个单天线UE。 UE可以是一部手机,也可以是其他无线设备。UE可以使用内置GPS驯服振荡器(GPSDO)的不同USRP RIO来表示,这些USRP RIO通过有线式PCI Express转ExpressCard链路连接至笔记本电脑。GPSDO非常重要,不仅可以提供更出色的频率精确度,还能够提供同步与地理定位功能。典型的MU-MIMO测试台包含多个可作为UE独立运行的USRP RIO。由于每个USRP RIO都有2个RF通道,每个USRP与笔记本电脑组合可代表2个UE。

多天线UE

MIMO应用框架可支持单天线UE和多天线UE。 UE可以配置为1、2、4、6、8、10或12根天线。 请注意,虽然UE可支持多达12根天线,但未经修改的MIMO应用框架初始最多仅支持12个空间数据流。 可以通过修改代码库来支持更多的空间数据流。

对于多于1根天线的UE,所需的硬件与基站的硬件相同。 也就是说,除了USRP RIO之外,还需要PXI机箱、控制器、FlexRIO FPGA 模块、PXIe-6674T定时和同步模块、CDA-2990参考和PPS分配模块以及CPS-8910 PCIe开关盒模块。

系统配置选项

MIMO原型验证系统具有可扩展性和灵活性,可满足用户需求。此系统最多可应对128根天线(图9),最少可应对2根天线。

多用户MIMO

图9. 128通道MU-MIMO设置

如图10所示,较常见的基站配置为16根天线、32根天线、64根天线与128根天线。如果使用MIMO应用框架,则可支持多达12个空间数据流。不过,UE的数量不能超过基站天线的数量减一。基站天线与UE的比例大于8:1时,可实现出色性能。

图10.常见MU-MIMO配置

MU-MIMO的实际设置可能会因研究需求而有所不同。举例来说,可以使用NI提供的天线或自行设计的天线来连接射频头。也可以选购已完成组装并经过机架测试的较大型MIMO配置。

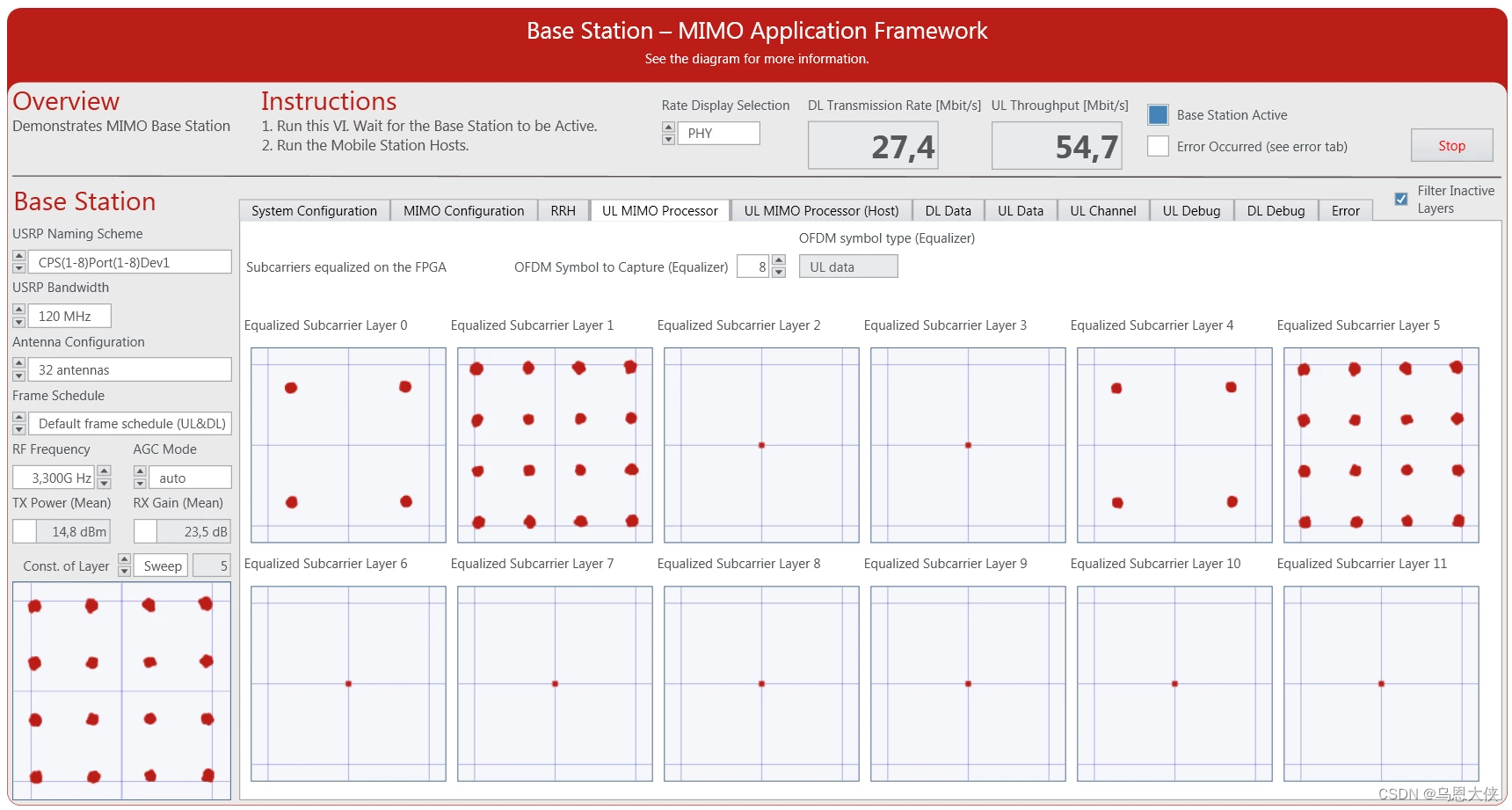

软件界面

虽然MIMO原型验证系统可使用LabVIEW和LabVIEW Communications完全从零开始编程,不过此系统专为搭配MIMO应用框架使用而设计。图11所示的软件框架提供了开放式可重配置的物理层参考设计,能够根据研究需要进行配置,也可用作全新MIMO应用的基础。

图11.MIMO应用框架的前面板

MIMO应用框架可使用LabVIEW Communications进行部署,并支持现成即用的FPGA IP来实现MMSE、MRC和ZF波束成形。应用框架还提供了空口同步、信道互惠校准、可重配置的框架结构、MIMO侦测、预编码与实时通信功能。请参阅MIMO应用框架技术白皮书,了解更多信息。

总结

MIMO应用框架可使用LabVIEW Communications进行部署,并支持现成即用的FPGA IP来实现MMSE、MRC和ZF波束成形。应用框架还提供了空口同步、信道互惠校准、可重配置的框架结构、MIMO侦测、预编码与实时通信功能。请参阅MIMO应用框架技术白皮书,了解更多信息。