专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

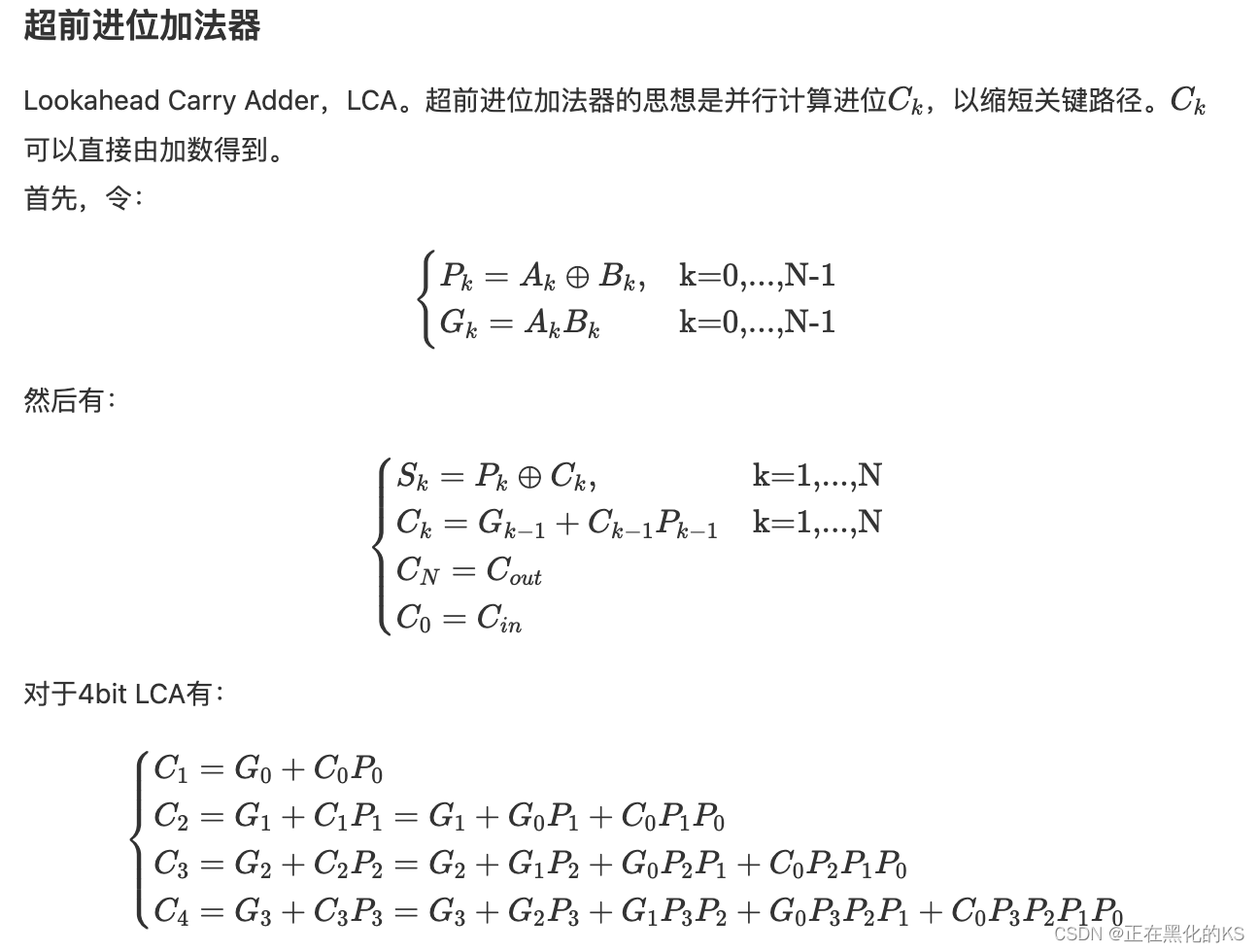

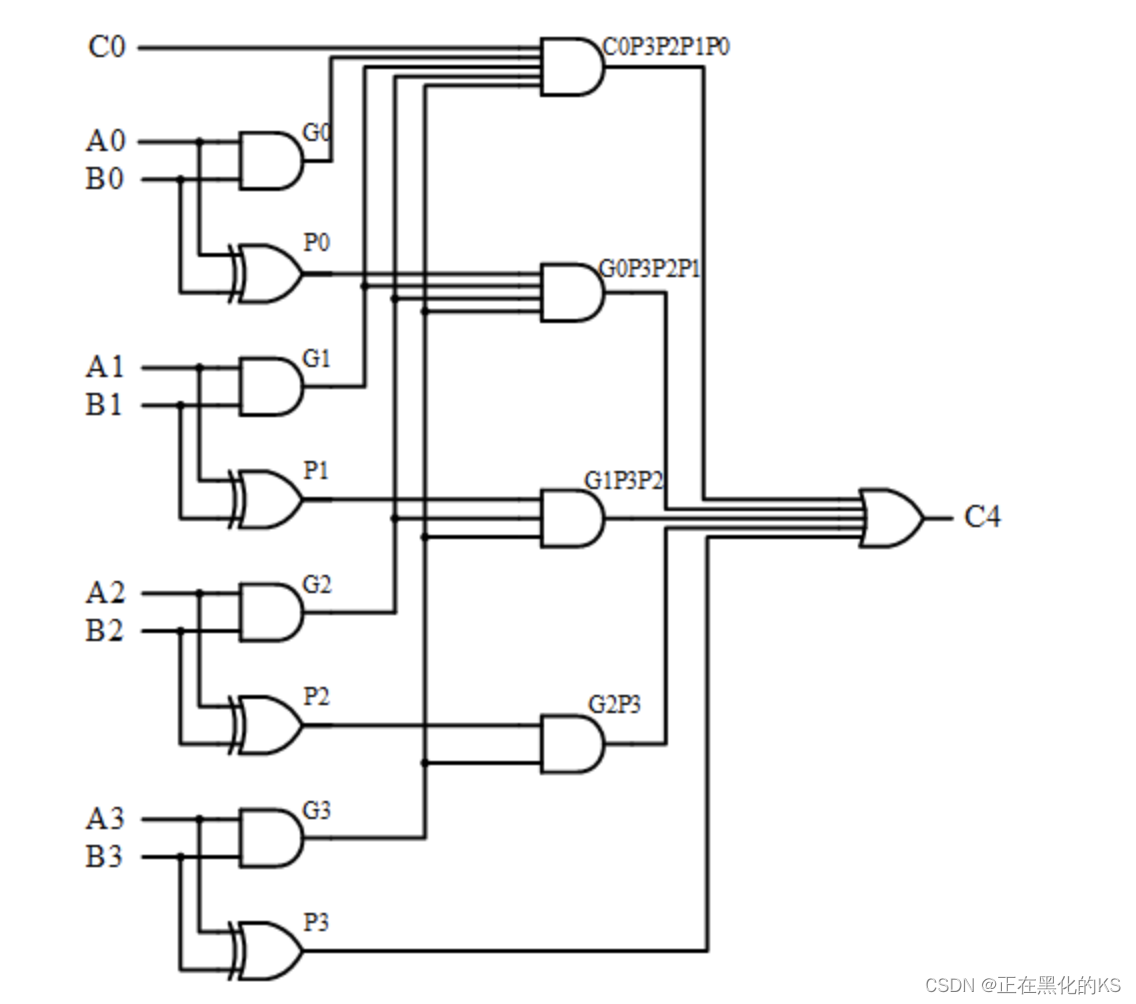

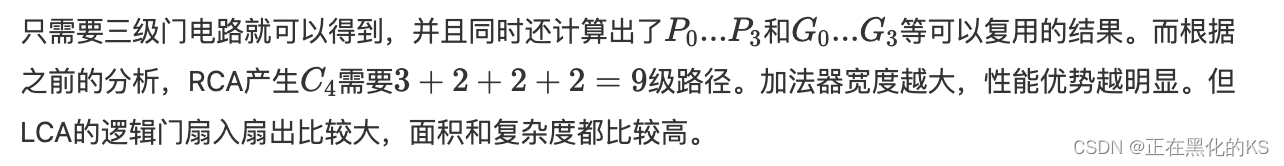

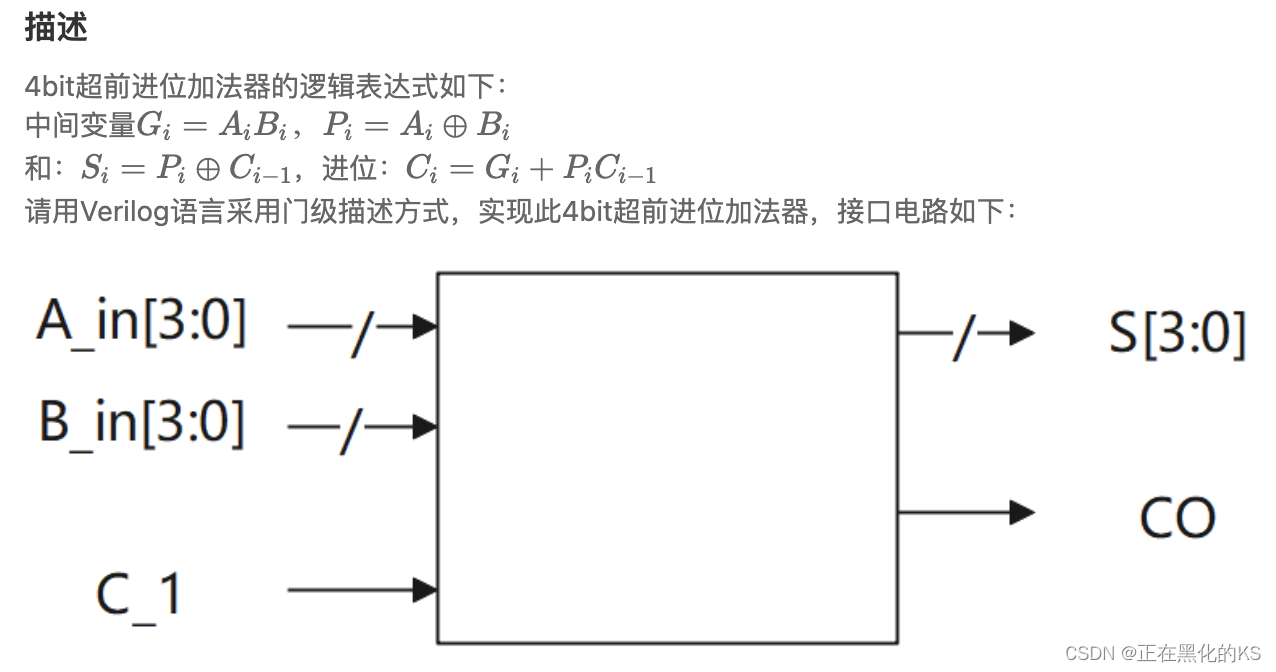

分析

`timescale 1ns/1ns

module lca_4(

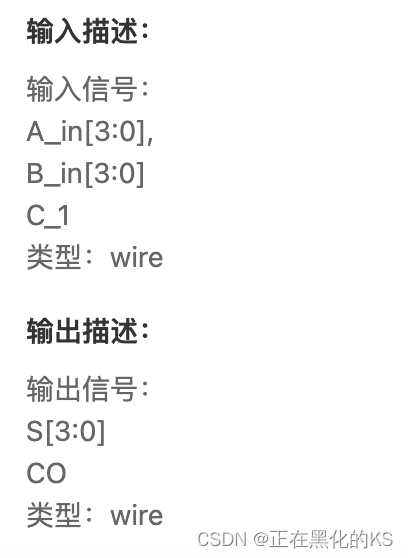

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire [3:0] C ;

wire [3:0] P ;

// Pk = Ak ^ Bk

assign P[0] = A_in[0] ^ B_in[0] ;

assign P[1] = A_in[1] ^ B_in[1] ;

assign P[2] = A_in[2] ^ B_in[2] ;

assign P[3] = A_in[3] ^ B_in[3] ;

// Ck = Gk-1 + Ck-1 * Pk-1, Gk = Ak * Bk

assign C[0] = (A_in[0] & B_in[0]) || (P[0] & C_1);

assign C[1] = (A_in[1] & B_in[1]) || (P[1] & C[0]);

assign C[2] = (A_in[2] & B_in[2]) || (P[2] & C[1]);

assign C[3] = (A_in[3] & B_in[3]) || (P[3] & C[2]);

assign CO = C[3];

// Sk = Pk ^ Ck

assign S[0] = P[0] ^ C_1 ;

assign S[1] = P[1] ^ C[0] ;

assign S[2] = P[2] ^ C[1] ;

assign S[3] = P[3] ^ C[2] ;

endmodule