很多入行不久的朋友潜意识里会认为FPGA是很高深的东西,能掌握FPGA的一定都是极其厉害的人。

其实,这是一个误解。

我们所讨论的FPGA只是基于已有的FPGA芯片去做后端排列组合的工作内容,而不是设计制造新的FPGA芯片,世界上能做这件事的公司屈指可数。

在说明FPGA为什么转IC前端之前,需要明确一下概念。

一、什么是FPGA?

FPGA像是IC行业里的乐高(拼乐高很容易,造乐高就极难了),它由大量基本的单元构成,让你组成自己想实现的功能。

FPGA:Field(现场)Programmable(可编程)Gate(逻辑门) Array(阵列)

这其中凸显了大量的逻辑门单元,这些逻辑单元是可以在任何地方随时进行组装的,这是不是跟组装积木一样?

在硬件描述语言出现之前,电路是用门搭的。

逻辑门单元是构成一切数字逻辑器件的基本单元,在数字世界里你想做任何事情、实现任何功能,都可以通过逻辑门的堆砌来实现,也就是说FPGA在数字领域里几乎无所不能。

前些年某FPGA公司在宣传其产品是称之为“万能芯片”,万能有些夸张,但FPGA高度灵活,理论上来讲,只要有足够的资源(积木数量足够多)几乎可以实现数字域的任何功能,受限的是速度、功耗以及系统的成本。

二、FPGA和ASIC的区别和共通点

1、作用ASIC——专用集成电路ASIC由IC设计人员根据特定的电路需求,设计专用的逻辑电路,在设计完成后生成设计网表,交给芯片制造厂家流片。

在流片之后,内部逻辑电路就固定了,芯片的功能也就固定的。FPGA——现场可编程门阵列FPGA由Xilinx,Alter等器件厂家提供,设计人员只需要根据需求选择相应的器件,然后设计逻辑电路,并下载到FPGA器件中去,实现需求的电路功能,随时可以修改电路功能。

2、适用性FPGA主要用于要求快速迭代或者小批量产品,或者作为ASIC的算法验证加速。ASIC用于设计规模大,复杂度比较高的芯片,或者是成熟度高,产量比较大的产品。

3、成本小批量需求时,单片FPGA成本低于ASIC,随着产品量的增加,单片ASIC成本逐步降低

4、功耗在相同工艺条件下,FPGA要大于ASIC。FPGA,尤其是基于占用大量硅面积的、每个单元六个晶体管的静态存储器(SRAM)的查寻表(LUT)和配置元件技术的FPGA,其功耗要比对等的ASIC大得多

5、速度FPGA内部是基于通用的结构,根据RTL设计选择内部布局布线,当然通用必然导致冗余。ASIC是根据设计需求,最优化cell逻辑资源,并且做到最优布局走线,降低走线延迟和CELL延时。

显而易见,FPGA在适用性、普遍性、成本、功耗、速度等等方面都难以与ASIC竞争。

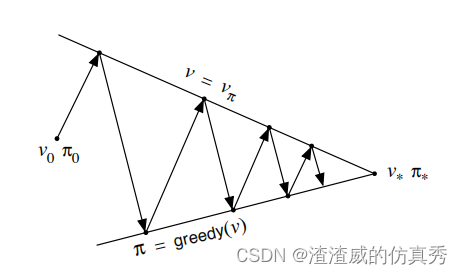

至于共通点,需要了解掌握FPGA应当具备以下能力:

1、需要有数字逻辑的设计思想 :针对任意一项具体的功能,如何组合你器件内的单元来实现,需要哪些单元?如何连接这些单元?各个单元之间连接的先后顺序如何?

2、一套从头到尾执行的设计环境(FPGA厂商提供的编译工具 - Lattice的Diamond、Intel的Quartus、Xilinx的Vivado)

3、一种连接你的逻辑思维和机器操作之间的沟通工具 - 设计语言(原理图、Verilog、VHDL等等)。 而设计思想和语言工具在ASIC上也是所必须的,说白了大家都要写Verilog,很多地方自然互通。

三、FPGA转IC前端的原因

并不是说FPGA必须转数字IC,这只是一个方向。

真正的原因是做RTL的工程师一定要往系统层面的工程师转,只在RTL和协议这条路上走下去,没有任何希望。

19年的Xilinx 开发者大会(XDF)之后,新的开发平台和自适应芯片降低了FPGA的使用门槛,将软硬件放在同一平台上开发,尽可能的使用高级软件语言(c++、python等)进行整体SOC的开发,这也是将来FPGA开发的趋势,让无论是否会HDL的人都能立马上手使用。

最开始从底层做起,慢慢的积累学习,最终能在SOC上实现软硬件的整体把控设计,才能在当前岗位上提升一个层面。

RTL出身的工程师,在这方面本身就具有一点点优势,而且从技术上来说,数字IC设计只会比FPGA更加复杂:

更快的时钟

更统一的coding style

更严格的STA

更系统的仿真

更低的功耗

更少的可用资源

至于UVM仿真,即便不做IC,传统的FPGA工程师也应该有所掌握,一个系统的仿真对产品的开发和后期维护,节省的时间不可估量。

FPGA受限于环境因素,ASIC/SOC一定是之后发展的大趋势。

如果愿意待在目前的舒适区,做个传统的FPGA工程师也没什么不好,但是想工作上有突破,就大胆迈向IC前端吧!

如果你还是不知道怎么选择岗位的话,不妨先跟行业的工程师了解一下岗位的学习难度,薪资,就业这些信息,再做抉择。

这里放个入口:IC入行指导

![[MySQL] MySQL库的基础操作](https://img-blog.csdnimg.cn/c461496986f64c47ba5b6d4abc970ac0.png)