一百二十三、计算机相关理论

123.1 计算机的组成

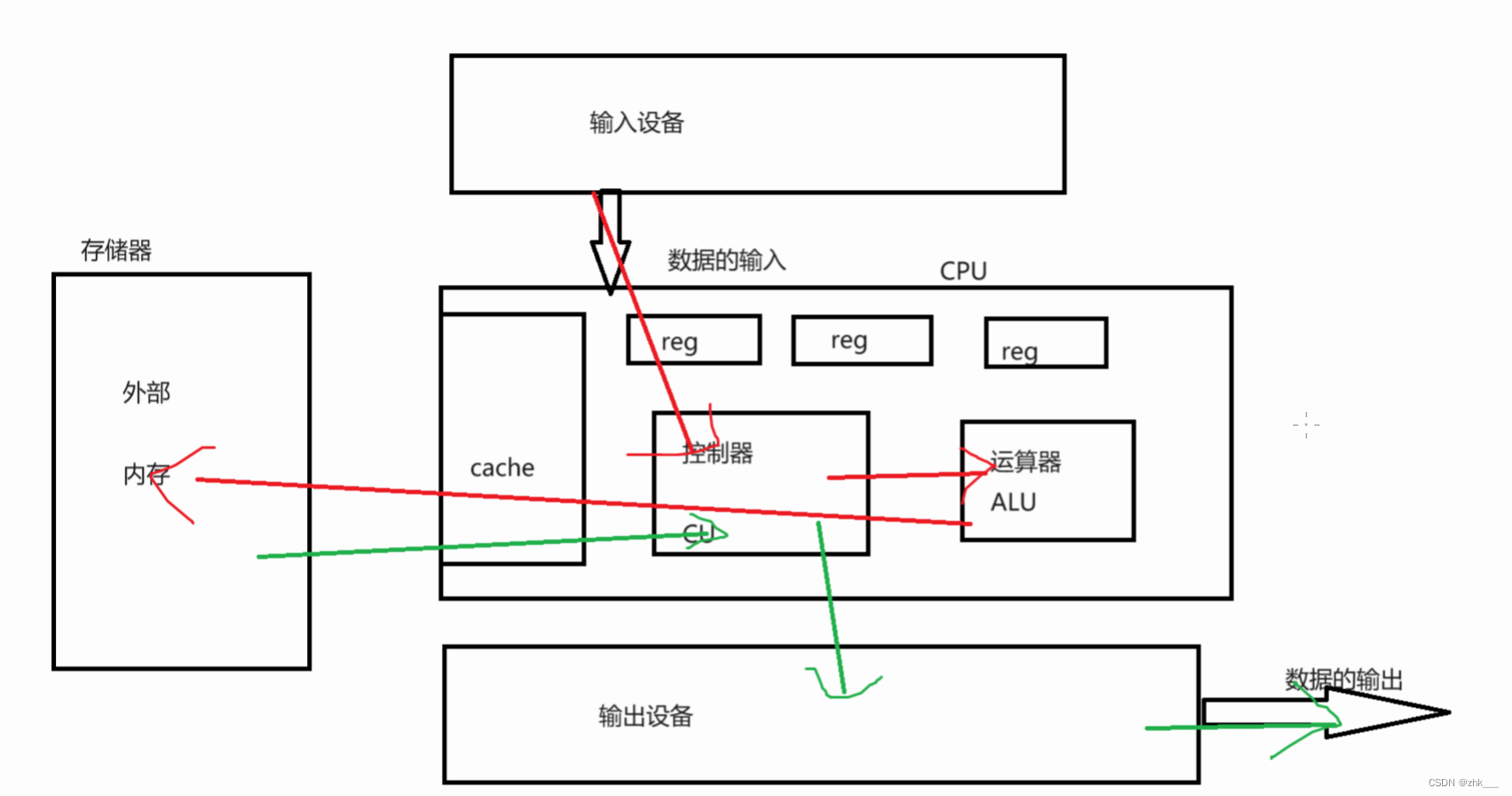

- 目前的计算机都还是 冯·诺依曼体系 ,也就是由:输入、输出、运算器、存储器、控制器,这个五个部分构成。

- 输入:Input,常见的输入设备,比如鼠标,键盘啥的

- 输出:Output,常见的输出设备,比如音响(喇叭),显示器啥的

- 运算器:ALU(Arithmetic Logical Unit),可以进行算术运算和逻辑运算,就是用来计算的

- 存储器:用来存放数据的东西,存储器的体系为金字塔型,越往下读写速率越慢,存储空间越大,每 bit 价格越便宜,从上往下依次是

- 最上面是 register(寄存器),

- 然后是 L1cache、L2cache、L3cache(一般是三级cache,有些体系的计算机可能会用两级cache,早期的计算机有些是没有cache,有些是一级cache)、

- main memory(主存,也被称为内存,就是内存条的那个内存)、

- Auxiliary storage(辅存,一般是外接的存储器,比如硬盘,之前还有磁盘、磁带、光盘啥的)

- 控制器:CU(Control Unit),其实就是个有限状态机,会根据每条指令的二进制代码,以及里面的状态码去分支执行不同的操作,这些都是逻辑门进行控制的。所以并没有啥译码功能,也就是根据传过来的不同指令去开不同的通道执行不同的功能罢了

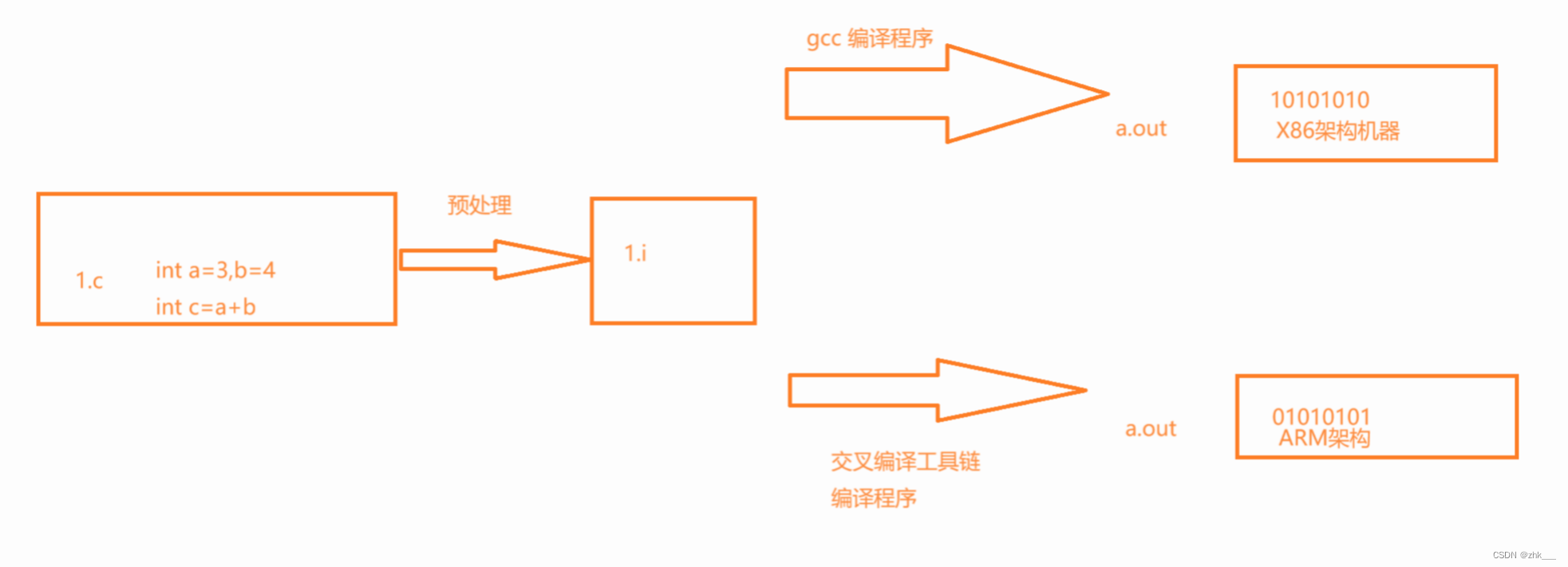

123.2 程序编译的过程

- 预处理,编译,汇编,链接

预处理:将程序中所有以#开头的内容展开到当前文件中 gcc -E 1.c -o 1.i 编译:检查语法错误,生成汇编程序 gcc -S 1.i -o 1.s 汇编:将汇编程序编译为二进制程序 gcc -c 1.s -o 1.o 链接:将程序中用到的一些库链接到程序中,生成二进制可执行文件 gcc 1.o -o a.out - 为啥需要编译:

- CPU只能识别二级制的0和1,但其实它0和1都不识别,只能识别高电位和低电位,因此具象为0和1。

- 想让CPU按照我们写的高级语言代码执行,那就需要将高级语言逐步转化为机器码,因此需要先生成汇编文件,然后根据汇编文件生成对应的二进制文件。

- 而不同体系的CPU的汇编代码也怎么一致,因为里面CPU的架构不一样。

123.3 指令与指令集

- 指令有机器指令和汇编指令之分,不同体系的CPU之间它们的风格和内容也不一样。

- 机器指令:由二进制0和1组成的代码,计算机可以通过0/1转换为的高电位低电位进行识别执行;RISC风格指令为定长的,CISC风格指令是变长的。

- 汇编指令:由机器指令进行符号化抽象的结果。机器码的0和1不方便人的记忆与操作,故符号化一下方便人的使用。

- 指令集:指令的集合,指令集中一般需要包含 运算类指令、程序流控制类指令、存储器访问类指令 这三种。

123.4 RISC(Reduced Instruction-Set Computer 精简指令集)和CISC(Complex Instruction Set Computer 复杂指令集)

123.4.1 RISC

- 简介:RISC的指令系统相对简单,它只要求硬件执行很有限且最常用的那部分指令,大部分复杂的操作则使用成熟的编译技术,由简单指令合成。目前在中高档服务器中普遍采用这一指令系统的CPU,特别是高档服务器全都采用RISC指令系统的CPU。

精简指令集是选取了一些比较简单、使用频率比较高的指令组成的指令集。 - 特点:

- 指令定长:即每条机器指令所占的 bit 长度固定。

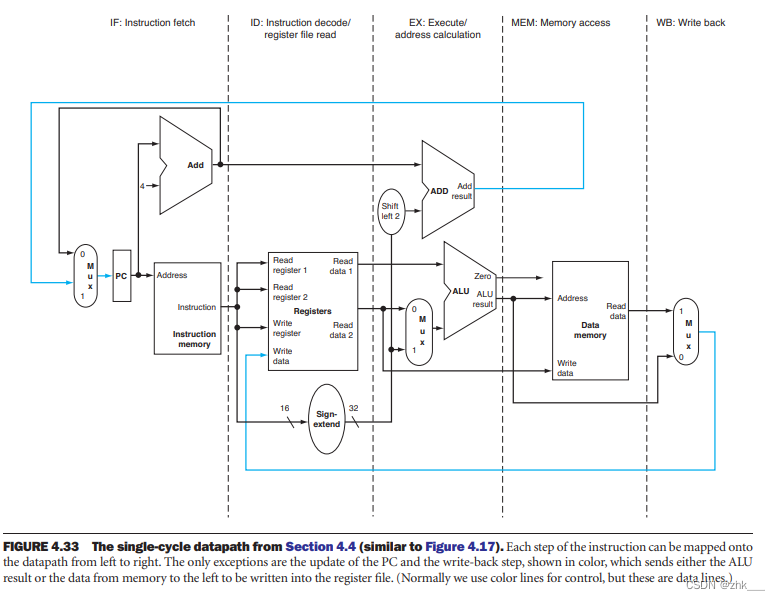

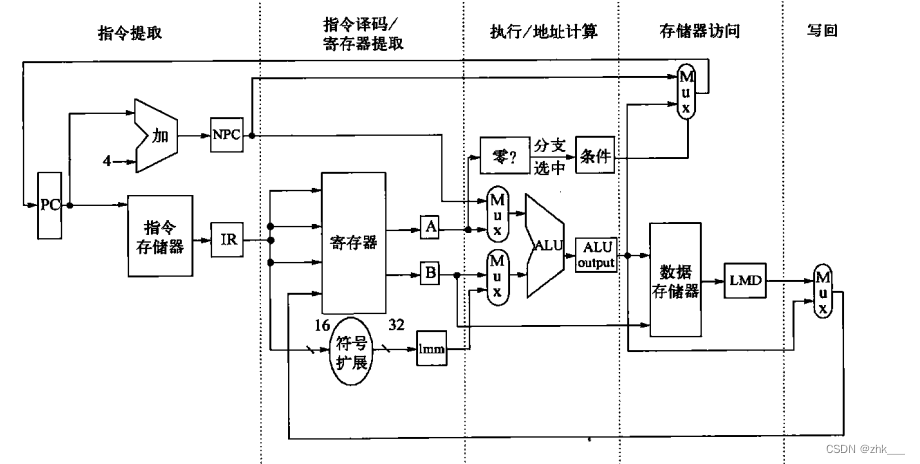

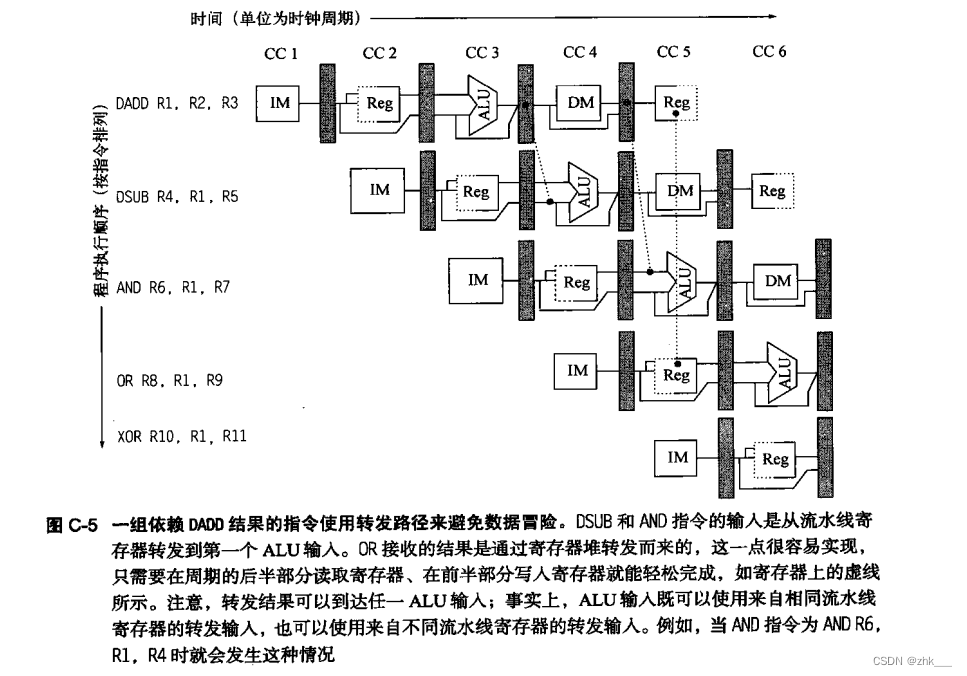

- 执行周期固定:一般是按照流水线的模式执行指令。比如 MIPS 的 五级流水线模型 为IF、ID、EX、MEM、WB,分别是 取指令、译码、执行、访问存储器、写回。有些指令可能不会执行某些周期,但是也要经过这一周期,就跟小学生排队打菜一样,一荤 一素 一米 一汤 一水果,这五个中某些可以不要,但是都要从前往后经过这些窗口。

- 基于精简指令集设计的CPU核心成本、功耗、体积更低,但是实现的功能也相对简单。

123.4.2 CISC

- 简介:在CISC微处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。其实它是英特尔生产的x86系列(也就是IA-32架构)CPU及其兼容CPU,如AMD、VIA的。即使是现在新起的X86-64(也被称为AMD64)都是属于CISC的范畴。

CISC早期的计算机部件比较昂贵,主频低,运算速度慢。为了提高运算速度,人们不得不将越来越多的复杂指令加入到指令系统中,以提高计算机的处理效率,这就逐步形成复杂指令集计算机体系。 - 特点:

- 指令长度不固定:比如说 x86 架构,最短的指令NOP,只有一个 byte,而最长的指令却足有 15byte。

- 执行周期不固定:每条指令中的各个操作也是按顺序串行执行的,因为最长的指令所需要的周期比较长,最短的比较短,所以就没有让二者看齐,不然会造成最长的指令没有执行完足够的功能,或者最短的指令浪费太久的时间。

- 复杂指令集设计的CPU核心实现的功能更为复杂,但是功耗、成本都会更高。

123.5 流水线模型

此处以MIPS的五级流水线为例

忽略第一个图里面说的单周期数据通路,多周期数据通路是在上面再接几根线,保证数据的读写不会错乱,就先不上图了

一百二十四、ARM相关内容

ARM的流水线更抽象,直接整合为三个阶段:取指令,译码,执行。执行里面包括了访问存储器和写回。。。只能说,挺无奈

124.1 ARM 发展史

直接上链接:ARM发展史

124.2 ARM架构

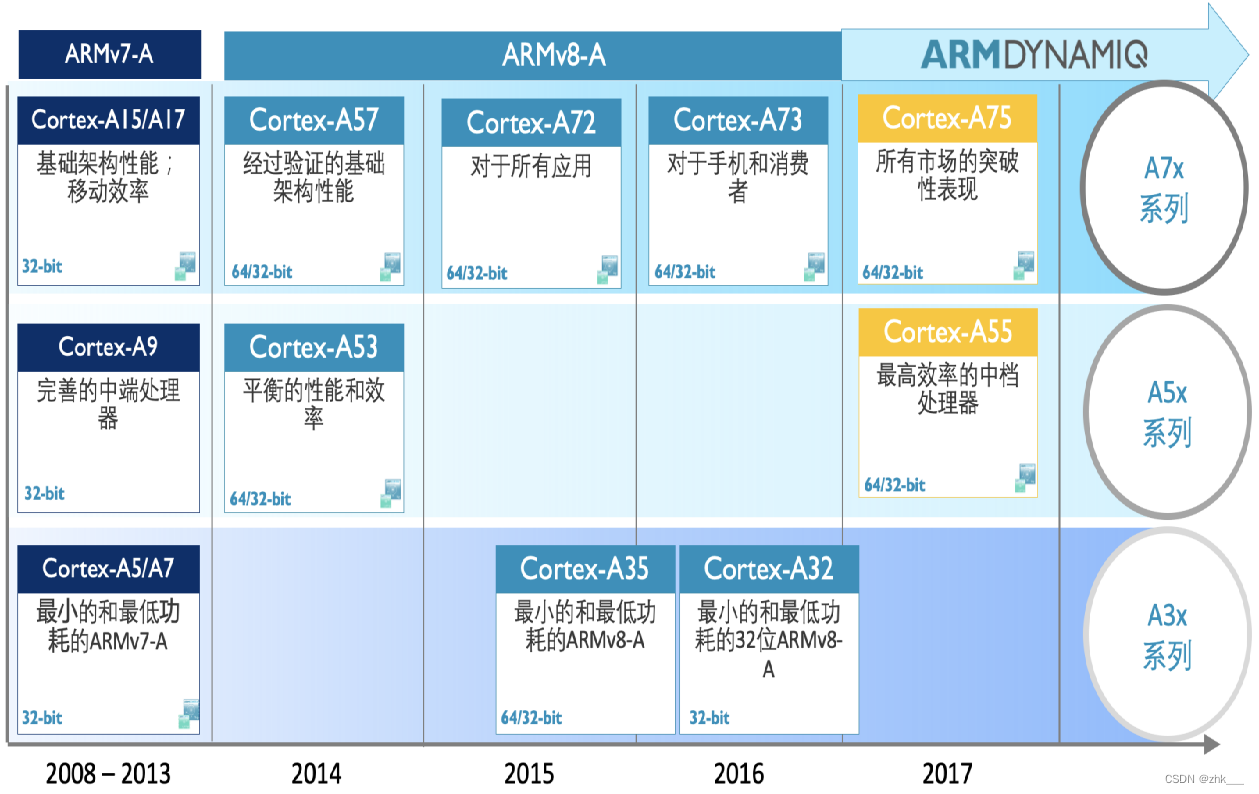

- 不同版本的指令集就是不同的架构

ARMV1-ARMV6:已经被淘汰

ARMV7架构:32位架构,支持32位指令集

ARMV8架构:64位架构,支持64位指令集,并且向下兼容32位指令

ARMV9架构:64位架构,支持64位指令集

124.3 ARM内核

- 基于不同的ARM架构设计出来的不同的处理器核心叫做不同的ARM内核

arm7/arm9/arm11

cortex-A7 ARMV7

cortex-A53 ARMV8

cortex-A55 ARMV8

cortex-A77 ARMV8

cortex-A78 ARMV8

cortex-x1 ARMV8

cortex-A710 ARMV9

cortex-A510 ARMV9

124.4 SOC(system on chip 片上系统)

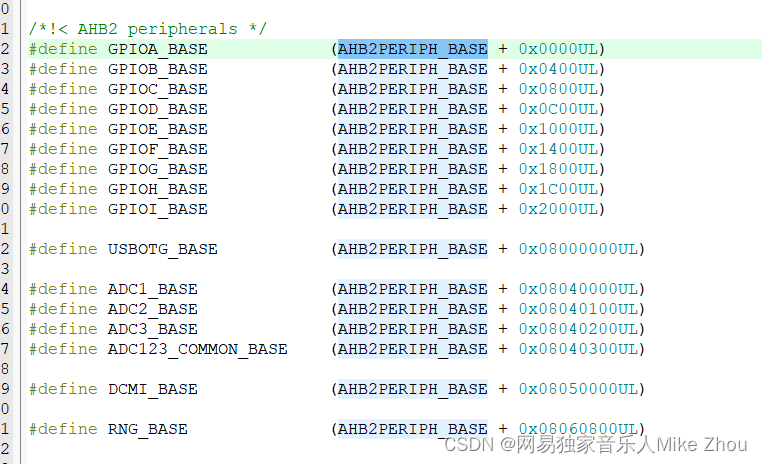

- ARM公司只进行技术授权。将自己的IP授权给各个半导体公司。半导体公司根据ARM的授权,在CPU核心外围设计了一些外围电路和设备,集成在一个芯片上,这个芯片就被成为SOC。

- SOC = CPU + 外设 + 总线

公司 SOC名称 内核 架构

ST STM32MP157A cortex-A7 ARMV7

三星 S5P6818 cortex-A53 ARMV8

海思 麒麟9000 cortex-A77 ARMV8

高通 骁龙888 cortex-x1 ARMV8

124.5 ARM的产品分步

124.5.1 Cortex-A系列

- Cortex-A 系列的核心是 ARM 处理器中性能最强的、最完善的处理器。属于高端处理器

- 在基于 Cortex-A 处理器为核心的开发板上可以搭载 linux / 鸿蒙 等标准化操作系统

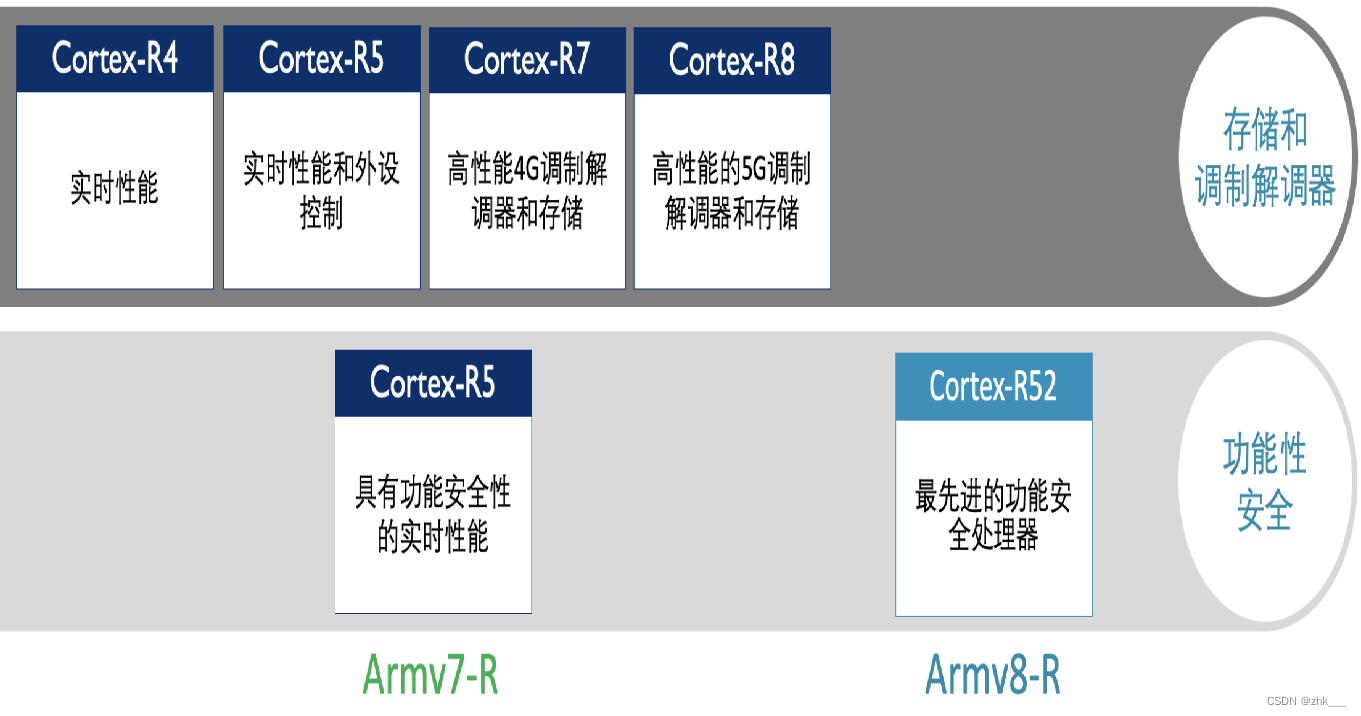

124.5.2 Cortex-R系列

- Cortex-R 系列处理器追求系统的实时性能。对数阶的实时性要求高的场景下使用 Cortex-R 系列处理器汽车、军工

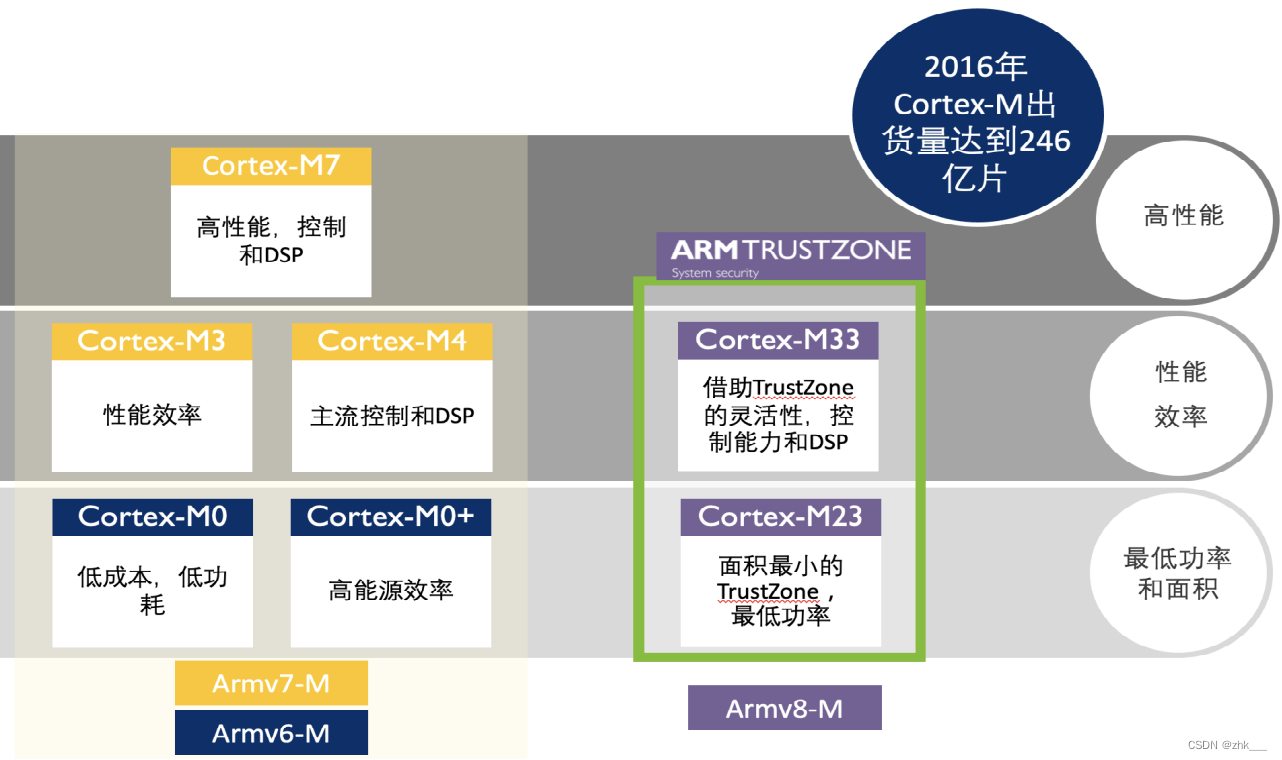

124.5.3 Cortex-M系列

- 属于 ARM 处理器中比较低端的芯片处理器,工作主频一般在 24M-256MHz 之间

- Cortex-M 系列处理器一般不跑操作系统,主要执行一些裸机程序

- Cortex-M 系列处理器可以搭载一些轻量级的实时系统 FreeRtos

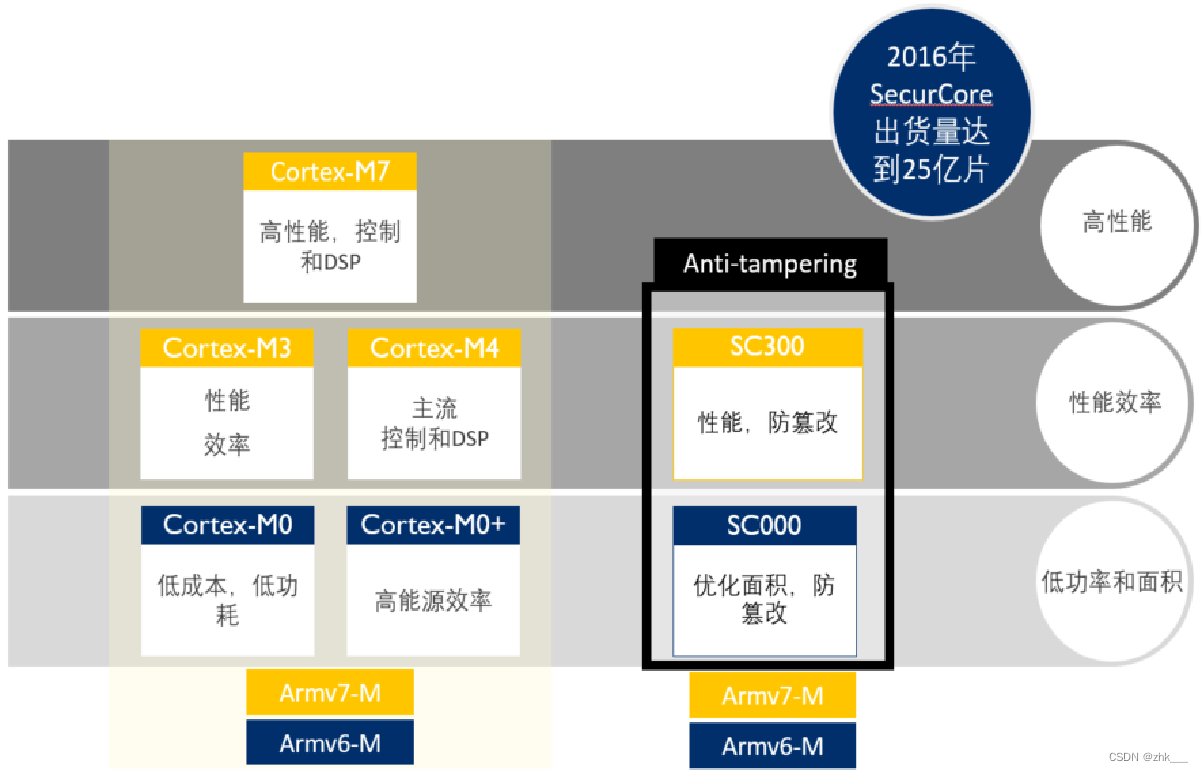

124.5.4 SecurCore系列

- 用于对安全性能要求比较高的场景

124.6 ARM数据约定

- 一些数据大小的表述

ARM 约定:

Byte 8 bits.

Halfword 16 bits.

Word 32 bits.

Doubleword 64 bits.

- 大部分ARM core 提供:

ARM 指令集(32-bit)

Thumb 指令集(16-bit ) - Cortex-A处理器

16位和32位Thumb-2指令集

16位和32位ThumbEE指令集

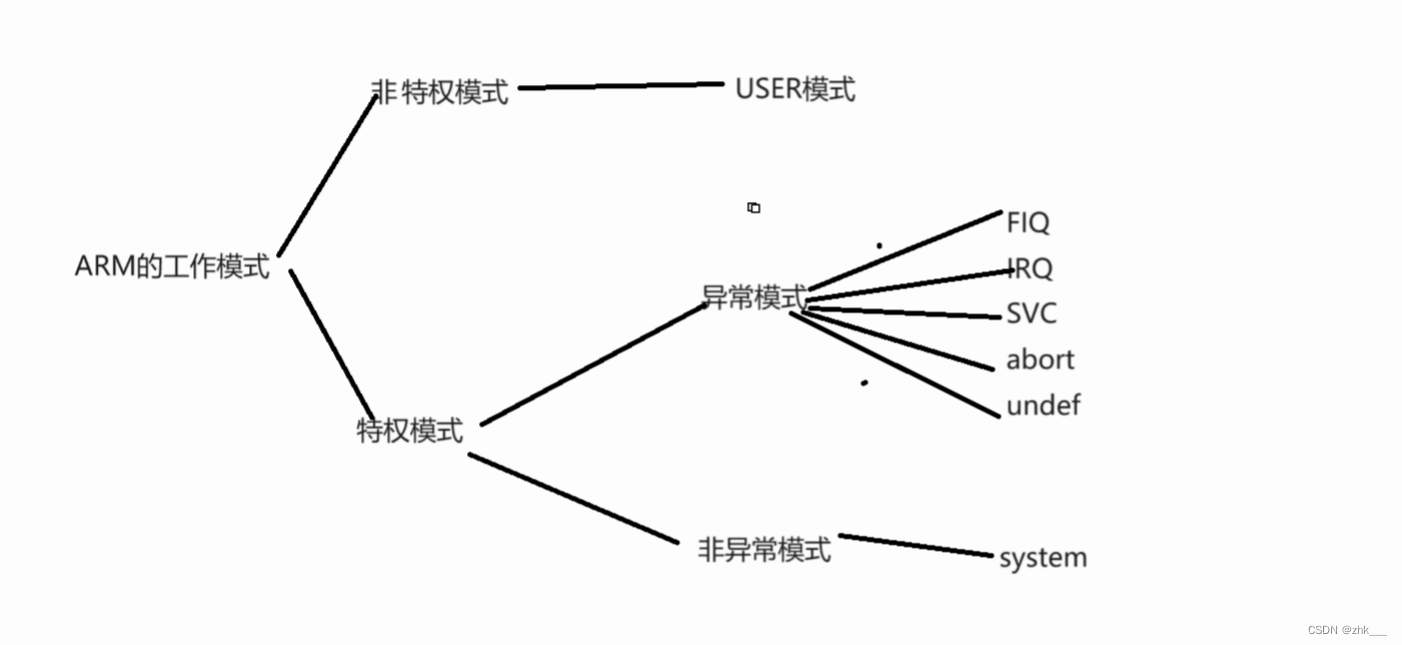

124.7 ARM的工作模式

- ARM 有7种基本工作模式:

User : 非特权模式,大部分任务执行在这种模式

FIQ : 当一个高优先级(fast) 中断产生时将会进入这种模式

IRQ : 当一个低优先级(normal) 中断产生时将会进入这种模式

Supervisor : 当复位或软中断指令执行时将会进入这种模式

Abort : 当存取异常时将会进入这种模式

Undef : 当执行未定义指令时会进入这种模式

System : 使用和User模式相同寄存器集的特权模式

- Cortex-A特有模式:

Monitor : 是为了安全而扩展出的用于执行安全监控代码的模式;也是一种特权模式。

HYP:虚拟化模式,当一个硬件上运行两种OS内核时进入这种模式。

124.8 存储器

124.8.1 存储器的金字塔模型

越往下读写速率越慢,存储空间越大,每 bit 价格越便宜,从上往下依次是,

- 最上面是 register(寄存器),

- 然后是 L1cache、L2cache、L3cache(一般是三级cache,有些体系的计算机可能会用两级cache,早期的计算机有些是没有cache,有些是一级cache)、

- main memory(主存,也被称为内存,就是内存条的那个内存)、

- Auxiliary storage(辅存,一般是外接的存储器,比如硬盘,之前还有磁盘、磁带、光盘啥的)

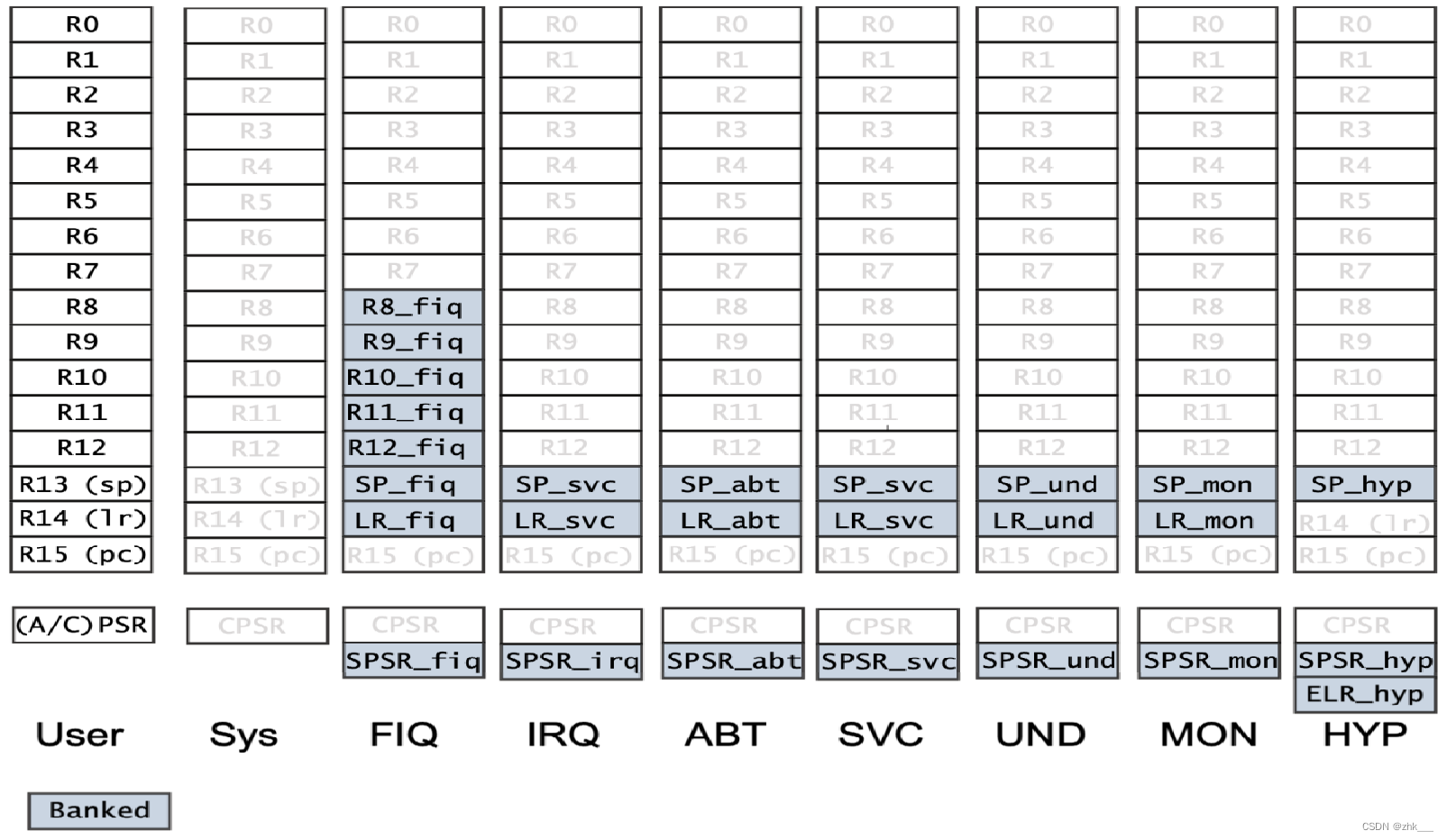

124.8.2 ARM v7架构下的寄存器组织

- ARM 有37个32-Bits长的寄存器:

1 个用作PC( program counter) 1个用作CPSR(current program status register) 5个用作SPSR(saved program status registers) 30 个通用寄存器 - Cortex体系结构下有40个32-Bits长的寄存器:

- Cortex-A多出3个寄存器

Monitor 模式 r13_mon , r14_mon, spsr_mon - 当前处理器的模式决定着哪组寄存器可操作.

- 任何模式都可以存取:

对应的R0-R12子集 对应的 R13 (the stack pointer, SP)、r14 (the link register, LR)、 R15 ( the program counter, PC) 对应的CPSR(current program status register, CPSR) - 特权模式 (除system模式) 还可以存取:

对应的 SPSR (saved program status register)

- 任何模式都可以存取:

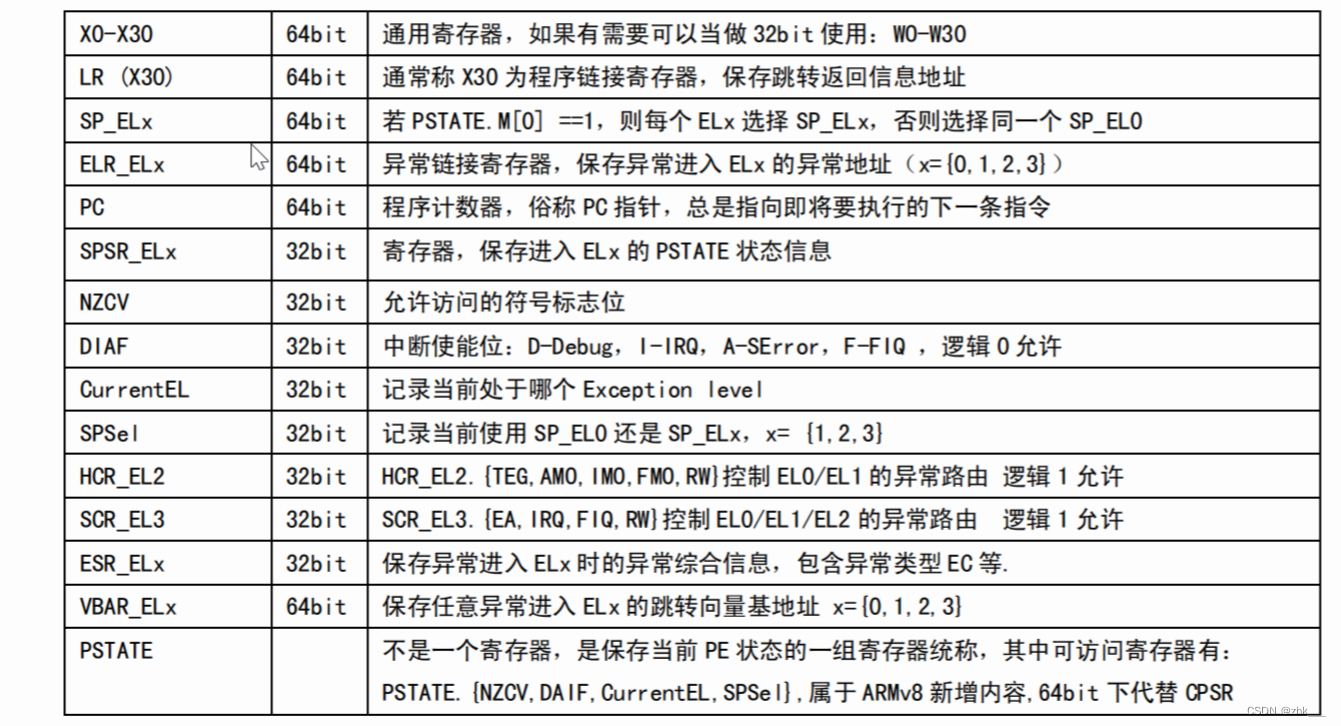

124.8.3 ARMV8架构寄存器组织

124.8.4 ARMV7架构下一些具有特定功能的寄存器

-

R13寄存器(the stack pointer, SP)

R13 寄存器又叫 SP(栈指针寄存器),这个寄存器内部保存栈顶的地址 一般在内存中分出一部分内存当作栈来使用,SP寄存器时钟保存栈顶空间的地址 栈一般存放一些临时数据,也可以用于保护现场 -

R14寄存器(the link register, LR)

R14寄存器又被称为链接寄存器,当程序在实现跳转的时候,LR寄存器中保存当前跳转指令下一条指令的地址。 方便实现程序的返回 程序的跳转实现: PC->跳转之后指令的地址 程序的返回: PC=LR -

r15寄存器(the program counter, PC)

R15 寄存器又被称为 PC 寄存器(程序计数器,或者指令指针) 这个寄存器始终保存马上要进行取址的指令的地址,当一条指令执行快结束之后PC寄存器的数值会自动向下+4 另外,在特定情况下可以手动修改PC的值进行程序的跳转 -

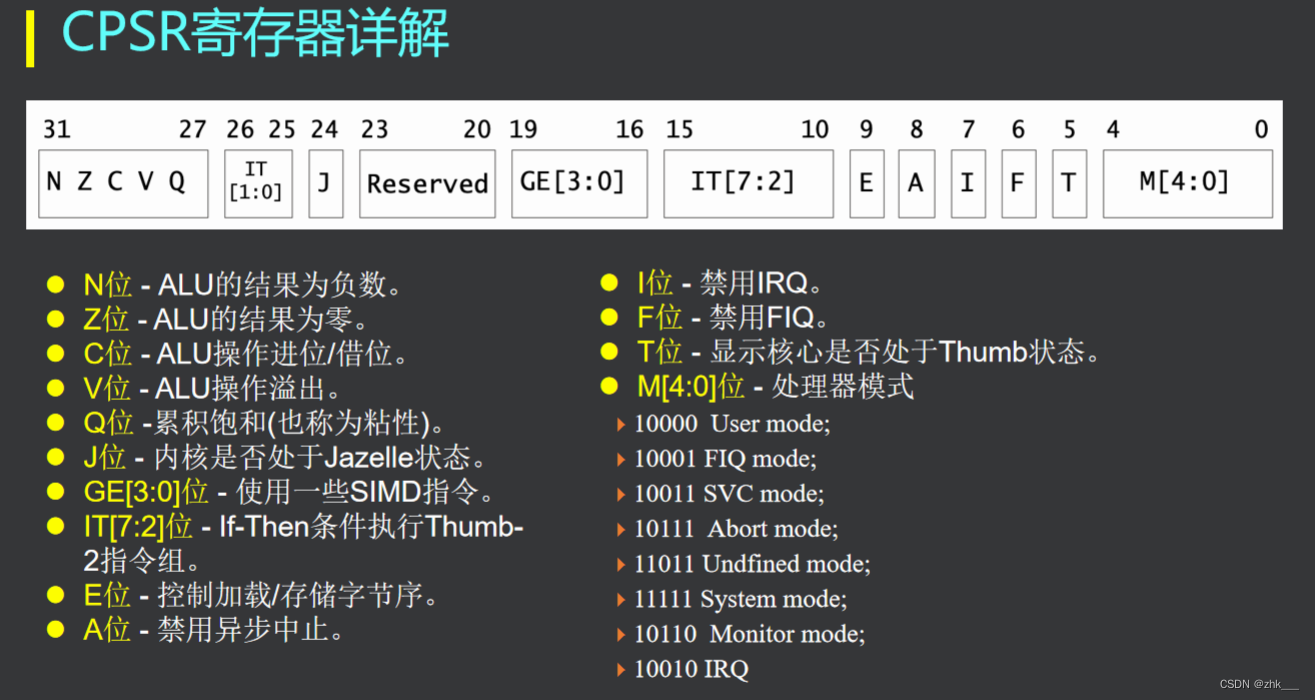

CPSR寄存器(current program status register, CPSR)

CPSR:程序状态寄存器 这个寄存器中保存当前程序的运行状态,比如工作模式等信息

-

SPSR寄存器(saved program status register)

SPSR寄存器可以用于保存程序某一时刻的状态 比如当发生异常之后,处理器的工作模式要切换到对应的异常模式去处理异常, 这样CPSR的数值会发生对应的改变 在处理完异常结束后,我们需要将CPSR的值修改为没有发送异常之前的状态, 这个时候就可以将SPSR保存的异常发送之前的状态赋值给CPSR