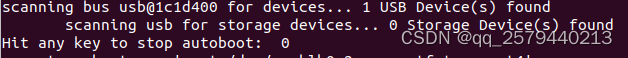

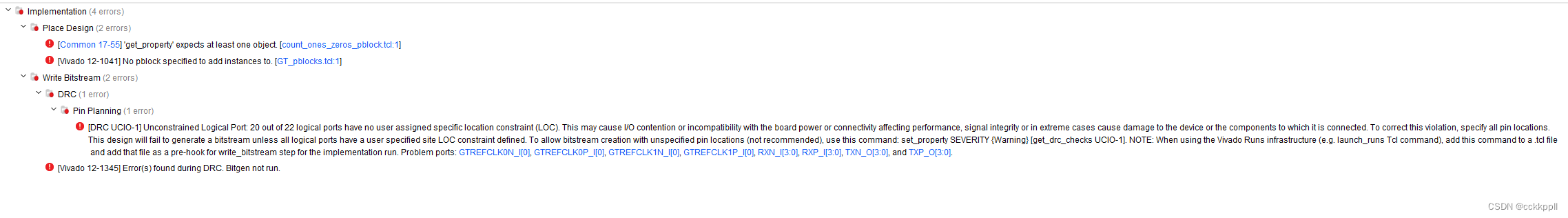

拿着开发板的例程,只修改了FPGA芯片,FPGA芯片是同一系列的。运行编译产生bit流出现如下错误

[DRC UCIO-1] Unconstrained Logical Port: 20 out of 22 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: GTREFCLK0N_I[0], GTREFCLK0P_I[0], GTREFCLK1N_I[0], GTREFCLK1P_I[0], RXN_I[3:0], RXP_I[3:0], TXN_O[3:0], and TXP_O[3:0].

问题分析:检查过引脚映射部分,确认都修改了的。设置“set_property SEVERITY {Warning} [get_drc_checks UCIO-1]”依然不行。

最后是将IP核重新在使用的FPGA下重新产生一遍解决。