1. 引言

RISC Zero zkVM为:

- 基于 FRI + PLONK 构建的

- 采用Von Neumann架构的

- ZK Machine

- 将RISC-V微控制器 具化为 某基于STARK的证明系统,的微架构和编码机制。

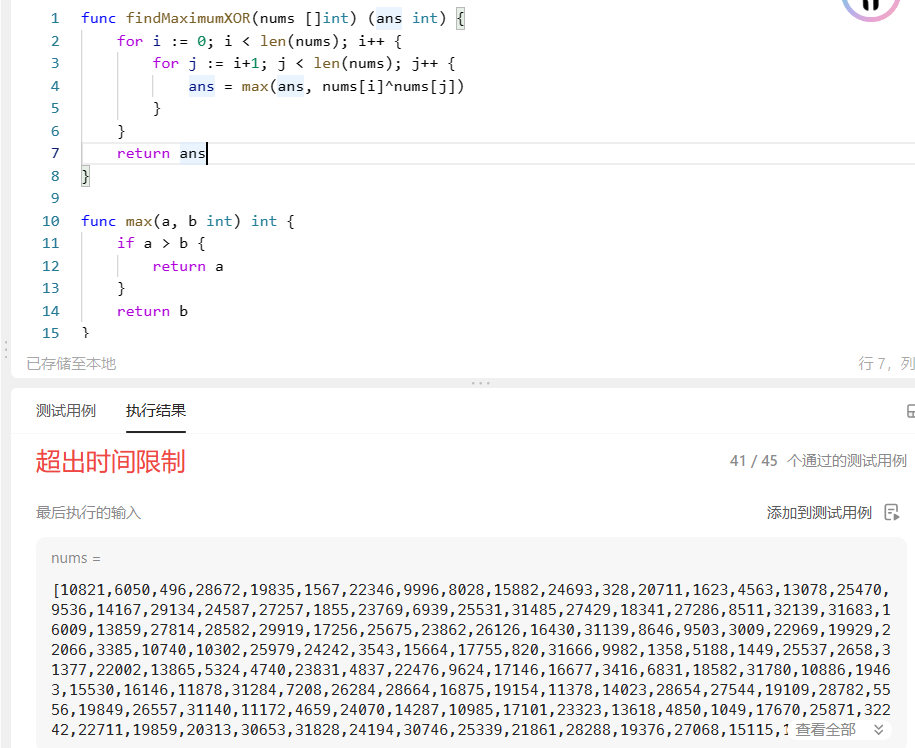

2. Row (Time) Structure

一个cycle对应1个memory transaction,对用户传入的程序elf可执行文件的处理流程为:

- 1)INIT:初始化阶段。有特殊的初始化cycle,用于重置状态。

- 2)LOAD:程序加载阶段。

- 高效加载特定elf程序的程序数据,到,emulated memory。

- 3)RESET:重置阶段。跳转program counter,到,程序初始执行位置。

- 4)RISC-V执行阶段:实际处理器用3个cycle来执行每条指令。【每个逻辑cycle对应一个memory transaction。】

- 4.1)DECODE:解码阶段。从内存加载每条指令进行解码。

- 4.2)COMPUTE:compute slash load阶段。从内存加载数据。

- 4.3)APPLY:更新寄存器值到内存。

- 5)FINISH:结束阶段。

3. Column Structure (Overall)

总体的column结构为:

总体分为3大类的列类型,每种列类型对应独立的Merkle tree:

- CONTROL列:也称为code列,用于表示对Prover和Verifier均已知的公开数据。实际上用于对control和各种flags进行编码。如:

- 以flags来表示其为初始化cycle、load cycle、execution的3 cycle structure。

- 实际会在这些列中存储待加载的elf数据。即程序默认是public input。Prover需知道整个program,而Verifier仅需知道该program的哈希值。

- 并将各种控制逻辑也写入这些列中。

- 对应一棵Control Merkle tree。

- DATA列:为private列。用于保存执行过程中的RISC-V状态。

- 对应一棵Main Data Merkle tree。

- ACCUM列:用于permutation等。

- 对应另一棵Merkle tree。

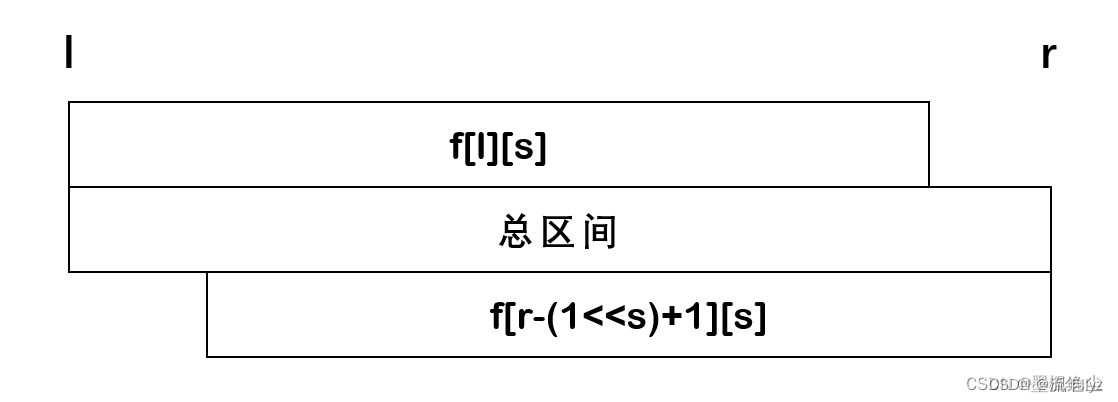

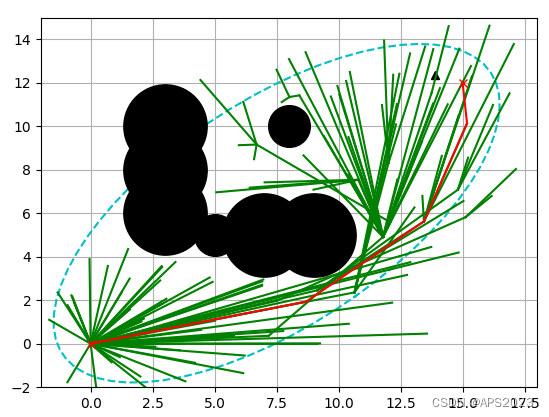

4. RISC Zero FRI Trace

即:

- 先按Addr升序排序

- 再按cycle升序排列

5. RISC Zero Host Interaction

参考资料

[1] RISC Zero团队2022年4月在ZK Summit 7 视频 RISC Zero Architecture Presentation @ Stanford - Jeremy Bruestle